FPGA跨时钟域处理方法(一)

描述

跨时钟域是FPGA设计中最容易出错的设计模块,而且一旦跨时钟域出现问题,定位排查会非常困难,因为跨时钟域问题一般是偶现的,而且除非是构造特殊用例一般的仿真是发现不了这类问题的。

优秀的FPGA工程,系统工程师一定会进行合理的时钟域划分,理想的情况是整个工程只有一个时钟,完全不考虑跨时钟域的问题,但是实际的工程中一般是不存在的,因此合理的跨时钟域设计是很有必要的。

单bit慢变信号跨时钟域方法:

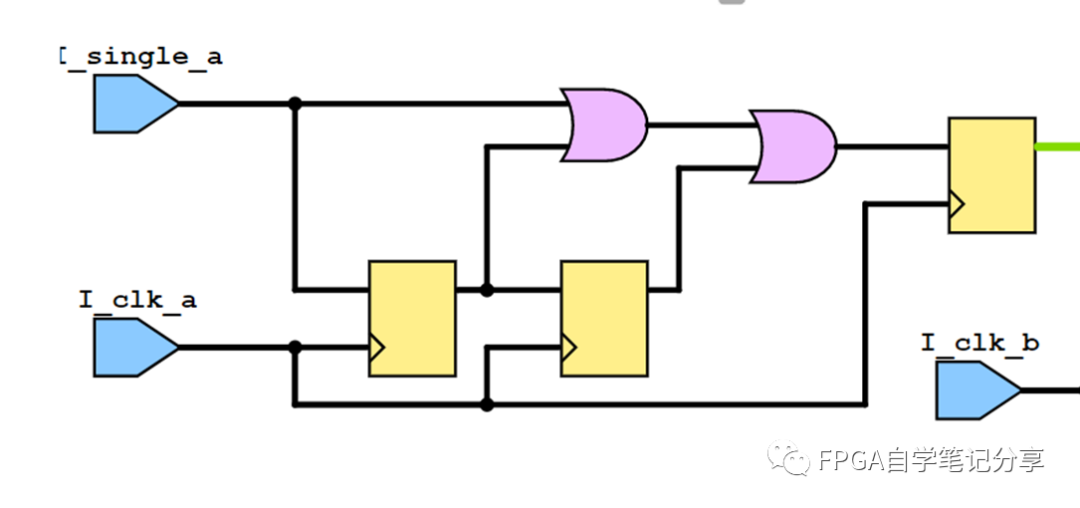

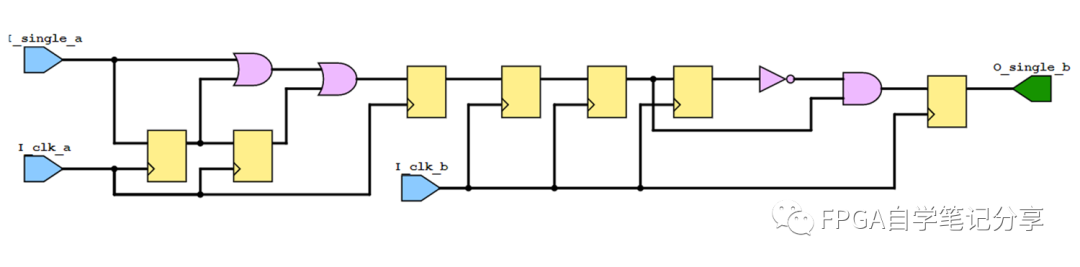

1、信号展宽

2、跨时钟打两拍

3、取沿

// ============================================================

// File Name: cm_cdc_1bit

// VERSION : V1.0

// DATA : 2022/9/28

// Author : FPGA干货分享

// ============================================================

// 功能:单bit慢变信号跨时钟域模块

// ============================================================

`timescale 1ns/1ps

module cm_cdc_1bit (

input wire I_clk_a , ///输入时钟a

input wire I_clk_b , ///输入时钟b

input wire I_single_a , ///a时钟输入信号

output reg O_single_b ///b时钟输出信号

);

// ============================================================

// wire reg

// ============================================================

reg S_clr_flag_a_d0 ;

reg S_clr_flag_a_d1 ;

reg S_clr_flag_a_all ;

reg S_clr_flag_b_d0 ;

reg S_clr_flag_b_d1 ;

reg S_clr_flag_b_d2 ;

reg S_clr_b_posedge ;

// ============================================================

// a时钟域

// ============================================================

always @(posedge I_clk_a)

begin

S_clr_flag_a_d0 <= I_single_a;

S_clr_flag_a_d1 <= S_clr_flag_a_d0;

end

///跨时钟域之前先扩展

always @(posedge I_clk_a)

S_clr_flag_a_all <= I_single_a|S_clr_flag_a_d0|S_clr_flag_a_d1 ;

// ============================================================

// b时钟域

// ============================================================

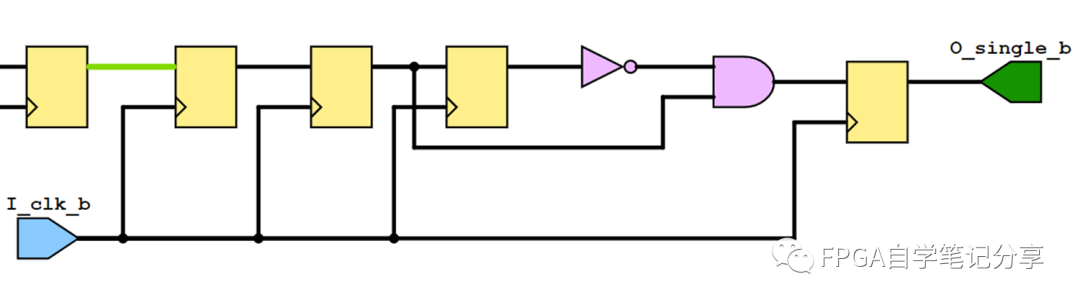

///使用第二个时钟进行打拍

always @(posedge I_clk_b)

begin

S_clr_flag_b_d0 <= S_clr_flag_a_all;

S_clr_flag_b_d1 <= S_clr_flag_b_d0 ;

S_clr_flag_b_d2 <= S_clr_flag_b_d1 ;

end

//打两拍之后的信号进行处理

always @(posedge I_clk_b)

O_single_b <= (!S_clr_flag_b_d2)&(S_clr_flag_b_d1);

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA跨时钟域处理方法(二)2023-05-25 1865

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2661

-

关于跨时钟域信号的处理方法2022-10-09 8545

-

SpinalHDL里用于跨时钟域处理的一些手段方法2022-07-11 3167

-

FPGA跨时钟域处理简介2022-02-23 1196

-

(10)FPGA跨时钟域处理2021-12-29 633

-

介绍3种方法跨时钟域处理方法2021-09-18 23583

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1717

-

FPGA初学者的必修课:FPGA跨时钟域处理3大方法2021-03-04 3939

-

三种跨时钟域处理的方法2021-01-08 2342

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 5265

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 2390

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2396

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14832

全部0条评论

快来发表一下你的评论吧 !