FPGA多bit跨时钟域之格雷码(一)

描述

FPGA多bit跨时钟域适合将计数器信号转换为格雷码。

格雷码的特点:从一个数变为相邻的一个数时,只有一个数据位发生跳变,

这种特点,就可以将跨时钟域中的多bit跨时钟域转换为单bit跨时钟域,最大限度的提高系统稳定性。

格雷码常用于通信,FIFO 或者 RAM 地址寻址计数器中。

格雷码编码

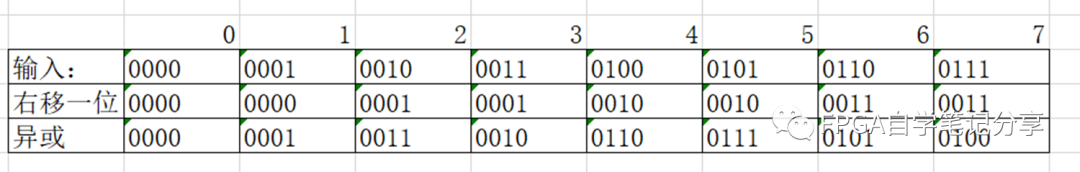

原码:b[0~n];格雷码:g0~n;编码:g=G(b);

编码:g=b XOR bi+1,g[n]=b[n];

最高位不变,其它位和高1位信号做异或

其代码如下:

//============================================================

// File Name: cm_bin2gray

// VERSION : V1.0

// DATA : 2022/10/2

// Author : FPGA干货分享

// ============================================================

// 功能:二级制编码转格雷码

//

// 原码:b[0~n];格雷码:g[0~n](n∈N);编码:g=G(b);解码:b=F(g);

// 编码:g=b XOR b[i+1](i∈N,0≤i≤n-1),g[n]=b[n];

// 解码:b[n]=g[n],b=g XOR b[i+1](i∈N,0≤i≤n-1).

//

// ============================================================

`timescale 1ns/1ps

module cm_bin2gray #(

parameter C_DATA_WIDTH = 4 )

(

input wire I_sys_clk , ///输入时钟

input wire [C_DATA_WIDTH-1:0] I_data_bin , ///输入二进制数据

output reg [C_DATA_WIDTH-1:0] O_data_gray ///输出二进制数据

);

// ============================================================

// main code

// ============================================================

always @(posedge I_sys_clk)

O_data_gray <= I_data_bin ^ (I_data_bin >> 1);

endmodule

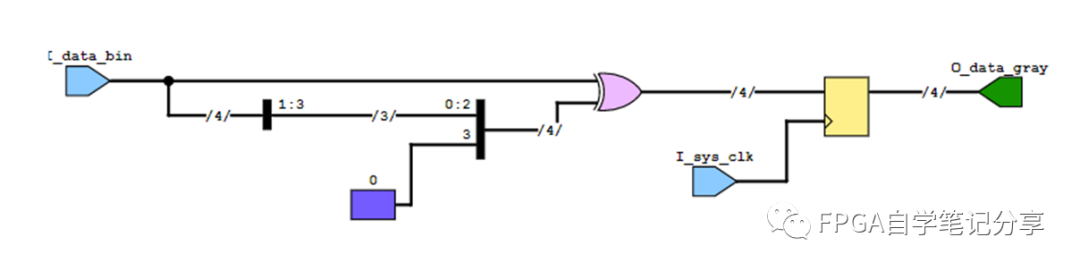

代码综合结果如下:

下一篇将介绍gray转二进制及其仿真

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA跨时钟域处理方法(一)2023-05-25 3209

-

揭秘FPGA跨时钟域处理的三大方法2022-12-05 2673

-

如何处理好FPGA设计中跨时钟域间的数据2021-07-29 1721

-

如何解决单bit和多bit跨时钟处理问题?2021-03-22 7776

-

FPGA初学者的必修课:FPGA跨时钟域处理3大方法2021-03-04 3942

-

三种FPGA界最常用的跨时钟域处理法式2021-02-21 4464

-

三种跨时钟域处理的方法2021-01-08 2346

-

FPGA设计中解决跨时钟域的三大方案2020-11-21 5277

-

探寻FPGA中三种跨时钟域处理方法2020-10-20 2392

-

如何处理好FPGA设计中跨时钟域问题?2020-09-22 2398

-

FPGA界最常用也最实用的3种跨时钟域处理的方法2017-11-15 14835

全部0条评论

快来发表一下你的评论吧 !