覆盖模型 – 填补内存VIP的漏洞

描述

正在寻找一种方法来减少在内存控制器/PHY 和子系统验证项目中定义和跟踪功能验证目标的工作量?

如果您尚未在内存项目中部署使用验证计划、功能和时序覆盖模型的最佳实践,请了解为什么建议这样做...

功能和时序覆盖闭合流程的关键属性

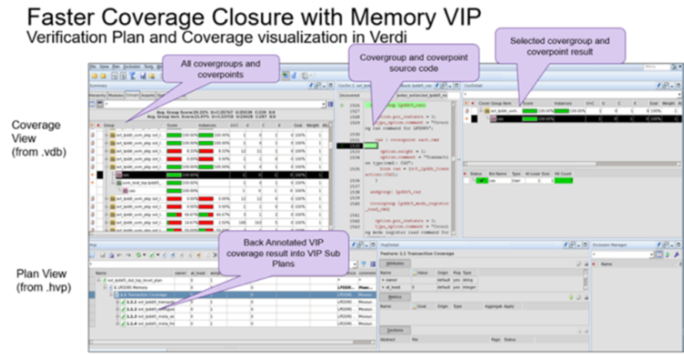

• 自动生成覆盖率报告,可灵活指定要启用

的不同类型的覆盖率 • 自动将覆盖率数据反向注释到测试计划中,确定覆盖目标

的进度 • 快速识别与未加密源代码相关的剩余覆盖点,实现更快的覆盖收敛

• 用户可以扩展内置覆盖范围,以根据内置的VIP采样事件和组添加自己的箱,或使用任何采样事件或数据

创建自己的组 •基于模拟器的覆盖实用程序(例如排除箱/覆盖点/覆盖组)可用于IP/子系统不支持的场景/设置Synopsys 内存模型 (VIP) 具有内置的验证计划、功能和定时覆盖模型,可加速覆盖收敛。提供覆盖模型是为了帮助跨配置设置、模式寄存器设置、功能和时序参数的多种组合运行完整的验证方案。

Synopsys Memory VIP 支持来自 JEDEC、ONFi、SD 和 SPI(DDR5、LPDDR5、DFI 5.0、HBM3、GDDR6 和 NVDIMM-P/N)等标准组织的最新批准和草案规范,以及与 VCS 和 Verdi 的原生集成和优化。

覆盖模型实现基于 System Verilog 构造(覆盖组、覆盖点、箱、非法箱),它是“协议规范版本感知”,这意味着如果不适用于配置的协议规范版本,则忽略覆盖点/箱。

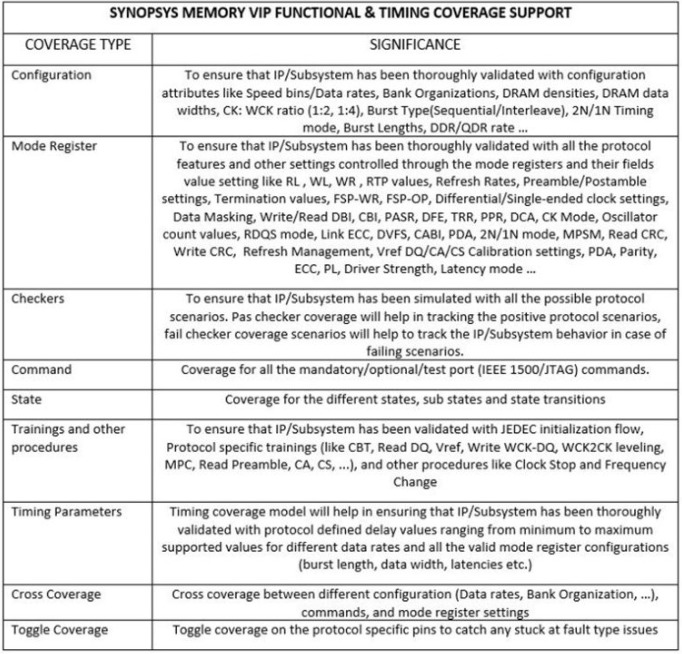

新思科技内存VIP覆盖模式包括:

·验证计划 - 验证计划显示每个功能覆盖组如何直接映射到协议规范方案。验证计划是分层的,子计划基于不同类型的覆盖范围。

• 功能覆盖模型 – 功能覆盖支持包括配置、模式寄存器、检查、命令、状态、训练、定时参数、切换以及有效的交叉覆盖。

• 定时覆盖模型 – 定时覆盖支持包括命令到命令延迟、掉电时间、自刷新时间、建立/保持,以及不同数据速率和所有有效模式寄存器配置(突发长度、数据宽度、延迟等)的交叉覆盖。

审核编辑:郭婷

-

curl中的TFTP实现:整数下溢导致堆内存越界读取漏洞2026-02-19 1322

-

物理内存模型的演变2024-02-25 1356

-

如何消除内存安全漏洞2023-12-12 2328

-

jvm内存模型和内存结构2023-12-05 1764

-

求解大型COMSOL模型需要多少内存?2023-10-29 3783

-

DDR VIP模型的无缝快速初始化2023-05-29 2907

-

使用内存VIP检测和避免内存瓶颈2023-05-26 2120

-

RT1060注册内存被TFLite Micro模型中的其他函数覆盖了怎么解决?2023-04-20 665

-

Rust语言助力Android内存安全漏洞大幅减少2022-12-06 1007

-

史上最难注册成为VIP的APP2016-09-12 7227

-

全球通VIP俱乐部建设2009-08-05 933

-

WCDMA室内覆盖规划研究 填补建筑物内盲区2009-05-21 561

全部0条评论

快来发表一下你的评论吧 !