使用经过验证的CXL IDE构建安全芯片

描述

欢迎来到安全流量的美妙而神秘的世界,CXL 是采用它的最新规范。随着对高性能数据中心的攻击变得越来越复杂,安全标准必须不断适应,以更好地保护敏感数据和通信,并最终保护我们的互联世界。为此,CXL 标准组织在 CXL 2.0 规范中添加了完整性和数据加密 (IDE) 的安全要求。

CXL 2.0规范为 CXL.io 和CXL.cache/CXL.mem协议引入了IDE原理图。CXL.io 途径使用 PCIe 规范定义的 IDE,而 CXL.cache/CXL.mem 相关更新在 CXL 2.0 规范中引入。在本博客中,我们将概述安全设置的外观以及 CXL 采用的安全策略。

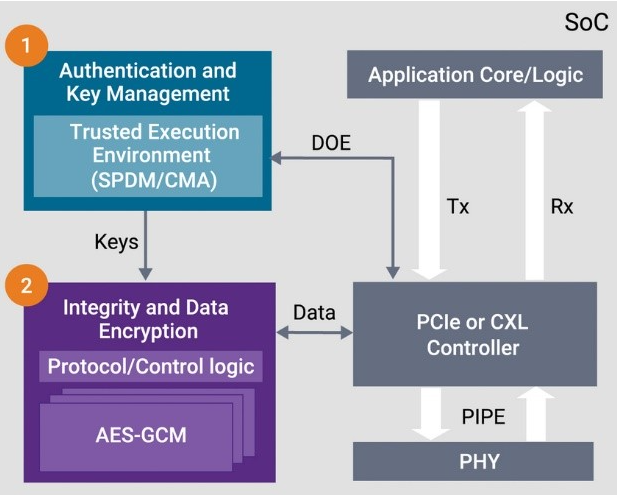

CXL IDE 可用于使用 TEE(可信执行环境)保护流量。TEE是一个隔离和安全的环境,用于存储和处理敏感数据。TEE 对 IDE 执行身份验证和密钥管理。

IDE 为 CXL.io 的事务层数据包 (TLP) 和 CXL.cache/CXL.mem 协议的数据链路层协议 Flits 提供机密性、完整性和重放保护,确保网络上的数据不受数据包的观察、篡改、删除、插入和重放。CXL.io 和CXL.cache/mem IDE都基于AES-GCM加密算法,并从身份验证和密钥管理安全组件(包括TEE)接收密钥。

使用 TEE 时,CXL IDE 通过使用对称加密密钥(CXL 为 AES GCM 选择 256 位密钥长度)来保护物理链路上两个设备之间交换的事务(数据和元数据)。

TEE 中的每个安全组件都实现一个 TCB(可信计算库),该库具有针对硬件、固件、软件以及用于实施安全策略的任意组合的保护机制。对于 CXL,TCB 包括:

实现加密算法的硬件块

配置加密引擎的模块(用于 CXL 的 AES-GCM,在即将发布的博客中详细介绍)

与上述两个块直接或间接通信的任何其他块

Synopsys 最近宣布推出业界首款安全模块,用于保护使用 CXL 2.0 协议的高性能计算 SoC 中的数据。适用于 CXL 2.0 的 DesignWare® IDE 安全模块 IP 已在超大规模云提供商处部署。强大的 IDE 安全模块使设计人员能够更快、更轻松地防止链路上的数据篡改和物理攻击,同时遵守最新版本的互连协议。IDE 安全模块使用 DesignWare 控制器 IP for CXL 进行设计和验证,可加快 SoC 的上市时间,同时提供适应设计特定用例所需的可配置性。

验证 IDE 功能的互操作性

为了验证 IDE 功能的互操作性,Synopsys VIP 支持 CXL.cache-mem IDE 开箱即用,如 CXL 11.2 规范第 0 章和 IDE 链路建立中所述。VIP 具有各种控件,允许用户调整 VIP 行为的功能,例如:

TX 和 RX 键编程(包括运行时键刷新)

TX 和 RX 截断延迟

带/不带PCRC的密闭和撬块聚合模式

密钥刷新时间

安全的<>不安全的流程

用于 Rx 错误状态寄存器验证的错误插入功能

CXL 缓存/内存 IDE 合规性测试,用于 CXL 设备 DUT 的互操作性测试。

特定于 IDE 的调试和日志记录

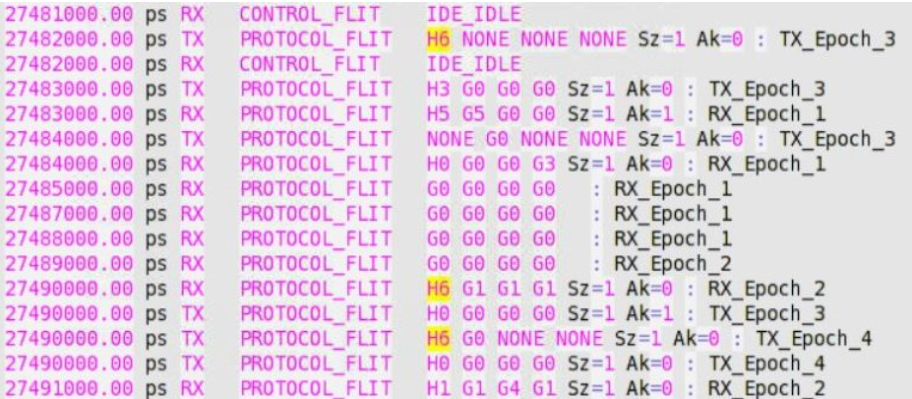

AES-GCM加密引擎需要3个输入(AAD,P,PText),这是加密引擎的VIPsTX和RX路径输出的片段。以下是示例流量和 MAC 的 IDE 特定 Flit 格式 (H6) 的代码段。

AES GCM 数据流:

H6 闪光:

审核编辑:郭婷

-

如何构建安全的IIoT设备2021-01-07 2432

-

如何构建安全的物联网架构2021-11-03 2136

-

一窥CXL协议2022-09-09 4523

-

虹科电子和IoT Inspector合作构建安全的物联世界2022-04-12 2500

-

数字孪生智慧加油站,构建安全防护网2022-11-03 1820

-

使用OseppBlock IDE构建代码2022-11-04 604

-

构建安全原封不动的门铃2022-11-24 778

-

邀请函 | 护航数字化校园,构建安全根基座2023-05-16 913

-

构建安全可信的数字世界2023-06-28 1656

-

澜起科技MXC芯片成功通过CXL联盟组织的CXL1.1合规测试2023-08-18 2261

-

亚马逊云科技助力vivo构建安全可信的“数字世界”2023-09-25 930

-

三星携手红帽成功构建全球首个CXL认证基础设施2024-06-25 1756

-

澜起科技CXL®内存扩展控制器芯片通过CXL 2.0合规性测试2025-01-21 2134

-

京准电钟守护时钟防线:北斗网络授时服务器构建安全堡垒2025-03-24 978

-

使用OpenUSD与NVIDIA Halos构建安全物理AI系统2025-12-24 1092

全部0条评论

快来发表一下你的评论吧 !