使用Synopsys协议连续体满足计算高速链路设计的异构验证和确认要求

描述

数据是推动云/边缘计算关键用例和人工智能进步的新燃料。数据处理的各个方面(收集、存储、移动、处理和分散)都带来了独特的设计实现和验证挑战。对异构计算的需求使特定于应用程序的加速器呈指数级增长,推动行业提出高效数据处理和资源利用的解决方案。CXL 是一种处理器互连协议,旨在支持从 CPU 到工作负载加速器的高带宽、低延迟接口,在异构设备之间保持内存一致性,同时满足用户的安全需求。

围绕 CXL 系统的验证和确认挑战

CXL 标准混合了外设互连、内存、一致性和安全域。以下是验证 CXL 系统时要考虑的要点。

需要系统级合规性 – 由于它是一个新兴标准,具有来自多个供应商的异构组件,因此必须遵守所有系统组件才能使设置正常运行。

硅前的系统级覆盖 – CXL 重用具有特殊处理(CXL 缓存/内存语义)的 Gen5 基础架构,用于 CPU-设备对的上游-下游内存访问,从而需要涵盖系统设置中的实际内存一致性方案。

硅后验证左移 – 准备在硅后生产有限的主板和硬件设备,缩小了硅后验证的范围。早期使用真实硬件设备的硅前到硅后理智对于避免硅重新旋转至关重要

新思科技优势

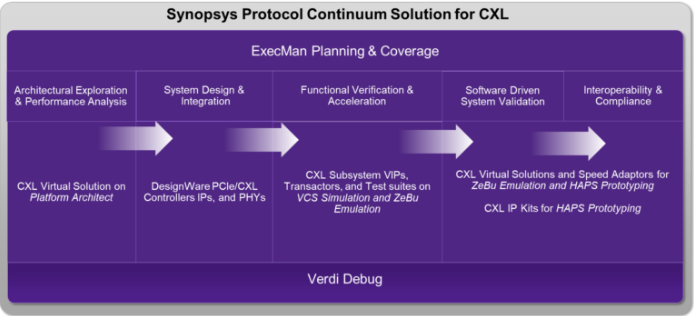

领域专业知识的融合是实现 CXL 系统的关键,Synopsys 利用数十年的专业知识为其用户提供全面的产品,支持开发基于 CXL 的设计。Synopsys 的 CXL 协议连续体是一个全面而完整的解决方案,涵盖架构探索、系统设计和实施、功能验证和加速、软件开发、系统验证、合规性测试和完整系统的互操作性。

Synopsys 积极参与 CXL 联盟,并且一直是推动采用、贡献 CXL 标准以实现各种基于系统的应用程序以及在我们的连续统一体解决方案上对最新的 CXL-CV 合规性测试进行早期测试的主要合作伙伴。Synopsys 是 DesignWare CXL IP 和 PHY 的领先提供商,包括符合定义的 CXL 2.0 IDE 规范的 CXL 2.0 完整性和数据加密 (IDE) 安全 IP 模块。

我们在协议验证解决方案中的产品与其他 Synopsys 验证技术原生集成,包括使用威尔第进行全面调试、使用 VC 执行管理器(“ExecMan”)进行回归管理和自动化。

审核编辑:郭婷

-

如何计算高速RS485收发器的功耗?2023-10-31 2637

-

如何计算高速RS-485收发器的功率损耗2023-08-24 1374

-

计算高速链路的系统注意事项2023-04-23 1302

-

计算高速链路互连内存和GPU以实现高性能2022-10-24 1173

-

SK hynix公司使用是德科技PCIe测试解决方案验证计算快速链路技术2022-04-24 1964

-

高速时钟线,多少M的算高速?2020-08-17 1809

-

基于AD9361和SIMULINK通信链路快速验证开发平台2019-02-19 2576

-

时钟抖动对高速链路性能的影响2018-09-19 2356

-

基于FPGA的EtherCAT链路冗余原理及其设计与验证2017-11-15 9729

-

计算高度密集型应用在异构多核DSP上的运行方法研究2017-10-19 711

-

AD9361+SIMULINK通信链路快速验证开发2016-11-25 3958

-

数据链路协议,数据链路协议是什么意思2010-03-18 813

-

链路状态协议2009-06-09 1698

全部0条评论

快来发表一下你的评论吧 !