256Gb/s就绪套装:PCIe Gen6验证IP

描述

Synopsys 业界首个 PCIe Gen6 VIP 可用性为行业领导者在验证基于 PCIe Gen6 的设计方面提供了先机优势,并以可预测的质量满足上市时间要求。由于 PCIe Gen6 是过去十年中对 PCIe 规范最重要和最具破坏性的更新,因此尽早开始验证并利用 Synopsys PCIe Gen6 VIP 来处理不断增加的验证复杂性,并通过 PCIe VIP 源代码测试套件确保与前几代产品的向后兼容性至关重要且具有优势。

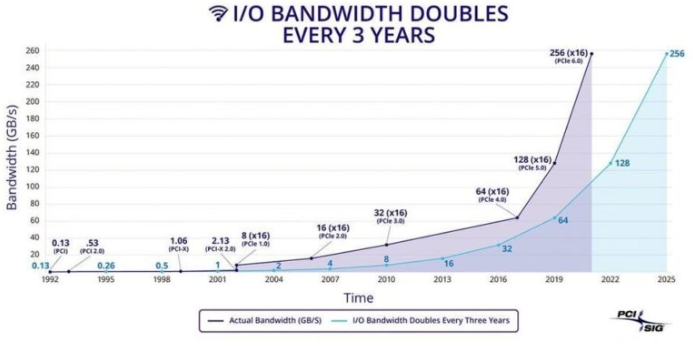

让我们看一下推动对 PCIe Gen6 标准的需求并实现更高带宽和 I/O 性能的一些向量。根据PCI-SIG的数据,I/O带宽每三年翻一番,PCI Express协议是一代又一代设计更高容量系统的关键推动因素。

AI、ML 和自动驾驶等新兴应用的数据量非常大。应用程序性能和结果质量在很大程度上取决于数据的丰富性和计算基础架构的性能。PCIe Gen6 提供可扩展的速度升级,以满足由专用 CPU 和 GPU 高效处理的这些繁重工作负载的更高数据吞吐量要求。

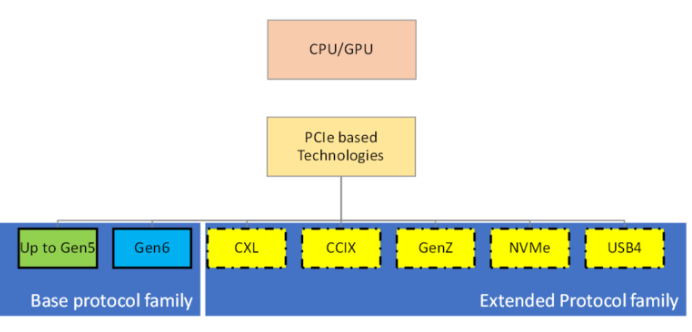

此外,不断提高的性能要求推动了边缘和分布式计算等不同方法。PCIe Gen6 和其他基于 PCI Express 的高性能互连标准(如 CXL)支持设计可扩展的分布式和互连系统。虽然 PCIe Gen6 是过去十年中最重要和最具破坏性的更新,但它仍然向后兼容,因此能够以经济高效的方式逐步构建新基础设施。

有一些服务器存储技术广泛使用PCI Express。高 I/O 吞吐量存储(如 NVMe 和 SSD 设备)通过即时访问 HPC 节点来虚拟本地化数据,并在 PCI Express 和以太网协议的帮助下保持流速率。因此,PCIe 提供的速度提升将显着改善整个基础设施的功能。PCIe Gen6规范的颠覆性将为NVMe,SSD和其他基于PCIe的存储技术带来新的验证挑战。Synopsys PCIe Gen6 VIP 和源代码测试套件将帮助您成功应对这些挑战。

突出特点一览

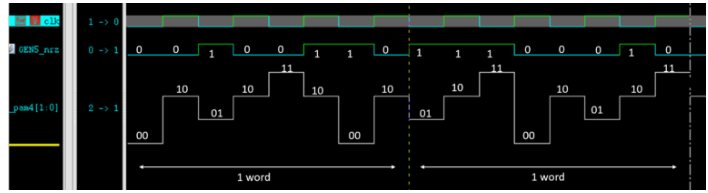

双带宽,带脉冲幅度调制

PAM4 的 4 个信号电平有助于传输两倍于 NRZ 的数据,而无需将 PCIe 6.0 的传输带宽加倍

为什么要使用前向纠错 (FEC)?

PAM4信号本质上是脆弱的,可以通过使用前向纠错方法进行补偿。这是通过牢记数据完整性至关重要而引入的。因此,将提供源源不断的纠错数据流,以确保我们不会在重新传输数据时浪费时间。它将确保低延迟和带宽效率。

为什么选择基于 Flit 的编码?

由于FEC可用于固定大小的代码字,因此引入了长度为256字节的Flits,它将用于通过链路传输TLP和DLLP。STP和SDP的成帧令牌将被移除,以提高带宽效率。纠错码 (ECC) 字节将作为 flit 的一部分进行传输,它们将负责保护整个 flit,包括 CRC(用于保护 TLP 和 DLLP 字节)。将删除同步标头以减少 flit 的开销。

审核编辑:郭婷

-

瑞萨电子推出符合PCIe Gen6标准的时钟缓冲器和多路复用器2022-04-14 3209

-

SSD 545S 256gb只在中国生产吗?2018-10-30 1534

-

PCIe Gen-3高速前端卡参考设计2022-09-21 1474

-

小米MIX皇帝版开箱!256GB!2017-02-24 3012

-

vivo Y93s已正式开售标配128GB闪存三卡槽设计最高支持256GB闪存拓展2018-12-11 10087

-

Patriot上市新产品 容量从256GB到1TB2020-03-03 1093

-

三星Galaxy S20FE海外推出256GB版本2020-11-09 4044

-

瑞萨电子推符合PCIe Gen6时钟缓冲器和多路复用器2022-04-15 2415

-

华为p50pocket价格官网报价256GB 售价8988元起2022-07-04 4407

-

戴尔Emulex EMC的XtremIO数组GEN6光纤通道2023-08-30 608

-

Astera Labs展示PCIe 6.0连接,带宽翻倍至256GB/sec2024-03-28 1875

-

新思科技PCIe 7.0验证IP(VIP)的特性2024-07-24 2636

-

美光研发出世界首款PCIe Gen6 SSD2024-08-07 2245

-

PCIe Gen6典型应用平台与差分晶体振荡器参数对照2025-06-27 2185

-

PCIe Gen5/Gen6 信号传输可以用极细同轴线束吗?2025-10-27 2821

全部0条评论

快来发表一下你的评论吧 !