CXL设备类型简介

描述

计算高速链路 (CXL) 是高带宽设备互连技术的最新规范。它提供从 CPU 到高性能计算平台其他组件的高速、高效连接。

CXL 在主机 CPU 和设备(如硬件加速器)之间具有相干内存访问功能,通过利用 PCIe 架构的高级功能,满足下一代设计中处理数据和计算密集型工作负载的要求。

让我们探讨一下 CXL 设备的类型和 CXL 特有的验证挑战,例如维护主机 CPU 和加速器之间的缓存一致性。有关此规范的初步概述。

类型 1 CXL 设备

实现完全一致的缓存,但没有主机管理的设备内存

扩展 PCIe 协议功能(例如,原子操作)

可能需要实现自定义订购模型

适用交易类型:D2H 相干和 H2D 窥探交易

类型 2 CXL 设备

实现可选的一致缓存和主机管理的设备内存

典型应用是连接了高带宽存储器的设备

适用的事务类型:所有 CXL.cache/mem 事务

类型 3 CXL 设备

仅具有主机管理的设备内存

典型应用是主机的内存扩展器

适用的交易类型:CXL.mem MemRd 和 MemWr 交易

CXL.cache/mem 设计必须保持主机和设备代理缓存及其相应内存之间的缓存一致性。类型 1 CXL 设备的基于偏差的一致性模型定义了设备附加存储器的两种状态 – 主机偏置和器件偏置。每个国家都有自己的核查挑战。

CXL 充当高性能 I/O 互连系统,试图确保可靠、高效地访问分布在各个组件中的内存。其中一些组件通过使用本地缓存来优化性能,并减少内存访问的开销。为了支持这种类型的配置,CXL.cache 协议可确保在内存或本地缓存中的组件之间保存的数据与每个组件保持一致。CXL 中的设备组件通常用作计算密集型应用程序的加速器,因此包含本地缓存。因此,如果主机组件想要访问相同的内存位置,则可以强制设备从其本地缓存中逐出该行,并根据缓存行状态更新相应的内存位置。

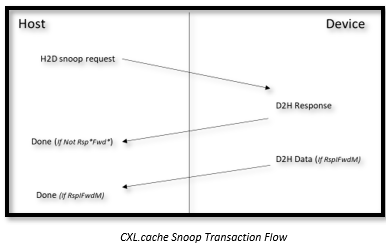

CXL.cache 协议将设备和主机之间的交互定义为多个请求,每个请求至少有一个关联的响应消息,有时还具有数据传输。该接口由每个方向的三个通道组成:请求、响应和数据。通道以其方向命名 - D2H(设备到主机)和 H2D(主机到设备)。

基于 CXL 的系统使用基于偏差的一致性模型来提高内存访问性能。当设备附加存储器处于主机偏置状态时,设备会像常规主机附加存储器一样访问它。如果设备需要访问设备附加的内存,它首先向主机发送请求,该请求将解析所请求行的一致性。

或者,当设备附加内存处于设备偏置状态时,可以保证设备没有缓存线路。在这种情况下,设备可以访问它,而无需向主机发送任何事务。但是,无论偏置状态如何,主机都会看到设备附加内存的统一视图。

在主机偏置状态和设备偏置状态下,设备附加存储器始终保持一致性。

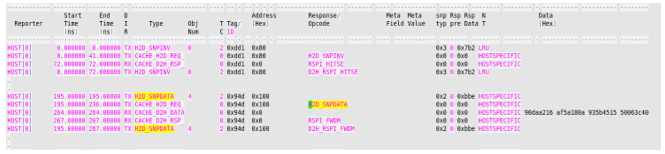

CXL.cache H2D Snp 事务交换:

主机向设备发送 H2D 请求 SnpData

设备接收请求并将 D2H 响应作为RSPI_FWDM发送到主机。

设备将 D2H 数据发送到主机

主机收到响应后事务完成

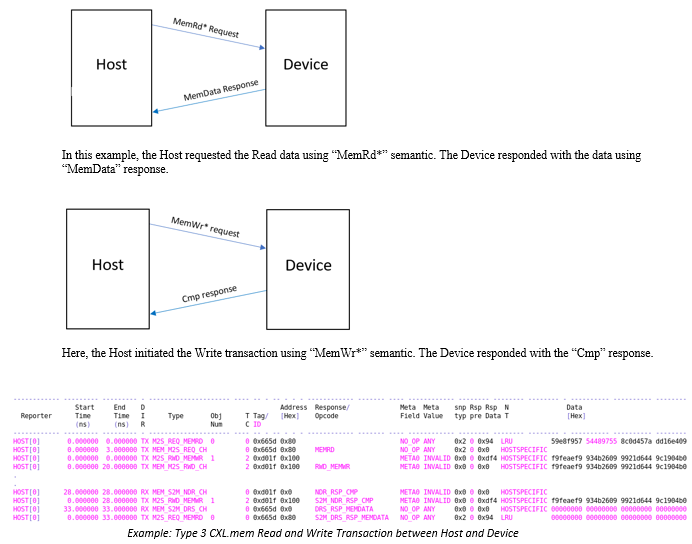

类型 3 设备主要是主机内存的内存扩展器。设备通过 CXL.mem 运行,以服务从主机发送的请求。类型 3 设备支持两种类型的流 – 读取和写入流。

Synopsys 是 CXL 设计 IP 和验证 IP 的市场领导者,为 CXL 生态系统的发展做出了重大贡献。请继续关注此新 CXL 规范的更深入探讨,包括其他事务类型、分层体系结构以及 CXL 设计的验证要求/挑战等主题。

审核编辑:郭婷

-

解码CXL存储器扩展设备(上)2023-12-04 1173

-

什么是CXL技术?CXL的三种模式、类型、应用2023-09-27 7684

-

澜起科技MXC芯片成功通过CXL联盟组织的CXL1.1合规测试2023-08-18 2261

-

揭开CXL的神秘面纱:概述2023-05-26 5091

-

访问CXL 2.0设备中的内存映射寄存器2023-05-25 3744

-

一文详解CXL链路层格式的定义2023-02-21 2455

-

CXL.mem是什么?2022-11-02 4099

-

CXL内存协议介绍2022-11-01 3174

-

CXL事务层详解2022-10-10 4683

-

CXL事务层的结构是由哪些部分组成的2022-10-08 2123

-

一文解析CXL系统架构2022-09-14 3745

-

一窥CXL协议2022-09-09 4523

-

labview数据类型简介2022-01-11 963

全部0条评论

快来发表一下你的评论吧 !