揭秘PCIe PIPE 5.1 SerDes架构

描述

人工智能和机器学习正在迅速渗透到广泛的设备中,推动了SoC设计的重新架构,需要更多的内存空间和更高的带宽来传输和处理数据。这种变化需要更高速的接口和更宽的总线,为最新 PCIe 协议规范的增强以及升级 PIPE(PCI Express 的 PHY 接口)规范作为首选 PHY 接口铺平了道路。

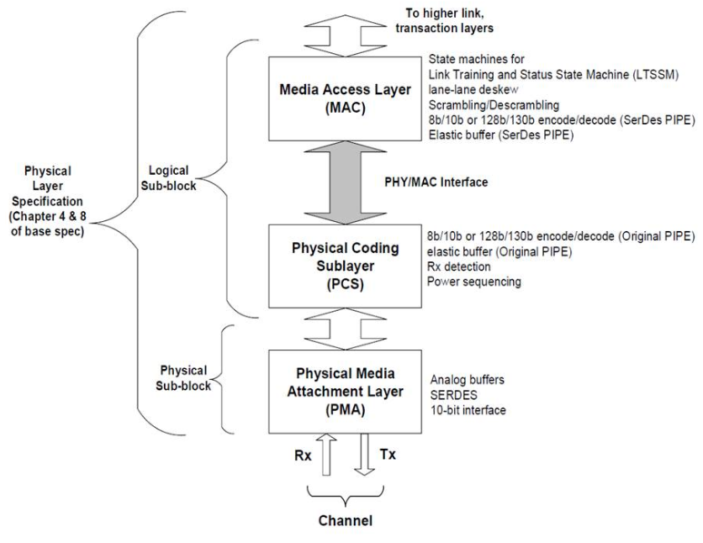

PIPE 规范已发展到版本 5.1.1,不仅是为了匹配最新的规范,而且还是为了扩展协议中的未来增强功能。SerDes 架构使 PIPE 5 PHY 协议不可知,所有协议特定逻辑都转移到控制器。这简化了PHY设计,并允许不同的协议栈轻松共享。用于 PIPE 接口的 SerDes 架构通过对物理编码子层 (PCS) 和媒体访问层 (MAC) 的职责进行一些关键更改以及对信令接口的更新来实现可扩展性。

图 1:PCI Express 的分区 PHY 层

PIPE 5.1规范除了SerDes架构和低引脚数接口之外,还有一些额外的更新。以下列表总结了 PIPE 5.1 中的主要升级:

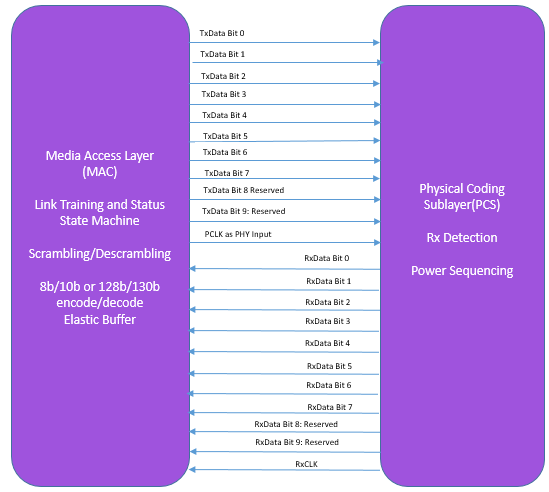

• 由 MAC 执行 8b/10b 或 128b/130b 编码/解码 • 弹性缓冲区控制由 MAC 维护,RxStatus 仅用于接收器检测目的

• PHY 在由“RxWidth”

确定的管道宽度上呈现与恢复时钟“RxClk”同步的 RxData • RxPolarity 场不再用于 SerDes 架构,MAC 负责反相接收器极性

• 由 MAC

执行环回 • 新的支持的 64 位数据宽度,专门用于 SerDes 架构

• PIPE 数据宽度为 10/20/40 位,而不是 8/16/32

随着 SerDes 架构带来的所有变化,调试和理解接口上 PIPE 数据的新格式变得具有挑战性。具体来说,新的PIPE宽度和编码器/解码器到MAC的转移导致PIPE接口上的数据看起来与以前的任何PIPE版本大不相同。当您继续阅读时,您将看到我们如何尝试将数据分解为更小的单元,以清楚地显示如何通过界面交换信息。

TxData/RxData 信号宽度为 10 位倍数 (80/40/20/10)。对于 8b/10b 编码,每 10 位携带 10b 编码数据。在 128b/130b 编码时,每 10 位携带 8 位数据,保留上两位。

图 2:跨 PIPE SerDes 架构的数据传输

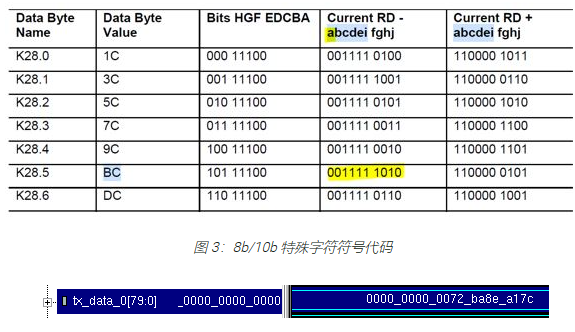

让我们看一下下图中在 1 位 PIPE 宽度上以 Gen2/Gen40 速度传输的 COM 符号。COM (8) 的 10b/0011111010b 编码值占用 TxData 的所有位 [9:0]。

位 'a' (来自 'abcdeifghj') 应该首先进入接口,所以它将是 17c。

请注意,2c 中剩余的 17 位(即 0001 0111 1100)对应于下一个符号。

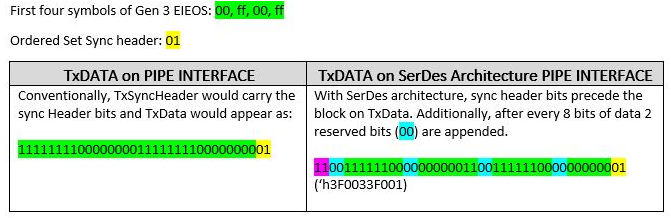

现在让我们看一下块编码数据。在 TxData/RxData 上呈现数据时,每个 8 位切片中仅使用 10 位,并保留上两位。考虑 3 位管道接口上的第 40 代电气空闲有序集 (EIEOS)。

• 编码在块前面添加 2 个同步标头位。请注意,它们是TxSyncHeader和RxSyncHeader。

SerDes架构正在全面迅速采用。随着 PIPE 规范的不断发展,复杂 PCI Express 控制器和 PHY 的设计和验证周期将变得更加复杂和耗时。Synopsys PCI Express VIP 完全支持 PIPE 5.1,并提供成熟全面的验证解决方案。

审核编辑:郭婷

-

什么是SerDes?SerDes有哪些应用?2025-03-27 7252

-

PCIe 5.0 SerDes 测试2024-08-16 3236

-

适用于PCIe 5.1、DP 1.5、USB 0.1、SATA和未来协议的PIPE 4.3.22023-05-26 6604

-

Pipe Go开源博客平台2022-06-09 482

-

PCIE基本概念与拓扑架构图2022-02-16 2799

-

SerDes协议简析2021-12-20 2093

-

GMII、SGMII和SerDes的差异总结2020-10-09 34744

-

axi_pcie3_0编译的解决办法?2020-07-25 2752

-

请问Virtex7 GTX如何生成PIPE接口PCIE PHY?2020-05-04 3022

-

请教关于C6678的serdes模块2018-08-06 2669

-

申请TI Keystone DSP PCIe SerDes IBIS-AMI Models。2018-06-21 1827

-

在Arria 10 PCI Express中更改串行和PIPE仿真的方法2018-06-20 6065

-

了解PIPE4.4规范及PCIe 4.0的开发设计2017-11-15 11969

-

参考时钟对SERDES性能的影响2017-02-10 6733

全部0条评论

快来发表一下你的评论吧 !