如何减少内存模型调试时间

描述

正在寻找缩短调试周期的方法,以快速从根本上解决内存控制器/PHY 和子系统验证项目中的问题?

在某些时候,您在调试内存模型时很可能面临以下挑战之一(计时问题、日志消息、银行统计信息、分层调试等)。

Synopsys 内存模型 (VIP) 与 Verdi 一起可提高整体调试效率。以下是紧密耦合的调试解决方案如何帮助解决一些痛点的示例:

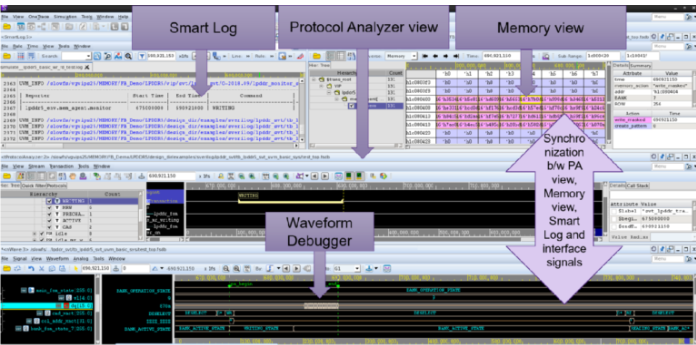

以协议为中心的调试使用户能够快速了解协议活动,识别瓶颈并快速查找和调试意外行为

协议视图中的错误、警告和消息注释可快速确定原因

交易、银行状态、内存内容和握手的图形视图,可立即访问特定于上下文的详细信息

锁定步骤链接到模拟器跟踪视图(波形),可在任何抽象级别轻松调试

以下是其他示例,其中包含详细说明供您参考:

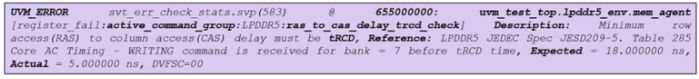

协议和计时冲突: 当内存VIP检测到协议/时序冲突时,通知将显示有关被破坏的规范部分的所有命令性信息,包括报告错误的组件,协议版本以及针对预期的规范定义值应采取的纠正措施。

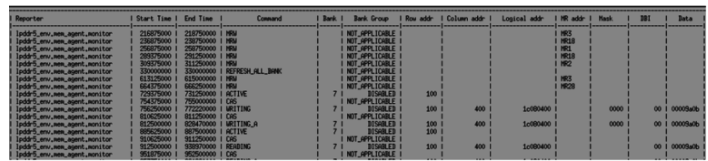

跟踪文件: 跟踪是特殊的文本文件,其中包含有用的信息,例如事务的开始/结束时间和命令名称等。例如,如果命令是“模式寄存器”,则会显示与“模式寄存器”字段相关的所有信息,例如读/写命令、相关地址、数据和重要信息,如延迟、DBI、DM 和模式寄存器设置。

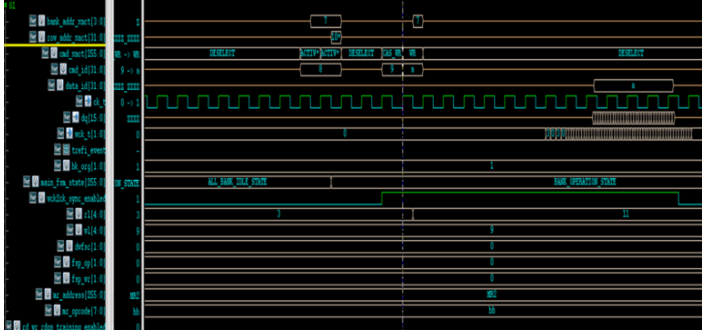

调试端口:它们在高度抽象中提供了协议流量的可视化表示,例如在哪个银行执行交易、编程模式寄存器值、银行状态、命令和数据 ID 标记以将数据与相应的命令相关联,以及其他功能。调试端口作为 Synopsys 内存 VIP 接口的一部分提供,并可加载到波形查看器(如 Verdi)上。

威尔第协议分析器流程:这提供了交易、银行状态、内存内容的配置设置、模拟等的图形可视化。通过同步视图,用户只需单击ERROR消息,相应的牵引,内存地址位置和信号电平流量信息等详细信息将突出显示给用户。

Synopsys Memory VIP 独特、灵活的架构使其可以轻松插入任何基于 Verilog/SV/UVM/VMM 的测试平台设置。

审核编辑:郭婷

-

物理内存模型的演变2024-02-25 1356

-

调试准备怎么减少时间2019-05-16 1128

-

嵌入式减少调试时间的3个技巧2022-06-28 3968

-

用于快速模型的模型调试器11.20版用户指南2023-08-10 603

-

Elastos内存管理对软件调试的支持2011-12-01 680

-

如何减少 MQX RTCS 使用内存2015-11-26 754

-

减少调试时间的 3 个技巧2022-07-14 2752

-

更改CTC规则以减少训练和解码中的内存消耗2022-10-11 2438

-

边缘AI的模型压缩技术2023-05-05 1882

-

简化内存模型的调试2023-05-26 1573

-

嵌入式软件开发之如何减少调试时间2023-06-02 774

-

求解大型COMSOL模型需要多少内存?2023-10-29 3779

-

jvm内存模型和内存结构2023-12-05 1762

-

如何有效减少PCBA的打样时间2024-06-04 990

-

深度学习的模型优化与调试方法2024-07-01 2875

全部0条评论

快来发表一下你的评论吧 !