适用于PCIe 5.1、DP 1.5、USB 0.1、SATA和未来协议的PIPE 4.3.2

描述

人工智能和机器学习正在迅速渗透到广泛的设备中,推动了SoC设计的重新架构,需要更多的内存空间和更高的带宽来传输和处理数据。这种变化需要更高速的接口和更宽的总线,为增强最新的 PCIe、USB、DP 和 SATA 协议规范以及升级 PIPE(PCI Express 的 PHY 接口)规范作为首选 PHY 接口铺平了道路。

PCIe 基本规范已升级到版本 5.0,修订版 0.7,预计很快就会升级到修订版 1.0。PCIe 5.0 引入了 32 GT/s 的更高链路速度作为其主要新功能,也称为 Gen5 速度。为了加速PCIe系统的发展,PIPE接口在行业中得到了广泛的应用。随着基本规范升级到5.0,PIPE规范也在迎头赶上,并已升级到5.1.1版本。最新的规格版本使 PIPE 接口能够达到 Gen5 速度,并提供了一些额外的增强功能。

PIPE 规范已发展到版本 5.1.1,不仅是为了匹配最新的规范,而且还是为了扩展协议中的未来增强功能。在我们之前关于 PIPE – PCIe PIPE 4.4.1:PCIe 4.0 的推动者博客中,我们讨论了 PIPE 规范版本 4.4 中可用的功能。在这篇博客中,我们将讨论 PIPE 规范版本 5.1.1 中添加的新功能。

PIPE 4.4.1 已经将 PHY 设计的数字和模拟方面与控制器设计隔离开来,从而在 SoC 开发周期中提供了明确的推动力,因为现在控制器设计必须只满足其设计的协议方面。但是,对于 PIPE 4.4.1,PHY 供应商应该为不同的协议开发不同的 PHY,或者设计单个复杂的 PHY 来满足多种协议,如 PCIe、USB 和 SATA。当必须升级设计以适应 PCIe、USB、DP 和 SATA 协议规范中的所有增强和升级时,此使用模型不可扩展。此外,一种新的隧道协议也正在出现,通过通用PHY传输USB,PCIe和DP。这为PHY设计铺平了道路,PHY设计简单且与协议无关,能够以更低的空间成本处理更高的带宽。PIPE 5.1.1 通过引入新功能“SerDes 架构”和“低引脚数接口”,巧妙地解决了这些要求。

SerDes 架构使 PIPE 5 PHY 协议不可知,所有协议特定逻辑都转移到控制器。这简化了PHY设计,并允许不同的协议栈轻松共享。低引脚数接口可满足低房地产成本要求。对于更宽的数据总线,数据路径已经消耗了接口上的许多引脚。减少引脚总数;大多数非时间关键边带信令握手通过MBI总线移动。有效的结果是PIPE接口上的引脚数量更少,数据路径更宽。此方法还可以针对未来的协议增强功能进行扩展。

PIPE 5.1.1 规范除了 SerDes 架构和低引脚数接口外,还有一些额外的更新。以下列表总结了 PIPE 5.1.1 中的所有主要升级:

添加了对显示端口和融合 IO 协议的支持,同时保持对 PCIe、USB 和 SATA 协议的支持

低引脚数接口

删除了旧版握手信号

将遗留信号映射到 PHY 和 MAC 的消息总线寄存器

引入了消息总线命令 [读取和写入] 的使用,以在以下所有子功能中在 PHY 和 MAC 之间通信握手

接收器均衡

动态均衡

TxDeemph, FS, LF, LocalFS, LocalLF 设置

接收器裕量

车道边距

弹性缓冲区控制

极性反转

块对齐控制

塞尔德斯建筑

启用与现有常规 8/16/32 位数据路径等效的 SerDes 数据路径

启用新的更宽的 SerDes 数据路径,相当于传统的 64 位数据路径。

低功耗 L1 子状态支持使用边带信号

已弃用“PCLK 作为 PHY 输出模式”,用于 PIPE 接口的操作

强制要求“PCLK 作为 PHY 输入模式”,用于 PIPE 接口的操作

这简化了PHY设计,因为“时钟生成”的负担现在转移到控制器设计中

添加了MAC和PHY握手,用于通信“速率”,“宽度”和“pclk_rate”信号变化

PclkChangeOk 和 PclkChangeAck 信号用于此握手

PHY 使用 PclkChangeOk 信号与 MAC 通信,表明 MAC 已准备好更改速率、宽度或 Pclk 频率

MAC使用PclkChangeAx信号与PHY通信,表明速率,宽度或Pclk频率的变化是完整和稳定的

添加了对 P2 电源状态下接收器检测的支持

已弃用的“车道关闭”信号

其中许多更新以向后不兼容为代价提供了未来的可扩展解决方案。其中一个示例是要求弃用传统边带信号并使用 MBI 总线在 MAC 和 PHY 消息总线寄存器空间之间发出握手信号。用于边带信号(例如均衡信号)的传统 PIPE 接口对于任何符合 PCIe 4.0 的设备执行接收器均衡和动态均衡功能是必需的,现在不再适用于符合 PCIe 5.0 的设备。接收器均衡和动态均衡通过 MBI 总线传输,使用 MBI 读写命令从 MAC 和 PHY 的消息总线寄存器空间寄存器。

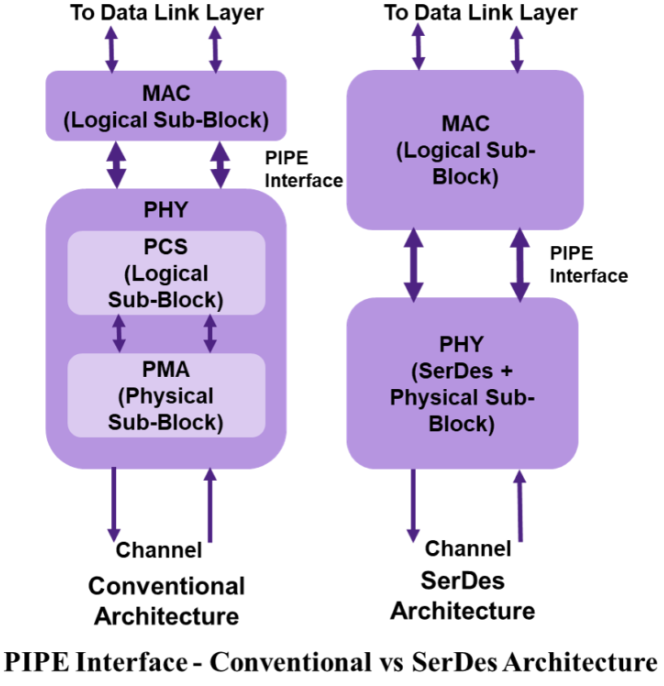

另一个剧烈的架构变化是对 SerDes 架构的可选支持。对于 PCIe 4.0 设备,对 SerDes 架构的支持是可选的,但对于 PCIe 5.0 设备是强制性的。随着SerDes架构的引入,与原始PIPE架构相比,PHY实现了最少的数字逻辑。这使得PHY设计具有可扩展性,并且易于在不同协议之间共享。仍然建议使用 PHY 设计来支持传统架构,以保持与选择不迁移到 SerDes 架构的 MAC 的互操作性。传统架构和SerDes架构的区别如下图所示。

审核编辑:郭婷

-

VIAVI Xgig4K-PCIe-X4-FL飞行引导插入器适用于PCIE4.0在被测设备和VIAVI协议分析仪机箱箱之间提供数据信号连接2025-03-19 1100

-

TS2PCIE412ruar芯片能否用于SATA1.0信号切换?是否支持SATA OBB信号?2025-01-07 527

-

适用于Emulex和OEM适配器的VMWARE ESXi 5.0/5.1 FC/FCoE驱动程序2023-08-08 522

-

揭秘PCIe PIPE 5.1 SerDes架构2023-05-26 10536

-

iTOP3A5000开发板多路PCIE、SATA、USB3.0等2022-12-01 1240

-

适用于小型应用的强大 USB Type-C™保护2022-11-01 788

-

适用于MiSTer v1.1的USB支架板2022-08-16 661

-

沉浸式Android11移植,iTOP-RK3568开发板双核GPU,独立NPU,SATA3.0,PCIE3.02022-04-29 2774

-

如何支持USB、DP、PCIe三种信号协议?2022-04-20 9738

-

详解串行总线中的SATA协议2021-11-01 12274

-

LTC3529 - 1.5A、1.5MHz 同步升压型稳压具自动故障检测功能,适用于 USB OTG 应用2021-03-20 772

-

VIAVI推出适用于PCIe 5.0协议一致性训练器2020-12-18 1274

-

请问Virtex7 GTX如何生成PIPE接口PCIE PHY?2020-05-04 3022

-

USB标准适用于哪些应用2009-04-19 2398

全部0条评论

快来发表一下你的评论吧 !