CCIX over PCIe:用于AI、网络、4G/5G和存储设计的更快相干互连

描述

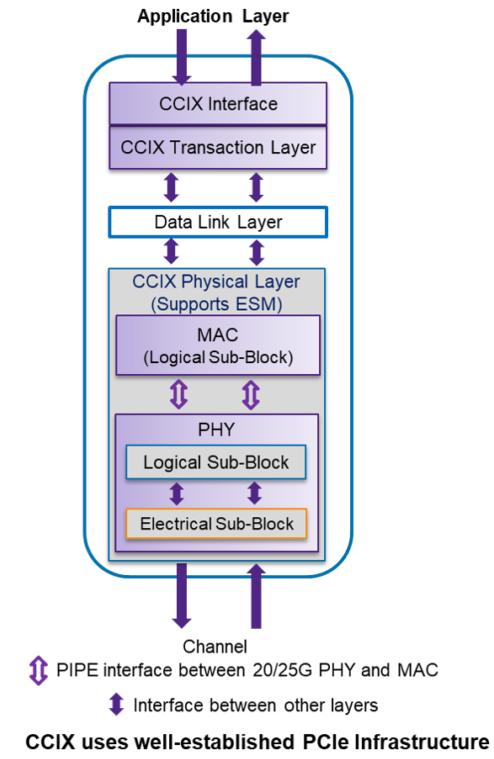

下一代 SoC 设计需要更快的相干互连,以实现机器学习、网络处理、存储卸载、内存数据库和 4G/5G 无线技术等高性能应用。CCIX(加速器缓存一致性互连)是一种新的协议标准,它提供了缓存一致性和对等处理的优势,可实现更快的互连。CCIX 设计巧妙,使用完善的 PCIe 基础设施在链路上传输一致性数据包,只需进行少量修改。CCIX 规范与 PCIe 基本规范 4.0 兼容。PCIe 实现被扩展为实现 CCIX 事务层,负责承载一致性消息。

16GT/s 以上的数据传输:

根据CCIX联盟,数据传输可以以25GT / s的最大速度完成,从而提高PCIe 4.0最大速度,否则限制为16 GT / s。 CCIX引入了一种称为扩展速度模式(ESM)的功能,以实现20 GT / s和25 GT / s的链路速度。支持此模式的 PCIe 组件必须增强物理层以实现更高的速度;但是,除了 EIEOS 和控制 SKP 操作系统格式更改外,有序集字段中不需要任何增强功能。要实现 CCIX ESM 速度,请执行以下步骤来保持 PCIe 和 CCIX 协议之间的兼容性。

使用正常的 PCIe 链路初始化过程按照相互支持的最高 PCIe 速度执行链路连接

应用层读取特定于 CCIX 的配置寄存器,以检查两个组件是否都支持 ESM

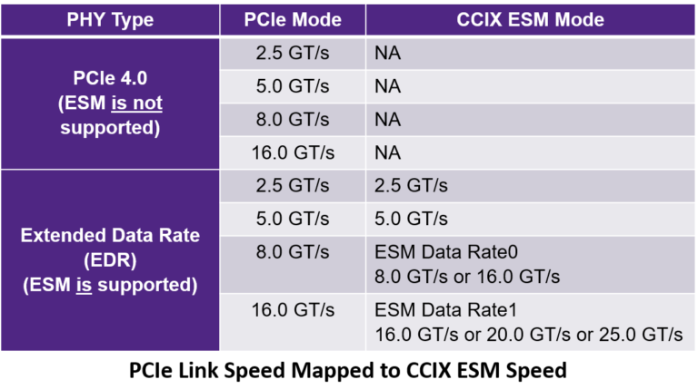

如果支持 ESM,则两个组件上的 CCIX 特定寄存器将被编程为映射 PCIe 链路速度,如下表所述

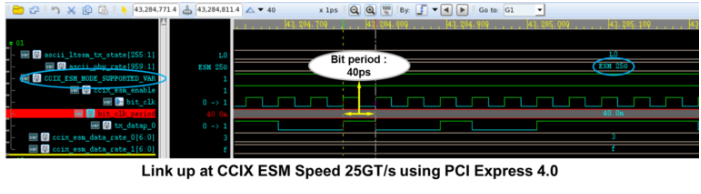

链路经过重新训练以实现 CCIX ESM 速度,因此两个组件都可以以 25GT/s 的最高速率执行数据传输

下面的Verdi快照显示了与Synopsys VIP for PCIe 25.4的连接速度为0GT / s。串行 PCIe 链路上所需的位周期为 40ps。

使用 PIPE 4.4.1(用于 PCIe 的 PHY 接口)可以实现更高的性能,从而减少 SerDes 中的延迟,从而加快仿真速度。它还可以轻松快速地集成。但是,需要进行一些自定义,因为目前没有 CCIX over PIPE 接口的行业标准规范。消息总线接口有助于执行所需的自定义。

审核编辑:郭婷

-

嵌入式设备中的4G/5G模块管理2024-07-13 3573

-

5G是什么?5G到底什么时候来?2016-06-14 7347

-

3G、4G、5G通讯技术背后有什么意义(上)?2019-08-19 2710

-

什么是5G天线及射频?2019-09-17 10387

-

5G网络的建设方案2020-12-03 4294

-

4G/5G日常网优命令2021-03-03 7553

-

5G网络架构,5G中的SDR和SDN是什么?2023-05-05 1790

-

5G天线和4g天线能通用吗?有何区别?2023-05-09 6417

-

5g网络4g手机能用吗2018-11-10 610424

-

5G网络与4G网络的区别2020-05-02 18175

-

手机信号升级5G网络后,原先使用的4G手机该如何处理2020-06-10 7939

-

不办5G套餐也能用5G网 流量从4G套餐中扣除2021-01-15 6545

-

4G手机能否用5G网络2021-04-29 19507

-

5g网络和4g网络有什么区别2023-05-06 9383

-

5G和4G的区别 5g网络比4g网络耗电吗?5g功耗是4g的多少倍?2023-10-19 6703

全部0条评论

快来发表一下你的评论吧 !