DFI 5.0如何确保DDR5/LPDDR5系统的更高性能

描述

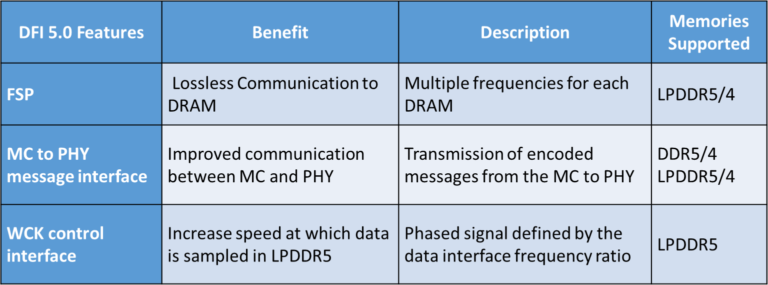

数据中心、存储、汽车和其他新兴市场应用的增长正在推动下一代内存技术(DDR5、LPDDR5)的发展。与其前辈一样,最新的内存技术也使用内存控制器和PHY之间的标准接口DFI,以降低集成成本并提高性能和数据吞吐效率。DFI 也随着内存技术的发展而发展,下一代 DFI 5.0 在这里确保使用 DDR5/LPDDR5 的系统具有更高的性能。在这篇博客中,我们将讨论 DFI 5.0 规范的新功能。

DFI 定义了跨接口高效通信所需的信号、时序和功能。该规范是为内存控制器和PHY的设计而开发的,但对内存控制器如何与系统设计接口或PHY如何与DRAM设备接口没有任何限制。

在DFI 5.0中,训练模式已经完全转变为独立于PHY的训练模式,通过PHY训练内存接口而不涉及控制器。减速模式也已扩展到 2N 模式。还添加了一个新的信号dfi_2n_mode以支持此行为。DFI 5.0 还有其他重大改进,以降低功耗,并改善互操作性和接口通信。

特定于 LPDDR5 的 DFI 更改

FSP(频率设定点)

LPDDR4/5 增加了两组物理寄存器空间,FSP0 和 FSP1,无需重新训练即可在两个不同的工作频率之间切换。DFI 状态接口新增信号dfi_freq_fsp,指示系统运行 FSP。该信号仅在初始化或DFI频率变化操作期间应更改。新参数 dfifspx_freq已添加(其中 x 由 DRAM 中支持的 FSP 数量定义),它定义了每个 FSP 的频率。这是由dfi_frequency信号和phyfreq_range可编程参数定义的编码值。

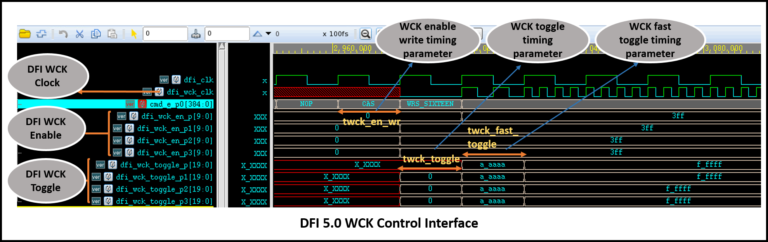

WCK(写入时钟)

LPDDR5 SDRAM使用两种不同频率的时钟。WCK 的频率比命令时钟高四倍或两倍。在DFI 5.0接口中定义信号以控制WCK同步序列 - 打开WCK,切换模式,静态状态和关闭WCK。信号从控制器发送到PHY数据片,是由数据接口时钟频率比定义的相位信号。dfi_wck_en信号定义时钟何时启用或禁用。dfi_wck_toggle信号传达 WCK 的状态:STATIC_LOW、STATIC_HIGH、切换和FAST_TOGGLE。

DDR5/LPDDR5 的 DFI 接口更改

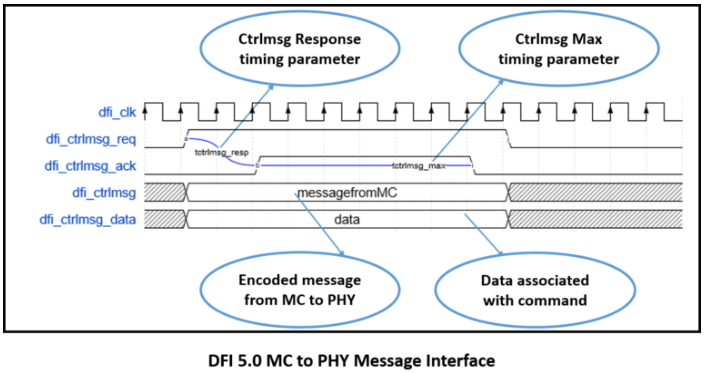

消息接口

MC 到 PHY 消息接口处理从 MC 到 PHY 的编码消息的传输;它包括信号和定时参数。在 DDR 内存子系统中,控制器和/或 PHY 可能支持内存子系统功能。在某些情况下,控制器执行的函数可能会导致需要向 PHY 发送消息。消息传递包括预定义的消息和特定于设备的消息。控制器和 PHY 应支持相同的编码。

简而言之,DFI 5.0 具有像 WCK 这样的新接口,以提高数据采样的速度,并支持多个频率集,从而实现与 DRAM 的无损通信。它还增加了消息接口,以改善MC和PHY之间的通信。其他接口更改包括降低功耗的增强功能、与 PHY 无关的启动顺序以及扩展频率更改支持等。

审核编辑:郭婷

-

DDR5 设计指南(一):DDR5 VS LPDDR52025-10-27 11454

-

新品迅为RK3588-LPDDR5核心板_LPDDR4x与LPDDR5的区别2024-07-17 1124

-

Introspect DDR5/LPDDR5总线协议分析仪2024-08-06 4850

-

LPDDR5相对于LPDDR4,性能上又有哪些提升呢?2021-06-18 2922

-

LPDDR5 DRAM芯片的性能及应用是什么?2021-06-26 2002

-

大多DRAM厂商DDR5相应产品发售,DDR5能成为市场的主流吗2020-03-01 3712

-

5G时代你是等DDR5上市 还是升级DDR4内存2020-03-30 11419

-

DDR5单条内存128GB不再遥远,性能和容量均兼备2020-04-05 5712

-

为什么三大厂商都在跟进DDR5?2020-05-27 2067

-

什么是LPDDR5呢?美光车用LPDDR5有何不同?2021-06-23 11137

-

芯动科技量产LPDDR5/5X/DDR5 IP一站式解决方案2022-06-24 4881

-

lpddr4x和lpddr5区别 lpddr4x和ddr5的区别大不大2023-08-21 36082

-

lpddr5时序比ddr5慢多少2024-01-04 8661

-

Amphenol DDR5/LPDDR5 CAMM2连接器:高性能内存连接新选择2025-12-09 928

-

Altera面向DDR5与LPDDR5的FPGA解决方案现已实现量产交付2026-03-13 1474

全部0条评论

快来发表一下你的评论吧 !