SOC设计之外部存储器

电子说

1.4w人已加入

描述

Soc芯片的片外存储器

FLASH设计实例

**NOR FLASH **

NAND FLASH

主存储器的主要技术指标

- 存储容量

存储器可以容纳的二进制信息量(寻址空间,由CPU的地址线决定) - 实际存储容量: 在计算机系统中具体配置了多少内存。

- 存取速度: 存取时间是指从启动一次存储器操作到完成该操作所经历的时间,也称为读写周期;

- 可靠性: 用平均故障间隔时间来衡量MTBF(mean time between failure)

- 功耗: 每个存储元消耗功率的大小

DRAM和SRAM时序比较

DRAM :

SRAM : 地址、数据和控制信号在同一上升沿变化

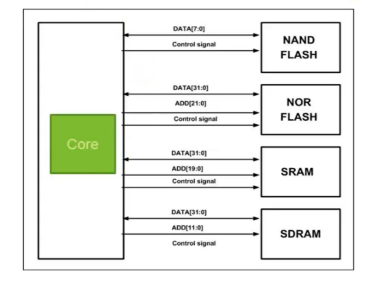

外部存储器控制器

连接在AHB总线上,管理片外存储器,如FLASH、SRAM、DDR等;

EMI在SOC芯片中的位置:

EMI控制器

- 支持SRAM、SDRAM、ROM、NOR FLASH及NAND FLASH,芯片外部存储接口模块提供了对这些外部存储器的读写接口,并且可以通过配置相关的寄存器,灵活的实现对不同外部存储器的操作。

片选信号和地址范围,普通SRAM接口

- 提供6个可配置的片选信号:CSA、CSB、CSC、CSD、CSE、CSF,用来实现对ROM、SARM、NOR FLASH 的片选。其中CSE、CSF与SDRAM片选信号复用;

- 每个片选支持的最大寻址范围为64M

- 每个片选可配的起始地址

- 启动片选可选配16位总线或者32位总线

支持SDRAM接口

- 提供2个相互独立的与SRAM复用的片选信号:SD_CSF,SD_CSF,作为SDRAM的片选,与SRAM、ROM、FLASH的片选CSE CSF复用

- 每个片选支持有4个bank的SDRAM,支持同时激活active最多达4个bank

- 提供选用的SDRAM型号,tRC,tRP,tRCD,CAS latency可配置

支持NAND FLASH接口

- 提供一个片选:nand_cs

- 只支持整个pape的操作,也就是每次读写都是一个pape。通过配置地址寄存器,控制字寄存器,然后对数据寄存器进行访问,从而完成对NAND FLASH的操作

- 支持从NAND FLASH直接进行系统启动

- 支持ECC校验的一位纠错

- 只支持8位数据线的NAND FLASH

SRAM控制器IP的设计

接口信号:

- AHB slave接口信号

- 输出给SRAM的控制器

AHB接口(标准slave)

片外SRAM存储器接口

SRAM控制器结构

SRAM控制器模块划分

- **BUS **接口

- 处理AHB接口信号

- 区分寄存器操作,存储器操作

- 寄存器

- 控制存储器地址范围、位宽

- 控制存储器访问方式

- **SRAM **状态机

- 处理有效的存储器操作

- 考虑各种传输类型:Burst长度、数据位宽、读写操作

- 控制输出信号的时序

- **SRAM **接口

- 根据状态机的控制输出相应的信号给SRAM

- 匹配总线位宽和SRAM位宽

SRAM控制器状态机的设计

- IDLE状态

- 读数据准备状态

- 写数据状态

- 写数据准备状态

- 写数据状态

EMI模块设计小结

- 挂在AHB总线上

- 接口信号

- AHB总线接口信号

- 片外存储器SRAM控制信号

- 子模块划分

- 总线接口模块

- SRAM接口模块

- SRAM状态机:控制寄存器的访问方式、时序、传输类型等

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SoC设计中常用的存储器2023-09-18 1834

-

外部存储器2012-11-04 3017

-

如何实现嵌入式ASIC和SoC的存储器设计?2019-08-02 1687

-

哪种类型的同步SRAM用于外部存储器?2019-08-15 2277

-

外部数据存储器的扩展实验2021-12-07 2141

-

外部存储器的相关资料下载2021-12-10 1355

-

如何选择DSP芯片的外部存储器?2009-04-07 2311

-

外部存储器电路接口电路图2009-11-13 3328

-

基于SOC的高性能存储器控制器设计2017-01-07 1121

-

存储器之外 东芝还有哪些值得关注的地方?2017-04-26 1723

-

简述 Stratix 10 外部存储器接口作用2018-06-20 3450

-

卡西欧计算器外部存储器开源2023-02-09 1245

-

什么是外部存储器2023-05-26 3383

-

外部存储器是ROM还是RAM2024-08-06 5329

-

外部存储器有哪些2024-09-05 8156

全部0条评论

快来发表一下你的评论吧 !