面向图形、网络和HPC的下一代内存技术

描述

在这个革命性技术的时代,内存在任何需要高速处理的应用中都起着至关重要的作用。高分辨率图形需要高速和高带宽图形内存,因此需要快速采用下一代内存技术高带宽内存(HBM)。HBM 正在进入领先的图形、网络、HPC(高性能计算)和人工智能系统;例如,视频信号解码器、全自动驾驶汽车、神经网络设计以及其他需要低功耗和大带宽的高级应用。我们之前的内存博客 – 下一代内存技术:准备好迎接验证挑战了吗?,讨论了跨应用的几种下一代内存技术。本博客将回顾 HBM 的详细信息,HBM 是用于图形、网络和 HPC 的下一代内存技术。

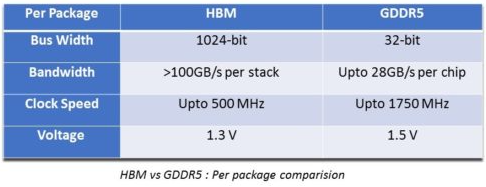

在过去的十年中,GDDR5已成为行业标准,并在所有面向图形的技术中占据重要地位。GDDR5 专注于使用更多功率来实现更高的时钟速度。GDDR5 芯片以单层形式直接连接到显卡,这意味着添加更多内存涉及在显卡上水平展开。因此,功耗和外形尺寸一直是主要问题。HBM 已成为打破所有加工瓶颈的替代方案。

HBM: 面向图形的内存技术的未来

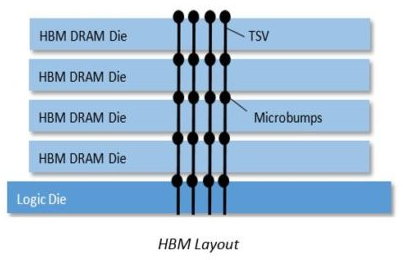

HBM 是一种 3D DRAM 技术,可堆叠多达 2 个 DRAM 芯片,这些芯片通过 TSV(硅通孔)和微凸块互连。它通过分布式接口与主机计算芯片紧密耦合。接口分为完全独立的通道,不一定彼此同步。HBM DRAM 使用宽接口架构来实现高速、低功耗运行。HBM 现已升级到 HBM2,每个堆栈最多可容纳 <> 个芯片,引脚传输速率翻倍至 <>GT/s,适用于性能敏感的消费类应用。

主要特点

与任何其他 DRAM 一样,HBM 内存由主机内存控制器的命令控制。它提供了两个独立的行和列命令接口,允许激活/预充电与读/写并行发出,因此这简化了控制器操作并提高了效率。它一次处理 128 位数据,支持 2n 个预取架构,每个内存读写访问 256 位。

HBM2 的关键增强功能之一是其伪通道模式,它将一个通道分成两个单独的子通道,每个子通道 64 位 I/O。这些通道是半独立的。在传统模式下,每个页面的大小为 2KB,但在伪通道模式下,它只有 1KB。页面大小越大,打开页面所需的电量就越大。由于伪通道页面的大小只有其一半,因此还需要大约一半的电流。这些伪通道半独立运行,它们共享通道的行和列命令总线以及 CK 和 CKE 输入,但单独解码和执行命令。它们还共享设备模式寄存器。

HBM 还具有温度传感器,控制器可以读取该传感器以调整其刷新率。它支持温度补偿自刷新。RAS(可靠性、可用性和灵敏度)功能包括对用于数据纠错和列/行地址/数据奇偶校验的 ECC(纠错码)的支持。HBM 的另一个吸引人的特点是 用于 IEEE-1500 访问的 JTAG 连接, AWORD 和 DWORD 训练, 通道修复, 边界扫描和环回测试模式.这些内置的自检 (BIST) 和内置的自修复 (BISR) 功能使 HBM 成为最复杂的动态 RAM 之一。这些测试功能用于组装系统级封装(SiP)的最后测试步骤。

总而言之,HBM 是性能、功耗和外形受限系统的突破性内存解决方案,提供高带宽、低有效功耗和小尺寸。与将 DRAM 芯片尽可能靠近电路板放置的传统内存设置不同,HBM 将一堆 RAM 芯片堆叠在一起。

审核编辑:郭婷

-

SK海力士开发出下一代智能内存芯片技术PIM2022-02-16 2044

-

2016CES:Atmel下一代触摸传感技术亮相2016-01-13 3213

-

为什么说射频前端的一体化设计决定下一代移动设备?2019-08-01 3140

-

如何建设下一代蜂窝网络?2019-08-19 2542

-

下一代SONET SDH设备2019-09-05 2632

-

请问Ultrascale FPGA中单片和下一代堆叠硅互连技术是什么意思?2020-04-27 2389

-

下一代超快I-V测试系统关键的技术挑战有哪些?2021-04-15 2158

-

面向下一代电视的低功耗LED驱动IC是什么?2021-06-04 1956

-

下一代网络概述2009-06-22 901

-

下一代网络体系结构及相关问题的研究2009-08-06 1458

-

面向下一代网络的开放式API技术研究2011-03-30 778

-

Qorvo宣布推出面向下一代光网络的高速产品系列2015-05-05 2050

-

下一代网络核心技术概览2016-01-14 816

-

下一代无线技术是VR下一代发展的缺失环节2019-08-11 1116

-

下一代英特尔至强可扩展处理器将集成高带宽内存(HBM)。2021-07-01 9354

全部0条评论

快来发表一下你的评论吧 !