使用Synopsys VIP和测试套件进行验证

描述

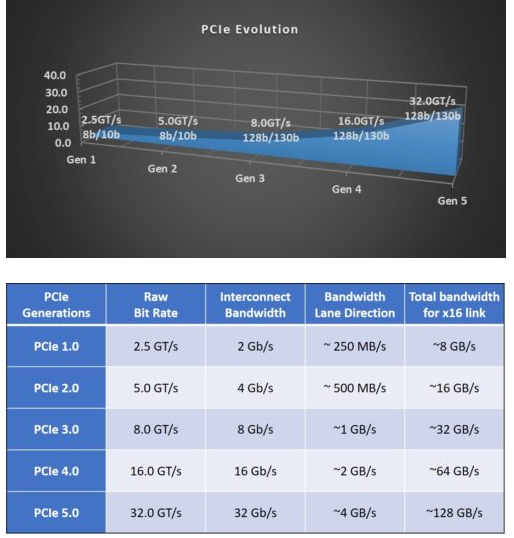

PCI Express 0.32规范将比特率提高一倍,达到每通道128GT/s,为x16 Link(16通道)提供约<>GB/s的带宽。下图提供了不同 PCIe 代的比特率和带宽的比较。

PCIe 物理层在以 128.130 GT/s 数据速率运行时将使用 32b/0b 编码。此新数据速率将与先前的数据速率向后兼容。PCIe 链路将以 0.2 GT/s 的速度训练到 L5 状态,就像以前一样,然后移动到更高的数据速率。采用 1b/2b 编码和 8b/10b 编码的 TS128 和 TS130 有序集得到增强,包括 32.0 GT/s 数据速率支持。均衡阶段类似于上一代 8.0 GT/s 和 16.0 GT/s 数据速率。在以 0.2 GT/s 的速度对 L5 进行初始链路训练后,链路将以 8.0 GT/s 的速度执行均衡,然后依次执行 16.0 GT/s 和 32.0 GT/s 均衡。当支持 32.0 GT/s 时,以较低的数据速率跳过(或重新排序)均衡是一项可选功能。除了跳过均衡的此选项外,还将通过链路训练协商备用协议。

采用 128b/130b 编码的 ElEOS 有序集扩展为包括更长的 0 和 1 运行长度。 在 32.0 GT/s 时,添加了另外 19 组具有各种预设的顺应性模式。添加了新的扩展功能结构和几个寄存器字段,以容纳32.0 GT/s的数据速率。对于 32.0 GT/s 的数据速率,接收器和重定时器的通道裕量支持预计不会改变。

审核编辑:郭婷

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

新思科技VSO.ai如何颠覆芯片验证2025-05-21 1518

-

三星电子采纳新思科技Synopsys.ai EDA套件,完成GAA制程验证2024-05-06 1290

-

AMD如何将Synopsys AI验证工具用于测试2023-09-21 3059

-

使用Synopsys VIP签署PCIe 5.0验证2023-05-26 3709

-

开始使用AXI VIP,对UVM有一些基本的了解2023-05-25 11634

-

如何使用Xilinx AXI VIP对自己的设计搭建仿真验证环境的方法2022-10-09 5129

-

4-AMBA VIP 编程接口2021-12-08 957

-

基于C的测试和验证套件集成到常规UVM测试平台的方法2020-12-15 1380

-

Synopsys为Arm AMBA CXS的VIP提供EDA验证解决方案2020-10-15 5298

-

基于FPGA的PCIe总线接口的DMA控制器的实现并进行仿真验证2018-01-11 15071

-

Synopsys为更快速的SoC验证推出下一代验证IP2012-03-14 961

全部0条评论

快来发表一下你的评论吧 !