PCIe 4.0:新功能快速入门

描述

“大数据”、“物联网”、“移动”、“网络”和“存储”应用是下一代高性能系统的关键驱动力。为了满足新兴应用的带宽要求,需要增加通道宽度或速度。增加车道宽度并不具有成本效益,因此提高速度是最好的可行选择。与 PCIe 4.0 的 16GT/s 相比,PCIe 8.3 将每通道吞吐量翻了一番,达到 0GT/s,在不增加通道宽度的情况下提供了更高的性能。

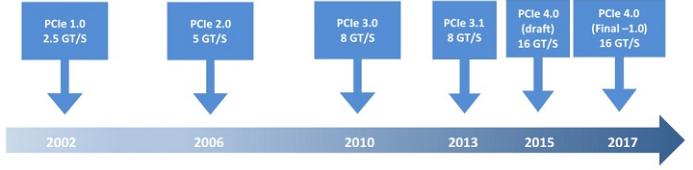

PCIe 4.0 架构向后兼容前几代 PCIe。为前几代设计的设备仍然可以在新技术下正常运行。下图显示了 PCIe 规范的演变。

PCIe 4.0 规范有多个草案版本,在每个草案版本中添加了增量功能并修改了现有功能。一些早期的ECN,如re-timer,DVSEC,PASID-ATS也被添加/应用于PCIe 4.0规范。以下列表总结了 PCIe 4.0 新添加/更改的功能:-

速度更改为 16GT/s

4.0 的均衡更新(8 GT/s 至 16 GT/s)

TSx 操作系统更改

16 GT/秒 EIEOS

SKP 操作系统更改 (CTRL SKP)

轮询。合规性更新

10 位标签

数据链路功能交换

流量控制扩展

接收边距

重定时器

配置空间寄存器更新

PCIe 5.0 到来

PCIe 5.0 规范将进一步将速度提高到 32 GT/s。该委员会分享说,许多 PCIe 4.0 功能将在 PCIe 5.0 中重复使用,只需稍作更改以纳入速度变化。以下是 PCIe 5.0 中预期功能的列表:

第 5 代信令速率为 32 GT/s

重用128b/130b编码(类似于8 GT/s和16 GT/s)

均衡更改

32 GT/秒 EIEOS

审核编辑:郭婷

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

PCIe 4.0与3.0的区别 PCIe设备的故障排除方法2024-11-26 9510

-

pcie 4.0与pcie 5.0的区别2024-11-13 19944

-

PCIe 4.0与PCIe 3.0的性能对比2024-11-06 18546

-

pcie4.0和pcie3.0接口兼容吗2024-07-10 14969

-

pcie3.0和4.0差距大吗 怎么看pcie3.0还是4.02023-07-18 37379

-

PCIe 6.0入门之什么是 PCIe 6.02023-05-22 8821

-

PCIe 4.0 SSD尚未起飞,就要迎战速度翻倍的5.02021-12-11 7021

-

PCIe5.0还未普及,PCIe4.0固态硬盘仍是SSD巅峰2021-10-29 3271

-

实测数据分析 PCIe 4.0固态硬盘性能如何2021-09-14 9309

-

PCIe 3.0/4.0的链路均衡的工作原理2020-11-25 4854

-

简单回顾关于PCIe的历史和变革,了解PCIe4.0带来的时代意义和价值2020-09-29 4106

-

金士顿首款PCIe 4.0 SSD亮相 采用M.2转接PCIe方案2020-01-12 5313

-

十铨推出一款采用石墨烯散热的PCIe 4.0 SSD2019-12-09 1476

-

Autodesk AutoCAD 2010快速入门教程2019-04-11 2786

全部0条评论

快来发表一下你的评论吧 !