如何使用测试套件解决JEDEC-UFS堆栈验证的7大挑战

描述

如果您目前正在使用或考虑在下一个设计中使用 JEDEC UFS 协议,您可能会面临一些验证挑战。以下博客将讨论 UFS 堆栈验证的 7 个最大挑战。随着人们开始减少引脚数量和提高速度,基于 MPHY 的堆栈已经发展势头强劲,并提供了越来越多的新应用程序来利用 UFS 堆栈。UFS协议由于其更高的性能、效率、并发多任务处理、使用完整带宽、安全性和可靠性以及更长的电源寿命而迅速被采用。

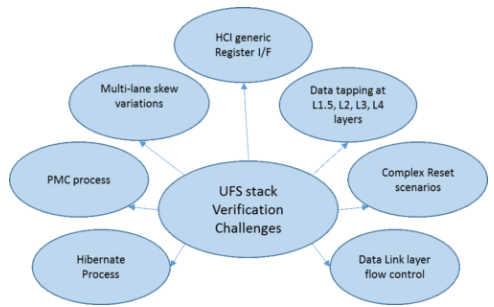

UFS 堆栈验证挑战

验证挑战

让我们从顶部开始,顺时针讨论上面描述的挑战。

HCI 通用寄存器 I/F

HCI(主机控制器接口)是 UFS 主机控制器中的寄存器编程,但允许用户决定寄存器接口。这突出了保持钩子的重要性,以便用户使用简单的RegToBus和BusToReg转换API将其UFS-Host-DUT集成到环境中。其次,将友好的UFS UPIU命令转换为HCI寄存器/存储器RD/WR指令也带来了更多挑战。

L1.5、L2、L3、L4 层的数据记录

Synopsys 在中间层提供了 VIP 的独特使用模型,可帮助用户独立验证 L1.5、L2、L3 或 L4 层的 DUT。这为我们提供了更好的分层数据流可见性。

复杂的重置方案

验证每个功能的突然重置,为热重置和冷重置创建复杂的重置方案,并验证后重置前条件。主要挑战是执行任何正在进行的进程的突然重置,并使用严格的数据传输和 PMC 进程检查休息后同一进程的重试。

数据链路层流控制

尽管有DME接口挂钩,但UniPro具有中间层,即传输层,网络层,数据链路层和物理适配器层。当然,人们会验证从传输到物理适配器层的数据流,反之亦然,但最具挑战性的部分是当控制 SAP 在两者之间中断这些流时,重要的是每一层都退出当前进程,然后稍后以优雅的方式确认下一个进程。

众所周知,对于给定的 TC0/TC1 帧,将从接收流量类帧的设备调度应答帧。现在有趣的一点是,协议没有说明何时调度AFC / NAC,因此验证应该有旋钮来控制超时期限内AFC / NAC的调度,以避免任何PA_INIT过程。

其次,验证环境还应检查 DUT 是否正在清除数据链路层的所有帧缓冲区,这些缓冲区可能包含复位时的正常帧、重新传输的帧和控制帧。这里的想法是重新调用尚未确认的预重置帧。

创建在DL_PAUSE请求及其确认期间可能存在中断的方案。这种情况将验证数据链路和物理适配器层之间的数据流在进入休眠状态期间的正确暂停和恢复,或者启动PA_INIT进程或 NAC 传输。

休眠进程

在一个完整的 PMC 请求进程生成中验证预休眠进入和退出、具有 L4 数据传输的重叠休眠请求、休眠请求和 PMC 请求 PACP 帧的配置。

在休眠过程中,重要因素对协议指定的最短休眠时间的 DUT 进行压力测试,并在此时间段后立即退出。这些排除了遗漏的任何其他延迟,当计时器超过所需的最小延迟时,可能会忽略这些延迟。

其次,在退出休眠时,数据链路层是否在PA_TActivate时间后正确取消暂停。这可以通过发送即时数据,然后休眠退出过程来实现。

PMC 流程

验证电源模式从非常低的速度(如PWM_G1)更改为HS_G3。在这种情况下,MPHY 如何处理配置更改以及允许的最小和最大PA_SaveConfig计时器。在这种情况下,当 MPHY 以串行模式嵌入 UNIPRO 时,时钟会从PWM_G1变为HS_G3,从而确保 MPHY 内部时钟模型的稳定性。在这里,UNIPRO规范中提到的最小SAVE配置时间(40ns)不足以满足MPHY的需求。

当 DUT 中未通告功能本身的兼容性时,发出 PMC 请求时会发生什么情况?我们如何确保如果此类请求是从 DUT 发起的并且得到遵守?如果遵循,则 PMC 是否与请求帧中的功能集一起发送。这种情况会检查 DUT 的启动功能。

针对 DUT 功能创建 PMC 请求,并在重试中创建不同的配置请求、PMC 进程与 L4 数据传输的重叠等。以及稍后要讨论的更多内容。

多通道偏斜变化

由于它是一个多通道协议,另一个有趣的因素是处理数据多通道的对齐。

在多车道环境中生成随机偏斜,车道-车道之间具有正负偏斜。

确保在PMC和Hibernate进程之后以最少的配置时间进行所有数据传输,特别是并以最大的倾斜启动下一个进程。

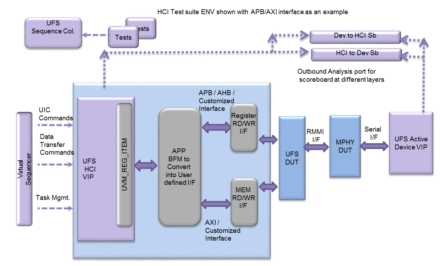

新思科技 UFS 测试套件可应对上述验证挑战

为了应对上述所有验证挑战,Synopsys 提供了独特的 UFS 测试套件解决方案。下图描述了 UFS 堆栈中上述挑战的理想解决方案。

UFS 主机测试套件框图

用于 UFS-主机 DUT 验证的 Synopsys 解决方案提供了将 UFS 主机控制器 DUT 集成到 UFS 主机测试套件中的简单步骤。上面的示例显示了 AXI/APB 寄存器接口和到主机控制器的内存接口的现成转换模型。

其中一个关键区别在于,Synopsys UFS VIP 可以配置为独立的 HCI-VIP,它将 UPIU 序列信息转换为寄存器读/写或存储器读/写命令转换,以“uvm_reg_item”接口的形式。这使得用户更通用地使用UVM_REG_OBJECT并在已经连接了 RAL 的现有环境中使用它。更有趣的是,解决方案应该能够提供所有必要的旋钮来创建所有 UFS 流量,并在 VIP 充当 HCI 或 UFS 主机时重复使用相同的旋钮。这样,如果要将独立的HCI嵌入到现有环境中,用户就可以更轻松地维护测试环境。该解决方案清楚地描绘了 UFS 主机 DUT 集成的干净即插即用模型。通过“uvm_reg_item”接口为寄存器覆盖提供简单的钩子。

对于所有其他挑战,如PMC、休眠过程、复位场景、数据链路层流控制、多通道偏斜变化,UFS测试套件解决方案提供了广泛的序列集合,涵盖了验证挑战的所有棘手方面。

不同层的记分牌供用户点击,以防需要中间层记分板。在上图中,记分牌显示在UPIU级别以用于说明。

审核编辑:郭婷

-

HBM量价齐飞,UFS加速普及:存储狂飙下的“最后质检”攻坚战2025-12-18 568

-

芯科普 | 一文了解存储主流配置UFS2023-06-30 27808

-

智能手机中的高速内存:MIPI UniPro v1.8 for JEDEC UFS v3.02023-05-26 4922

-

利用高级RPMB实现更快、更安全的UFS 4.0身份验证2023-05-25 5587

-

手机研发必须了解的UFS相关知识2023-03-29 1857

-

AN4230 STM32 MCU使用NIST随机数生成验证统计测试套件2022-11-21 646

-

什么是UFS 4.0,它对存储的未来意味着什么2022-05-21 12588

-

基于C的测试和验证套件集成到常规UVM测试平台的方法2020-12-11 3152

-

UFS2.2标准公布 加速推动UFS闪存普及2020-08-22 16456

-

JEDEC发布UFS 3.1规范,可使UFS存储设备更接近SSD2020-02-04 3854

-

eMMC与UFS的差异2019-09-18 3129

-

新ANSI/ESDA/JEDEC JS-002 CDM测试标准概览2018-10-24 5008

-

JEDEC 发布通用闪存标准 (UFS)2.0版2013-09-23 4704

-

2010年底JEDEC将公布UFS标准作为下一代的闪存存储规2010-07-01 896

全部0条评论

快来发表一下你的评论吧 !