快速集成USB测试套件以快速开始验证

描述

当今设计的SoC日益复杂,验证复杂性呈指数级增长,这不仅是由于设计的复杂性,也是由于协议的复杂性。由于陡峭的学习曲线,新兴的新协议使其更加困难。编写测试用例以涵盖整个协议成为 3-4 人年的工作,适用于 USB、PCIe 和以太网等复杂协议。Synopsys 提供 System Verilog/UVM 源代码测试套件来验证复杂的协议。提供源代码,测试可以扩展,并轻松定制。通过使用 Synopsys 测试套件快速启动验证并加速覆盖收敛,您可以节省工作量和时间。在这篇博客中,我们将概述USB测试套件,重点是易于集成和使用。

USB VIP 测试套件为一种类型的 USB DUT 提供了一个通用的测试平台。例如,有一个用于设备 DUT 的通用测试平台tb_dut_usb_device和一个用于主机 DUT 的通用测试平台tb_dut_usb_host。还提供了针对其他可能类型的USB DUT的不同测试平台。连接到设备 VIP 的主机 DUT 的测试平台提供主机驱动程序,用于将数据对象转换为特定于 DUT 的 API 序列。还有一个用于通用 xHCI 寄存器模型和内存操作的 xHCI 驱动程序,例如创建命令 TRB 并将其写入命令环、按命令门铃并观察命令完成事件 TRB。连接到主机 VIP 的设备 DUT 的测试平台提供了一个设备驱动程序,用于将数据对象转换为特定于 DUT 的 API 序列。

与 DUT 的预期连接是使用顶部模块中的特定“连接参数”实现的。可以在测试平台中运行预期的“连接类型”的测试。特定测试通过配置对象配置测试平台环境。测试平台级环境(TB_Env)基本上由两个子环境组成:Host_Env和Device_Env,也是TB_Env级虚拟序列器和TB_Env级序列集合。主机/设备环境由主机/Device_Env级虚拟序列器和主机/Device_Env级序列集合组成。因此,在TB_Env级别编写的序列可以面向主机/Device_Env级别的虚拟序列器。此主机/Device_Env级别的虚拟排序器由usb_transfer_sequencer、usb_service_sequencer和virtual_usb_sequencer组成。在主机/设备驱动程序中,接收的传输/服务要么使用 xHCI 模型(主机 DUT 作为 USB 控制器)进行处理,要么可以重定向到连接到 VIP 代理的排序器的主机/Device_Env中的virtual_usb_sequencer,传输/服务的处理由 VIP 完成。

要将 Synopsys USB VIP 测试套件集成到 DUT 中,使用以下 SystemVerilog 接口:

应用程序接口 – 此接口使用 AXI/AHB 接口对控制器执行 CSR(读/写),并对内存进行 DMA 访问 (_mem)。

设备/主机接口 – 这是将 USB VIP 连接到 DUT 的 USB 接口。

设备特定接口 – 驱动程序使用此接口轮询 DUT 的中断、事件和状态,从而控制 USB 测试套件驱动程序。

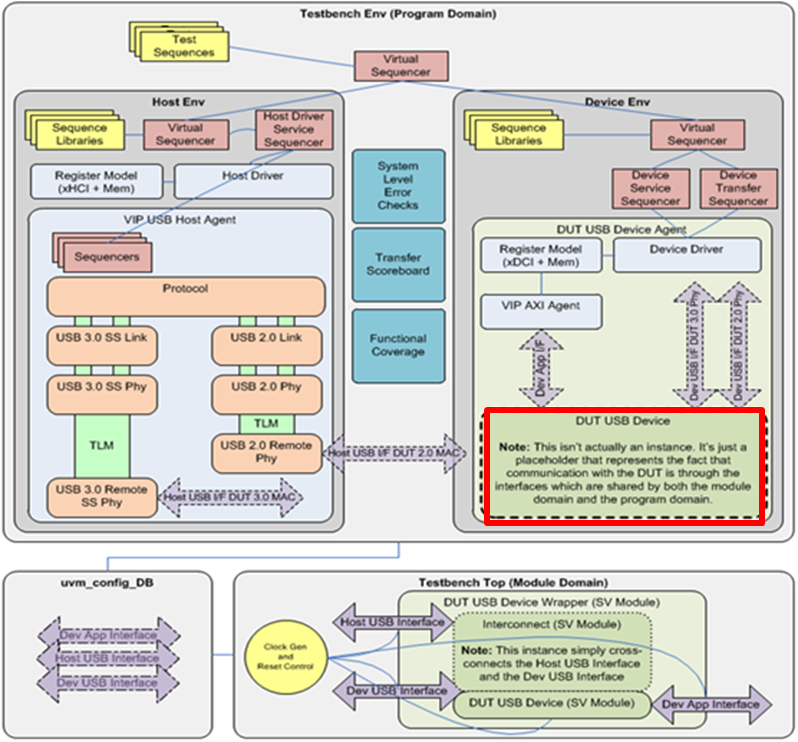

下图是具有以下设置的USB控制器DUT测试平台示例:

被测器类型:USB 设备

DUT 包括 PHY:否

应用界面:安巴AXI

USB 2.0 接口:{UTMI|ULPI} 和 USB 3.0 接口:{PIPE3}

USB 测试套件 VIP 与 DUT 集成

除 USB 测试套件外,Synopsys 还提供适用于各种总线、接口和内存协议的测试套件。所有测试套件都易于集成和使用,并作为扩展和自定义的源代码提供。

审核编辑:郭婷

-

探索 EZ - USB™ FX3 相机套件:快速上手与功能解析2025-12-20 932

-

英飞凌AURIX™ TC3xx安全应用套件快速上手2025-12-19 868

-

Renesas 7542入门套件快速入门指南2023-04-28 825

-

瑞萨入门套件以太网和 USB 应用板快速入门指南2023-04-27 567

-

医疗仪表套件-快速入门指南2023-03-17 469

-

高级开发套件快速入门指南2023-01-30 691

-

SK hynix公司使用是德科技PCIe测试解决方案验证计算快速链路技术2022-04-24 2214

-

TSN评估套件快速入门指南2021-04-20 1305

-

基于C的测试和验证套件集成到常规UVM测试平台的方法2020-12-11 3175

-

快速搭建系统,快速连接硬件演示2019-04-09 4244

-

快速物联网原型套件的内部构成与应用2019-01-04 3258

-

CC2540 USB评估套件快速入门指南2016-03-17 1827

全部0条评论

快来发表一下你的评论吧 !