记录一下verilog重复例化的两种方式

电子说

1.4w人已加入

描述

1 for循环方式例化方法

先给出 sub_module

module sub(

input [7:0] din,

output logic [7:0] dout

);

assign dout = din;

endmodule

要将这个module分别例化成u_sub_0和u_sub_1,并且每个都例化四次

for循环的实现方式如下

module top(

input [8*4-1 : 0] din0,

input [8*4-1 : 0] din1,

output logic [8*4-1 : 0] dout0,

output logic [8*4-1 : 0] dout1

);

genvar i;

generate for(i=0; i<4; i++) begin:inst

sub u_sub_0 (

//output

.dout(dout0[i*8 +: 8]),

//input

.din(din0[i*8 +: 8])

);

sub u_sub_1 (

//output

.dout(dout1[i*8 +: 8]),

//input

.din(din1[i*8 +: 8])

);

end

endgenerate

endmodule

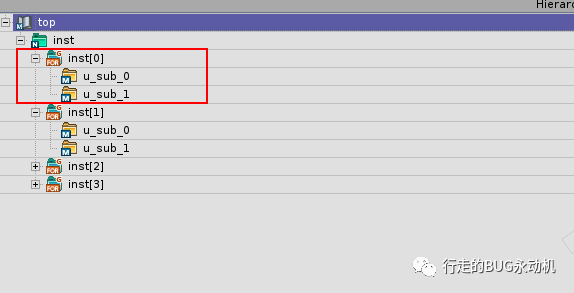

来看看例化后的效果

可以看到,总共4组inst,每组inst中存在两个u_sub

接下来点开inst[0]中的u_sub_0,看看它的信号是什么样的

依次点击,然后到shell界面粘贴内容

此时可以清晰的看到,这个din信号是来自哪里,这也体现了,在begin后命名block的重要性

2 数组的方式例化

同样的 sub_module,同样的例化要求,这次改用数组的方式进行例化

module top(

input [8*4-1 : 0] din0,

input [8*4-1 : 0] din1,

output logic [8*4-1 : 0] dout0,

output logic [8*4-1 : 0] dout1

);

sub u_sub_0 (

//output

.dout(dout0),

//input

.din(din0)

);

sub u_sub_1 (

//output

.dout(dout1),

//input

.din(din1)

);

endmodule

来看看这次的例化效果

在打印出这种方式的层次化结构

同样有清晰的辨识效果

4 一些其他的技巧

对于二维数组而言,如果想在verdi中将二维数组展开,那么我们需要在dump波形是加上这句话

$fsdbDumpMDA;

这样就可以在verdi中展开二维数组

当一个数组范围比较大不方便分析,可以将数组进行分段,操作如下

比如我要将32 bits位宽的din0信号分成8 bits位宽,可以这样设置

效果如下

实现了对信号的拆分

对于一些信号,在这种例化方式下拉信号的波形不是很容易(这个例子一时没想起来 >_<)

要拉出确定的波形可以这样操作

在波形界面按g,会弹出下面这个框

让后需要哪个信号选中即可添加

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

redis两种持久化方式的区别2023-12-04 1273

-

星三角的两种控制方式2023-05-05 1226

-

互锁正反转电路的两种实现方式2023-04-27 17024

-

MATLAB/simulink中两种实现建模方式的优势2022-09-15 6610

-

浅析标准的Verilog对语句有两种分组方式2022-09-14 1475

-

SQL语言的两种使用方式2021-12-20 2269

-

掌握原理图输入以及Verilog的两种设计方法2021-11-08 1915

-

开关量和模拟量是PLC初期使用最多的两种输入输出方式?2018-10-05 7530

-

请问IC设计中读写电路的设计中如何实现读写和连续读写两种方式?2018-07-18 2317

-

两种穿戴健身记录仪的方式2018-04-13 2348

-

开关磁阻电机两种绕组连接方式下铁心损耗的有限元计算2017-01-21 1132

-

两种verilog语言写法的实现问题!求解答~2015-01-29 4651

-

两种采样方式2013-08-08 1643

-

逆变器的两种电流型控制方式2009-07-10 4544

全部0条评论

快来发表一下你的评论吧 !