DDR VIP模型的无缝快速初始化

描述

DDR 验证是任何 SoC 中最关键和最复杂的任务之一,因为它涉及位于 DUT 内部的控制器和位于板载 DUT 外部的外部 DDR 存储器。在这里,我们将讨论 DDR VIP 模型的快速初始化。

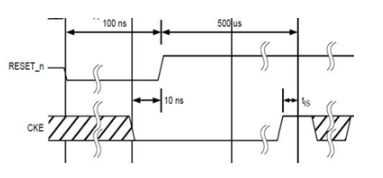

根据 JEDEC 标准 JESD79-4 第 3.3.1 节,RESET_n需要至少维护 200us。在模拟时间中,此值很长。此外,如果用户的测试平台违反此时间,Memory VIP 会将其标记为UVM_ERROR并失败模拟。即使此冲突被标记为错误,也不会影响 VIP 模型的行为。

有许多方法可以绕过此违规行为。在本博客中,我们将讨论其中一种方式。

Synopsys Memory VIP 具有称为快速初始化的初始化功能,也称为按比例缩小初始化。此功能的目的是允许控制覆盖初始化参数以加快初始化过程。新值(无论是默认设置还是由用户自定义)都可以缩短初始化时间,而不会断言任何检查器冲突。此外,它不会影响模型的初始化行为。此功能仅适用于前门访问 - 与后门访问相比。我们将在后续的博客文章中讨论内存 VIP 访问的类型。

有两种方法可以缩小初始化参数。一个是使用默认值设置的,另一个是自定义设置的。

根据标准,以下是预期值:

min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000000

min_reset_pulse_width_in_pu_ps = 200000000

使用默认方法,可以从配置对象的build_phase调用函数“set_scaled_initialization_timings()”。该函数调用会将计时参数缩小到下面分配的值,而不会触发检查器冲突:

min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000

min_reset_pulse_width_in_pu_ps = 200000

要自定义值,用户可以设置自己的自定义值,然后设置标志“scaled_timing_flag”。VIP 将配置为用户提供的值。因此:

对于分立器件:

|

// cfg handle of the svt_ddr_configuration class // Pass the cfg to the DDR Discrete Device component by using // the config_db mechanism. cfg.timing_cfg.min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000; cfg.timing_cfg.min_reset_pulse_width_in_pu_ps = 200000; cfg.timing_cfg. tPW_RESET_ps = 100000; cfg.timing_cfg.scaled_timing_flag = 1; |

对于内存型号:

|

// dimm_cfg is handle of svt_ddr_dimm_configuration foreach(dimm_cfg.data_lane_cfg[i]) begin foreach(dimm_cfg.data_lane_cfg[i].rank_cfg[j]) begin dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.min_cke_high_after_reset_deasserted_in_pu_and_res_init_time_ps = 500000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.min_reset_pulse_width_in_pu_ps = 200000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.tPW_RESET_ps = 100000; dimm_cfg.data_lane_cfg[i].rank_cfg[j].timing_cfg.scaled_timing_flag = 1; end end |

审核编辑:郭婷

-

DDR3初始化问题2018-06-21 7543

-

6657的DDR3初始化不成功2019-01-08 5760

-

如何从.mem文件初始化加密的ddr4内存模型?2020-05-11 2159

-

手机模块初始化向导2009-09-18 834

-

RDA1846S初始化设置2016-01-15 2313

-

UCOS_III_配置与初始化2016-12-20 1043

-

HX711初始化程序2017-02-08 2003

-

如何让KeyStone DDR3接口初始化的详细资料概述2018-04-28 1277

-

8253初始化程序分享_8253应用案例2018-05-23 23305

-

在51平台下初始化文件的引入导致全局变量无法初始化的问题如何解决2019-08-20 1433

-

C++之初始化列表学习的总结2020-12-24 1690

-

跳过DDR VIP模型的初始化2023-05-26 3012

-

DDR4-初始化、训练和校准2023-07-03 11941

-

GraniStudio:初始化例程2025-08-22 1015

-

ELF-RV112B RKNN模型加载与运行时初始化2026-04-03 145

全部0条评论

快来发表一下你的评论吧 !