如何在低功耗设计验证中尽早快速左移

描述

随着半导体行业向更小的工艺节点发展,静态功耗已成为主要的设计限制。这需要开发各种电源管理技术。例如,设计人员可能会创建多个电压域,或使用隔离单元将关断电源域与上电域隔离开来。他们可能会应用电平转换器在信号从一个域传播到另一个域时向上或向下缩放信号电压,或者使用保留单元在关断前更快地将寄存器返回到其状态。与用于指定设计功能意图的硬件描述语言 (HDL) 一样,实现这些技术需要一种通用语言来指定设计的电源意图:统一电源格式 (UPF)。

考虑到当今SoC的应用非常复杂且通常具有特定性,设计和实现所需功能以及时序和功耗要求的努力是巨大的。但仅仅实现这些目标是不够的。最终用户对在最短的时间内获得最新功能的永不满足的渴望给IP开发团队带来了压力。为了满足上市时间目标,芯片设计公司通常采用并行开发方法,其中不同的团队编写寄存器传输级别 (RTL)、Synopsys 设计约束 (SDC) 文件、UPF 文件等。

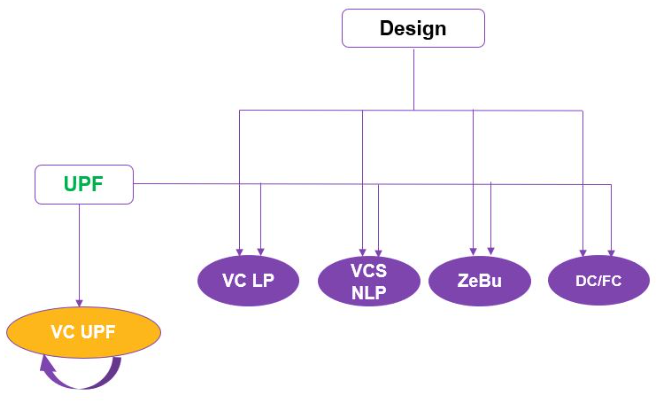

尽管设计和UPF的开发齐头并进,但它们的时间表可能会有所不同,这可能会导致一些挑战。在这篇博文中,我将解释如何使用 Synopsys VC LP™ 独立于设计的 UPF Checker (VC UPF) 克服这些挑战。请继续阅读,了解 VC UPF 如何让您在 RTL 准备就绪之前清理 UPF 文件中与设计无关的问题。

优化您的 SoC 电源设计

在设计 SoC 时,UPF 的第一个版本甚至在 RTL 最终确定之前就已经准备就绪。除非设计准备就绪,否则无法验证UPF的准确性和完整性。因此,通常有一个窗口,编写UPF的工程师只是在等待RTL第一次切割的关闭。一旦设计准备就绪,工程师就会运行一个静态检查工具来验证UPF与设计的关系,这时他或她意识到UPF中存在一些基本问题,即使不阅读设计,这些问题也可能被捕获。不幸的是,在这个过程中已经浪费了一些时间。UPF 修复和检查的多次迭代会导致较长的周转时间!

这就是VC UPF来拯救的地方。

顾名思义,VC UPF 使电源意图所有者能够在 RTL 准备就绪之前清理 UPF 文件中与设计无关的问题。该解决方案包括:

UPF 语法和语义检查

基于UPF供应分析的检查

PST 一致性检查

UPF 网络相关一致性检查

基于允许/不允许的命令和选项的方法特定检查

让我们看几个例子来了解这如何提供帮助。

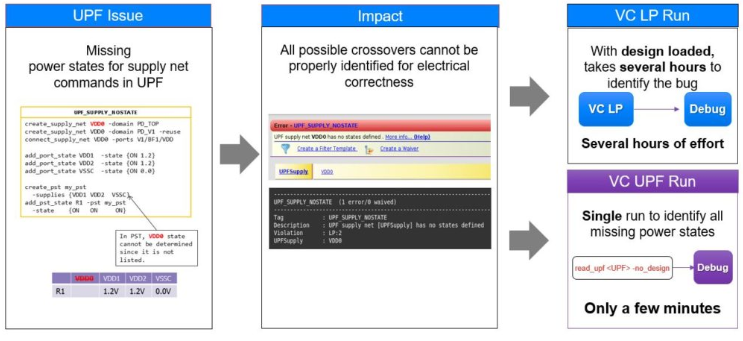

考虑UPF供电网络未定义任何电源状态的情况。只有在阅读设计、加载 UPF 并完成 UPF 检查后,用户才会意识到,由于缺少状态,有些交叉无法进行分析。使用 VC UPF,此信息将在几分钟内提供。

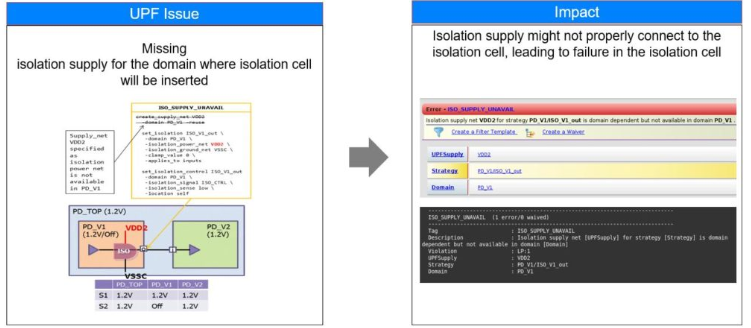

在另一种情况下,隔离策略的隔离电源网络可能在所需域中不可用。

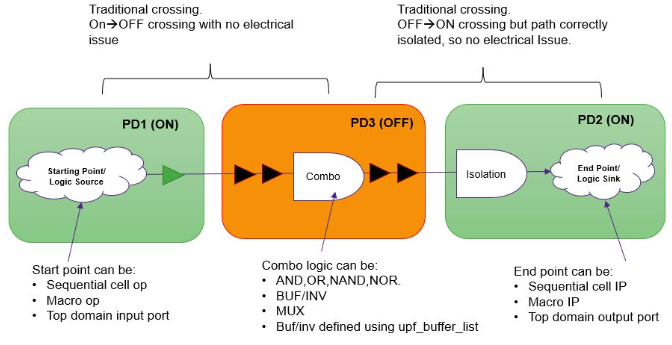

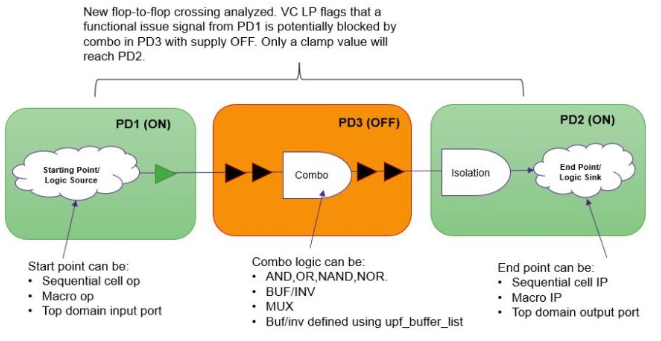

这是另一个例子。考虑从 PD3 到 PD2 的路径。没有电气问题,因为OFF-》ON交叉路口由隔离单元正确保护。因此,传统的电气检查不会标记任何违规行为。但在同样的情况下,存在一个功能问题,即来自 PD1 的信号被 PD3 中的组合阻挡,该组合已关闭电源。

VC LP 中的新高级检查正确标记了问题,并提醒设计人员,尽管路径已正确隔离,但来自 PD1 的信号被 OFF 域中的组合阻止,只有箝位值才能达到 PD2。

根据违规情况,设计人员应验证路径是否旨在在指示的电源状态期间携带功能信息。如果它在给定电源状态下不起作用,则无需进一步操作。另一方面,如果路径正常工作,则需要打开指示的缓冲器/逆变器/组合,并且需要修复与组合的电源连接。通过仿真识别这些问题非常耗时,但借助 VC LP,您现在可以在设计周期的早期发现这些问题,并节省仿真时间。

虽然VC UPF的主要动机是早期清理UPF,但它也可用于SoC的UPF管理。 复杂的SoC具有来自不同供应商/组的IP块的UPF文件,这通常会导致UPF修改延迟以及计划和重新验证延迟。为了避免这种情况,CAD 团队可能会强制执行一些引导软件规则,以符合 IP 供应商的 UPF 可交付成果,以实现平稳的 SoC 集成。VC UPF 可以帮助使用 disallow_* 命令或 allow_* 命令执行此类指南软件 UPF 构造检查。

同样,在 SoC 集成期间,您可能不希望从顶部覆盖特定的 IP 级 UPF TCL 变量。带有设计检查工具的标准UPF永远不会认识到这是一个问题。但是使用 VC UPF,您可以指定此类受保护变量的列表,并快速找出其中是否有任何变量已被顶级 UPF 覆盖。还可以验证 IP 的 UPF 版本与 SoC UPF 的兼容性。根据有关允许和不允许哪些 UPF 版本组合的用户指南,VC UPF 可以执行 IP 与 SoC 一致性检查。请注意,否则,VC LP 与 UPF 版本无关,并且“upf_version”没有后果。

经过生产验证的功耗感知静态检查签核

Synopsys VC LP 解决方案为 UPF 提供准确且经过生产验证的支持,与其他用于静态低功耗检查和调试的工具紧密集成:

Synopsys Verdi® 自动化调试系统提供事实上的行业标准工作流程、界面和调试功能。

Synopsys IC 编译器™ II 布局布线解决方案使用 VC LP 工具在设计周期的早期识别 UPF 和相关违规行为。IC 编译器 II 命令可用于修复发现的冲突。

Synopsys VC 正式™的下一代形式验证解决方案提供功耗感知连接检查。

总结

不言而喻,设计满足所需功能、时序和功耗要求的低功耗 SoC 需要付出很多努力。这项事业也面临着严格的上市时间压力。通常,芯片设计公司选择并行开发方法,其中不同的团队编写 RTL、设计约束文件、UPF 文件等。但是,虽然设计和UPF的开发可能齐头并进,但它们的时间表可能会有所不同。

VC LP 解决方案使电源意图所有者能够在 RTL 准备就绪之前清理 UPF 文件中与设计无关的问题。该解决方案还可用于 SoC 的 UPF 管理,因为复杂的 SoC 通常具有来自不同供应商的 IP 的 UPF 文件,这可能会导致 UPF 修改延迟以及计划和重新验证延迟。由于能够尽早清理UPF,工程师可以在低功耗SoC设计周期中节省时间和精力。

审核编辑:郭婷

-

如何在 RTOS 中处理微控制器的低功耗特性2025-12-12 84

-

请问DTU如何在低功耗下正常收发数据?2024-07-25 3168

-

X态传播在低功耗验证中的作用2024-01-24 1562

-

新唐蓝牙低功耗MCU带你快速实现摄影灯光应用2023-08-10 1331

-

如何在DDR中完成imx8m低功耗管理?2023-04-07 461

-

如何在低功耗模式下使用SPC560bxx中的RTC呢?2022-12-22 477

-

如何在低功耗Bluetooth® PEPS系统中添加CAN节点2022-11-09 669

-

如何在汽车设计中降低功耗2022-11-04 735

-

选择性唤醒的控制器局域网收发器如何在汽车设计中降低功耗2022-10-28 591

-

如何在RTOS中处理微控制器的低功耗特性2022-04-19 2239

-

【NUCLEO-L552ZE-Q开发板试用连载】低功耗智能电表验证2020-03-11 1546

-

CPF低功耗解决方案在在低功耗验证过程中应用分析2019-09-06 7038

-

低功耗ADC的低功耗参考和双极电压调节电路精密验证设计2018-11-15 3243

-

低功耗蓝牙怎么低功耗?如何界定2018-02-06 3733

全部0条评论

快来发表一下你的评论吧 !