3分钟了解ePort关键设计技巧

电子说

1.4w人已加入

描述

ePort-M模块到手,通信接口不了解?TX线需要串接电阻?信号线不懂处理、走线麻烦?3分钟带你了解ePort关键设计技巧,轻松上手!

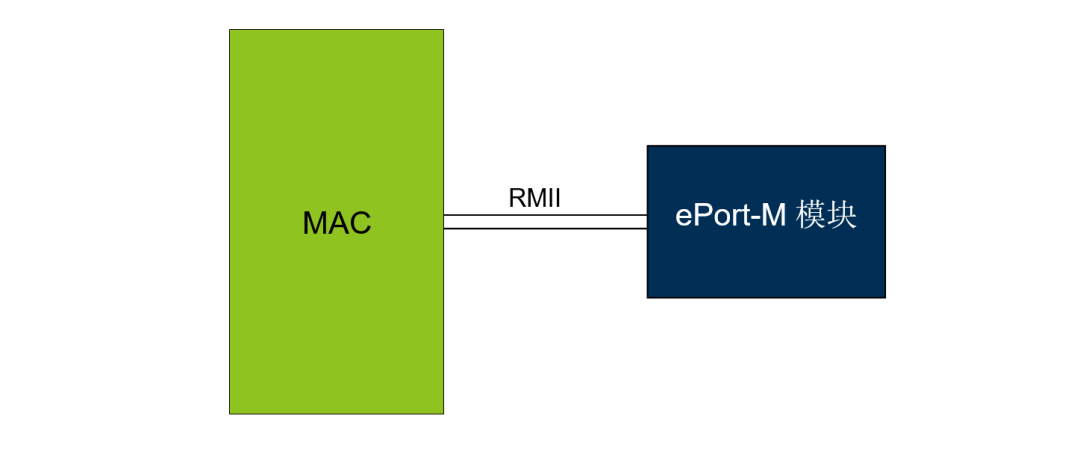

通信接口了解

通信接口了解ePort-M百兆以太网模块采用了RMII接口(精简的独立于介质接口),相比较于MII接口(媒体独立接口),RMII通信所需要的引脚数更少,根据IEEE802.3标准,MII接口需要16个信号引脚,RMII接口则只需要7个信号引脚,此时ePort-M模块的时钟信号频率为50MHz,该时钟信号由MAC端提供或外部时钟源提供。

ePort-M模块简单易用,然而应用到产品时,如何保证模块的正常通信,提高模块的的通信质量呢?下面介绍如何进行ePort-M模块的原理图设计以及PCB设计。

原理图设计

原理图设计

PCB设计

PCB设计

1、ePort-M模块PCB布线时,发送信号RMII_TXEN、RMII_TXD0、RMII_TXD1串联的22Ω电阻需要靠近MCU放置;

2、以太网的信号线需要控制单端50Ω阻抗匹配,避免信号传输过程出现反射以及过冲;

3、PCB走线保证TXD组内100mil等长,RXD组内100mil等长处理,模块内部TXD/RXD组已做等长处理,因此在处理等长时,无需考虑ePort-M模块内部的走线长度;

4、以太网复位信号是敏感信号,PCB走线距离MCU应尽量短,并且远离其他高速信号;

5、在条件允许的情况下,以太网时钟信号线两侧需要进行包地处理,包地线应该尽量粗,同时包地线上应该多打地孔,以减少时钟信号线与其他信号线之间的串扰。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

3分钟以内可调的延时电路2009-09-22 10487

-

3分钟带你了解博智慧达激光焊缝跟踪技术2019-08-30 4974

-

3分钟到4小时定时器2007-12-13 2121

-

3月12日将用3分钟搞定vivo真我X50 Pro的线上发布2020-03-04 5030

-

3分钟了解嵌入式的硬件构架资料下载2021-04-04 931

-

10分钟深入了解电路噪声资料下载2021-04-08 932

-

如何3分钟理解通信协议系列2021-11-21 10479

-

1分钟了解天线方向图核心信息2022-03-19 22005

-

ePort-M模块的原理图设计以及PCB设计2022-09-23 2542

-

3分钟了解ePort关键设计技巧2022-09-26 2327

-

【深度解析】你知道我们的ePort模块经历了多少刀山火海才能交付客户吗?2023-03-18 1920

-

【产品应用】3分钟了解ePort关键设计技巧2023-06-06 2774

-

快速了解ePort-G(1.8)的关键设计技巧2023-09-06 2798

-

快乐解说MCU:三分钟,带你了解低功耗MCU2023-09-18 2521

-

三分钟了解飞创直线电机运动模组特点、选型及应用-FCL系列2024-02-05 1644

全部0条评论

快来发表一下你的评论吧 !