电源设计对RF放大器相位噪声的影响

电源/新能源

描述

如今的射频(RF)系统变得越来越复杂。高度的复杂性要求所有系统指标(例如严格的链接和噪声预算)达到最佳性能。确保整个信号链的正确设计至关重要。

而信号链中,有一个部分经常会被忽视,那就是直流电源。它在系统中占据着重要地位,但也会带来负面影响。RF系统的一个重要度量是相位噪声,根据所选的电源解决方案,这个指标可以优化。本文研究电源设计对RF放大器相位噪声的影响。

什么是相位噪声?

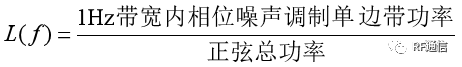

正弦波瞬时相位Φ(t)=ωt+φ(t)=线性相位ωt+随机相位φ(t),随机相位φ(t)的功率谱就是相位噪声谱,归一化后用功率谱密度表示。

相位噪声采用相对值表示:

相位噪声相当于一个噪声源对正弦波进行相位调制,若相位噪声较小,则调相指数(最大相偏)很小,φ(t)的功率谱与正弦波的功率谱相差不太大,所以用频谱分析仪测正弦频谱时,只能大致能观察相位噪声(但不准确,而且频谱分析仪的动态范围偏小)。

相位噪声中,窄带分量就是杂散。

信号链的DC电源解决方案是导致相位噪声的一个重要成因,但它常被忽视。为信号链供电的电源轨上的任何噪音或波纹都可能在内部耦合。这会导致相位噪声增加,从而可能隐藏发送的带宽中的关键频率分量,或从载波中引入杂散偏移。这些杂散靠近载波,所以特别难处理,且因为严格的过渡频带要求,给滤波器造成很大挑战。

在进行信号链分析时,必须考虑到所有噪声来源。DC电源解决方案这个噪声源常常被忽视掉,这可能会影响和严重降低信号链的性能。

这种有规律的,不管频率怎么变,间隔不变的就是电源杂散。

电源解决方案

DC-DC是最大的共模干扰源,很难用滤波的方法去抑制,处理共模干扰的唯一办法:共模电感。

LDO的目的是抑制纹波,抑制低频噪声,要求LDO的PSRR高,带宽大。能够抑制DC-DC的高次谐波,一般的LDO,PSRR抑制频率高端不到1MHz,好的LDO可达10MHz。

如果要求晶振、VCO低相位噪声、低杂散,那么电源必须是低噪声电源,LDO必须与其他电源LDO分开,单独供电,保证DC高频有必要的隔离度。晶振、VCO的电源功耗十分相近,大约1530mA,VCO的频率很高,退耦电容47470pF即可。VCO、晶振可以共用电源,用小电阻2.210进行隔离,加足够的退耦。

VCO电源

PLL、DDS

PLL、DDS含有数字和模拟部分,是数模混合电路,数、模电源之间要解决电源的隔离,大电流通过功率电感增加交流隔离,小电流通过电阻增大电源间隔离,DC及交流均隔离较好,防止数模串扰,降低杂散。

数模电源隔离

噪声不仅会因为电源选择的不同而大不相同,而且可能受到输出电容、输出电压和负载影响。应当仔细考虑这些因素,尤其是对于敏感的供电轨。

-

RF2373低噪声放大器/驱动放大器Qorvo2023-12-28 8489

-

如何选择最好的电源解决方案,以提高RF信号链相位噪声性能2023-06-15 2282

-

浅谈QORVO低相位噪声放大器的特点以及应用2020-11-12 1516

-

Custom MMIC低相位噪声放大器的主要特性及应用2020-11-06 1094

-

RF5515 放大器2018-06-21 1245

-

RF低噪声放大器设计2017-11-23 3465

-

放大器的电源电阻和噪声考虑因素2017-03-05 571

-

高性能RF/IF放大器设计2012-05-09 1709

-

放大器噪声的来源2011-11-24 3725

-

放大器的噪声2010-07-01 1041

-

RF放大器,RF放大器主要参数有哪些?2010-03-22 5478

-

低噪声放大器,低噪声放大器是什么意思2010-03-05 4033

全部0条评论

快来发表一下你的评论吧 !