AMBA向多芯片和CHI C2C进发

处理器/DSP

描述

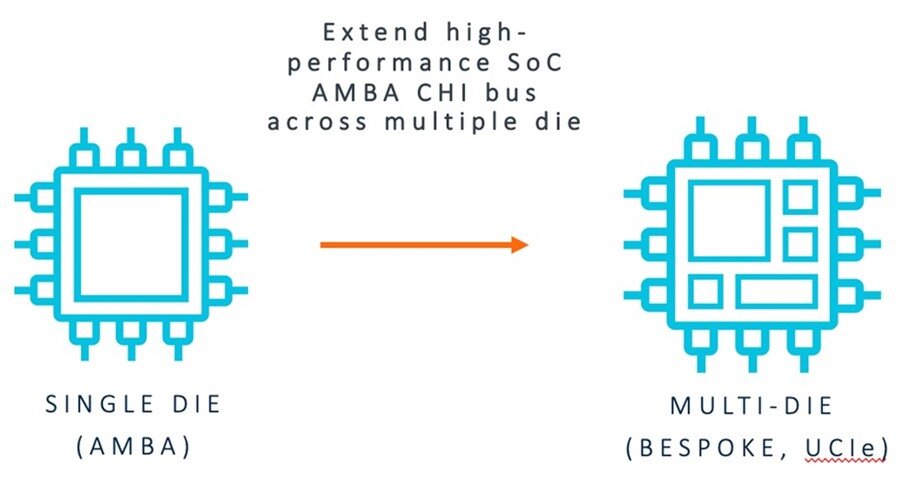

Arm的Advanced Microcontroller Bus Architecture(AMBA)在与生态系统合作解决复杂的行业性问题方面有着悠久的历史。现在,随着行业接纳芯粒(chiplets)技术,是时候将AMBA从片上扩展到多芯片了。

在这篇博客中,我们将概述AMBA Coherent Hub Interface(CHI)芯片互联(chip to chip, C2C)的方法——这是对片上CHI的扩展,旨在使CHI适用于芯片间互联。

我们还将说明AMBA CHI C2C如何努力与UCIe等芯片片间标准化相辅相成,以进一步推动协作。

为什么选择芯粒,为什么是现在?

正如我们在以前的博客文章中讨论过的那样,行业正处于一个拐点,芯粒正在在各个领域和应用中得到采用。

对芯粒的投资是由当前在SoC设计中所面临的巨大经济压力推动的。SoC的复杂性和性能要求不断增长,而每个新的先进制造工艺节点(5纳米及以下)的成本也在增加。然而,这些新节点带来的好处并没有相应增加。例如,虽然逻辑的面积持续缩小,但I/O和存储器的收益却递减。高昂的成本也阻碍了新SoC或衍生产品的数量。

这种情况为芯粒提供了绝佳的机会。芯粒使得在当前被芯片尺寸限制的性能上进行扩展成为可能,同时管理芯片成本并提供更大的可组合性。

标准化至关重要

AMBA一直是片上通信的开放标准。AMBA为各种设计提供了一个共同的标准,确保了SoC中不同组件之间的兼容性。它为设计集成提供了灵活性、可扩展性、设计复用性。

AMBA规范(如CHI和AXI)是免费提供的,并与行业各方合作共同开发。AMBA被广泛应用于Arm生态系统及其他领域。它具有长期可靠性和信任度,在过去27年中已经在数十亿台设备中使用,涵盖了各个市场和应用领域。

AMBA所带来的标准化是支撑SoC设计和无厂(fabless)半导体模式的基础。这种标准化构建了一个繁荣的生态系统和一个兼容IP和工具的综合市场。其中包括处理器、加速器、互连、控制器、外设,以及来自芯片合作伙伴、IP供应商和其他合作伙伴的验证IP(VIP)、建模工具和性能工具。

标准化对于芯粒同样至关重要。随着行业从当前的定制芯片互联转向多供应商可组合芯片互联,标准化将变得更加重要。

具有标准化明确定义和可互操作的层也至关重要。

明确定义和可互操作的层可以实现设计复用,降低成本和上市时间。不同的实现可以优先考虑和关注不同的用例和需求,提供更大的灵活性并促进创新。

芯粒需要物理、传输和协议层的标准化。更不用说软件模型、机械、热管理和功耗的标准了。还需要进行芯片验证、可靠性测试、合规性测试和许多其他方面的工作。

为什么选择AMBA CHI?

AMBA CHI架构提供了处理器、加速器和存储器等大型网络所需的性能和扩展性。

更重要的是,CHI是高速、可靠且分组化的,这使其也非常适用于芯粒。同时,CHI是广泛使用的开放标准,为芯粒提供了低风险和简单的利用方式。

CHI协议提供了一个完整的缓存一致性模型,与架构无关,支持用于使用snoop filter和directory-based 的系统。它公布于2013年,并不断发展,增加了新功能和性能提升。其广泛的功能列表包括:

- 原子和互斥事务 (Atomic and exclusive transactions)

- 用于降低延迟的优化流程,如DMT、DCT和DWT

- 基于奇偶校验的接口保护

- 低功耗,具有不同级别的控制

- 写入零、数据省略和本地复制 (Write zero, data elision and copy-at-home),以减少数据传输

- Distributed Virtual Memory(DVM)管理

- 用于机密计算的领域管理扩展(Realm Management Extensio,RME)

CHI作为基础设施应用程序在超大规模计算、服务器和网络领域取得了极大的成功。CHI现在已经广泛应用并在其他多个市场领域中得到验证,例如移动和汽车领域,这些领域也需要完全硬件一致性和高性能。

引入AMBA CHI C2C

我们很高兴介绍AMBA CHI C2C,这是CHI的扩展,用于芯片片间互联(chiplet-to-chiplet)。

通过C2C,即芯片片间互联(chiplet-to-chiplet),我们指的是芯粒(multi-die或die-to-die)和芯片间连接(multi-chip通过PCB连接)。

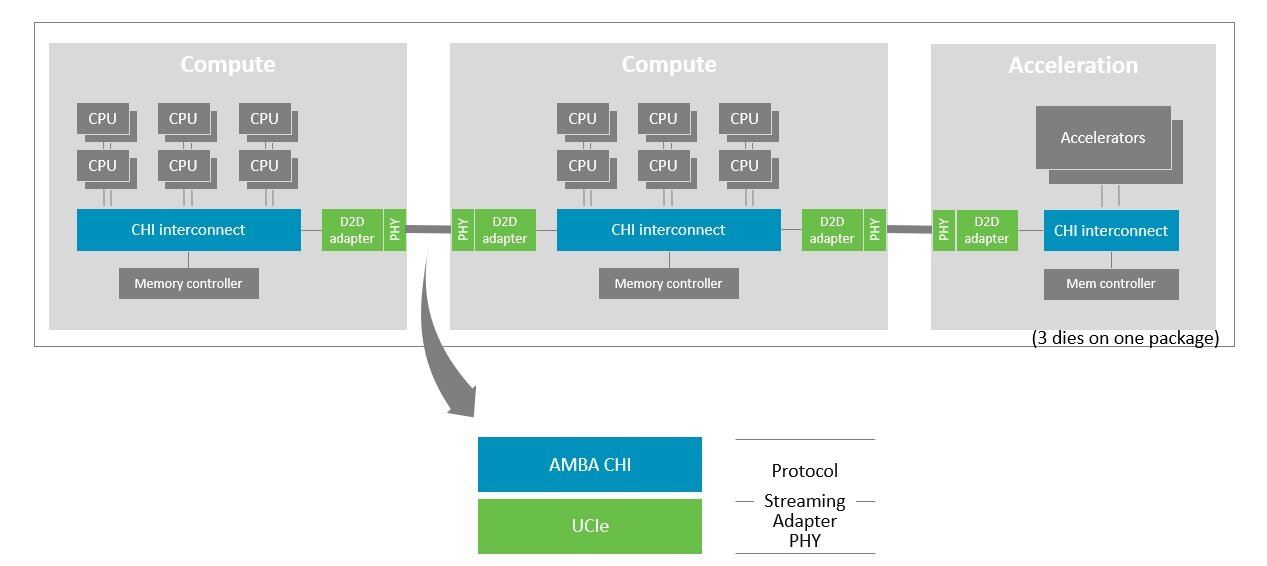

CHI C2C针对先进的异构系统,和基于Arm的一致性SMP。它提供了一个统一的设备连接接口,包括计算、加速器和存储器。不仅用于全一致性传输,也用于I/O和非一致性传输。

CHI C2C专注于协议(protocol )和信息打包(packetization )层。CHI C2C利用现有的片上CHI协议,并定义了如何对其进行信息打包,使其适合通过芯片片间互连进行传输。包格式针对链路利用率和延迟进行了优化,同时避免了复杂的打包和解包方案。

相同的架构特性可以跨越芯片间的边界,芯片之间可以共享相同的存储器和安全模型。这可以避免协议转换、不兼容性和额外的延迟。

这种分层的方法可以与底层传输进行清晰的分离,因此CHI可以在UCIe或其他方式上使用,无论它是否标准化。

使用CHI和UCIe streaming

UCIe已经汇集了行业领导者,提供了标准化的芯片片间接口,并取得了很大的动力。它提供了适用于芯片片间集成的物理层(PHY)和适配器(adapter),以及软件模型和合规性测试。

UCIe还提供了优秀的协议灵活性。它采用了多协议栈方法,允许在单个物理链路上使用多个协议。PCIe和CXL可用于传统的片外设备,而Streaming接口可用于插入其他协议,使其非常适合传输AMBA CHI。

下面我们以使用UCIe Streaming的基于CHI的多芯片系统为例进行说明。它具有重要的优势:

- 无缝使用架构特定功能--通过与片上系统一样的CHI协议的传输,可以无缝使用架构特定功能,无需协议转换。

- 链路稳定性--UCIe Streaming 接口提供了链路稳定性,例如使用UCIe定义的数据链路CRC和重传机制。

总结

CHI C2C规范正在开发中,和其他所有AMBA规范一样,将按照现有的AMBA许可和治理模型进行发布。也就是说,它将免费提供,免版税,与架构无关,并具有广泛和永久的实现权利[1],换句话说,非常适合广泛采用。

通过利用现有的AMBA许可和治理模型,CHI C2C将能够与CHI协议本身保持同步发展,并与现有AMBA生态系统的要求保持一致。当然,我们确保它仍然针对UCIe和其他传输进行优化。

该模型遵循分层的标准化方法和其他协议的现有治理模型,例如CXL和PCIe,也可以与UCIe一起使用。

基于此,我们预计CHI C2C将在各个领域和应用中得到应用。从高性能基础设施应用到汽车领域等,随着时间的推移,还包括现有的大量基于AXI的设计,这对于在C2C中进行启用至关重要。

-

AMBA CHI协议介绍2023-08-02 1570

-

SoC Designer Plus AMBA CHI协议包的用户指南2023-08-17 833

-

百度C2C进入上线敏感期 酝酿与淘宝全面开战2008-09-10 981

-

个人网上拍卖模拟实验(C2C模块)2009-03-18 3907

-

杭州市将建C2C电子商务创业园2009-11-21 1097

-

基于C2C模式的淘宝管理系统设计分析2017-11-03 1160

-

基于信任网络的C2C电子商务信任算法2018-01-26 1413

-

c2c交易平台系统开发,深圳数字资产c2c交易平台搭建商2018-07-06 812

-

okex模式平台c2c交易平台开发,深圳专业c2c交易平台开发搭建公司2018-07-10 6268

-

c2c交易平台虚拟货币模式开发2018-07-12 876

-

C2C交易平台搭建,交易所源码开发,区块链系统开发2018-10-23 1285

-

区块链usdt支付系统C2C支付通道搭建2019-02-12 2399

-

缓存一致性验证 – AMBA CHI中的新功能2023-05-25 2981

-

推动AMBA向多芯片和CHI C2C发展2023-11-23 1965

-

Arm和新思科技继续就AMBA协议系列的最新扩展密切合作2024-05-15 2758

全部0条评论

快来发表一下你的评论吧 !