HME FPGA入门指导:HME-P(飞马)系列开发板实验教程——LED流水灯

描述

一实验目的

熟悉 HME FPGA PLL IP 的使用,实现 LED 流水灯功能

二实验环境

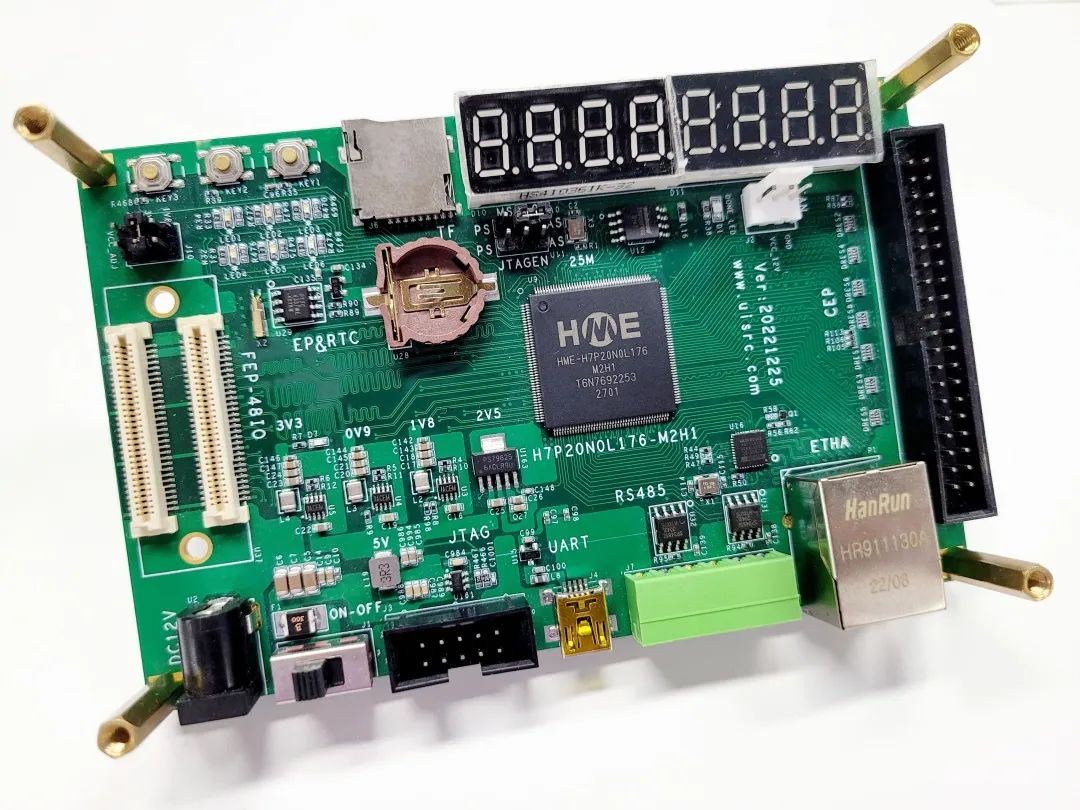

IDE:福晞Fuxi、开发板:P0 176

HME_P0 176 开发板

三实验原理

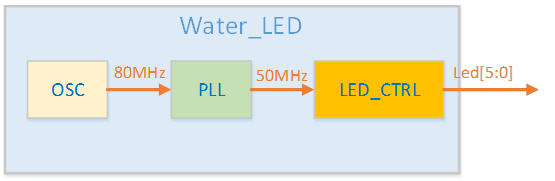

3.1 实现框架

3.2 实验功能分析

使用 P0 内部 OSC 作为时钟源,通过 PLL 锁相环输出 50MHz 的时钟作为 LED 的控制时钟,依次点亮板载的 6 个 LED 灯,实现流水灯的效果。

每个 LED 灯一次点亮持续时间 0.5s,通过分时控制每个连接到 LED 灯的 I/O 电平的高低来实现。如 LED 的控制时钟是 50MHz(T=20ns),需要通过一个计数器来计数,当计数器的值是25000000时改变 LED 亮灭状态。

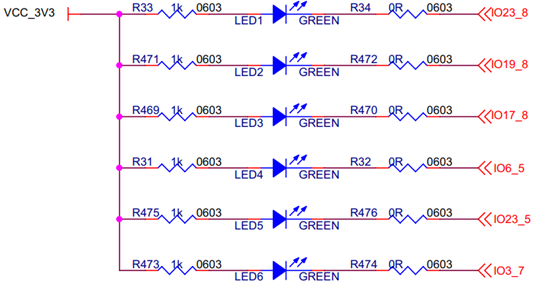

LED 部分原理图如下:

四OSC 与 PLL 使用

4.1 P0 OSC 使用

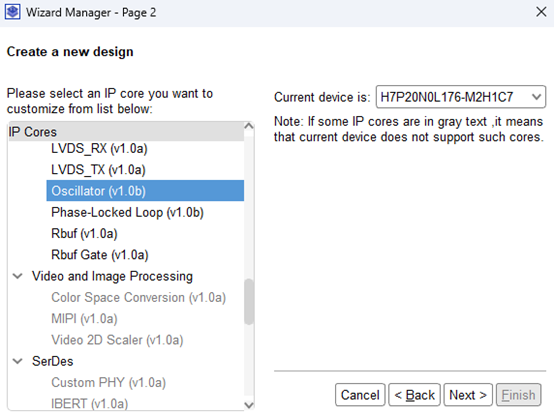

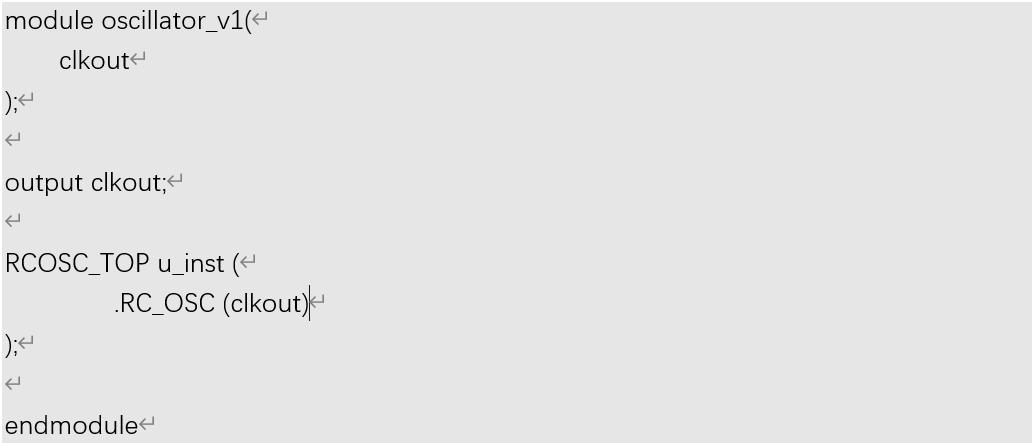

P0 内部有精准的 RC-OSC 时钟发生器,输出 80MHz 可作为系统的时钟源。rtl 代码可通过 Fuxi IP Wizard 将其例化出来使用,如下图:

创建出IP的代码如下:

4.2 P0 PLL 锁相环简介

锁相环路是一种反馈控制电路,简称锁相环(PLL,Phase-locked Loop)。利用外部输入的参考时钟信号控制环路内部振荡信号的频率和相位。

HME 系列产品的 PLL 模块能够提供可以综合的时钟频率,通过配置不同的参数可以进行时钟的频率调整(倍频和分频)、相位调整、占空比调整等功能。

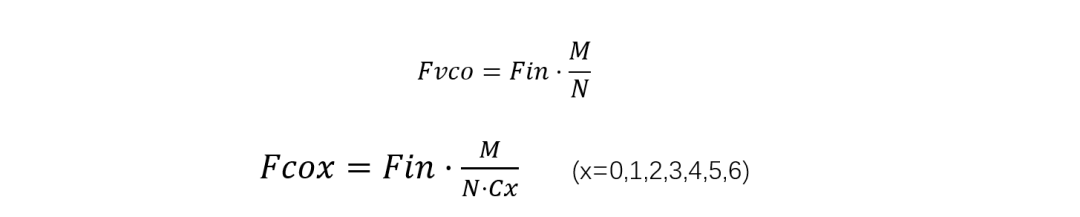

PLL 可对输入时钟 CLKIN 进行频率调整(倍频和分频),计算公式如下:

FIN=输入时钟,可以是外部时钟,也可是芯片内部的 osc 时钟;后面会讲述内部 osc 的使用方法。

N=CFG_DIVN [6:0]+1

M=CFG_DIVM [6:0]+1

Cx=CFG_DIVCX[6:0]+1

N、M、Cx 为 PLL 的参数,IP 会自行推到计算。

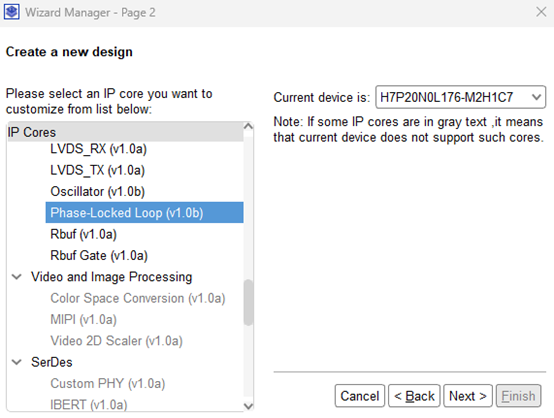

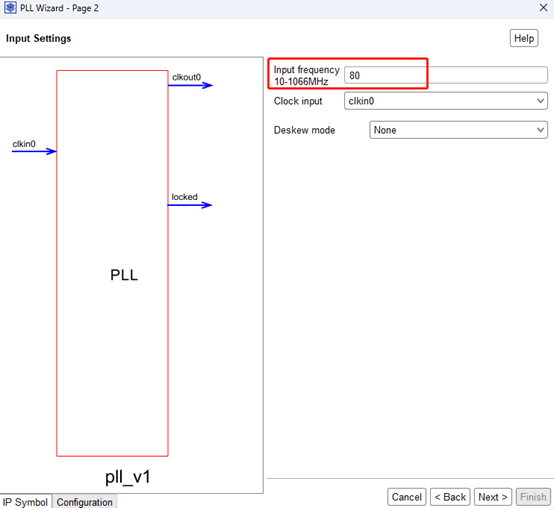

4.3 PLL IP 使用

通过 IP Wizard 创建 PLL

Input Frequency 是 PLL 的输入频率,这里配置为 80MHz,是因为这里将 oscillator_v1 IP 实例的 clkout 80MHz 作为 PLL 的输入时钟。

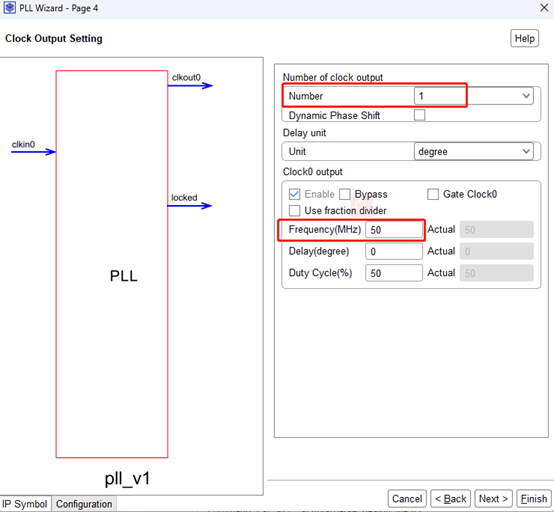

如下图所示,选择了1个时钟输出通道,输出频率 clkout0 为 50MHz,将该时钟作为逻辑的系统时钟;locked 信号一开始为低电平,当各输出通道的时钟稳定后变为高电平;可利用该特性将 locked 信号作为系统的复位信号。

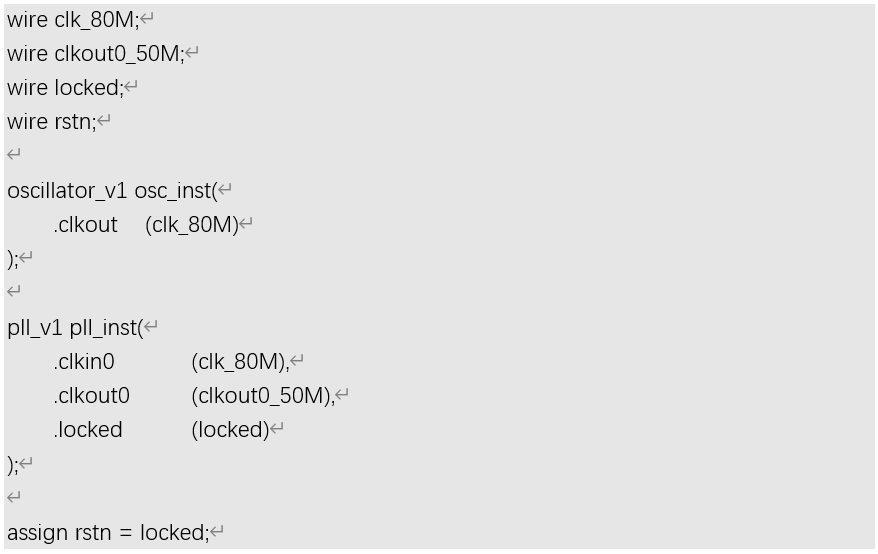

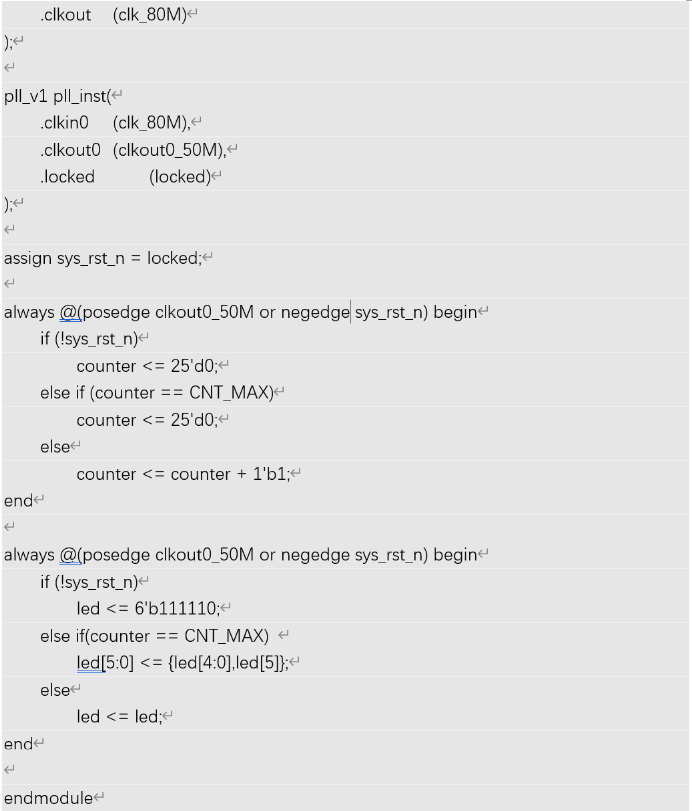

实例化 PLL 的 rtl 代码如下:

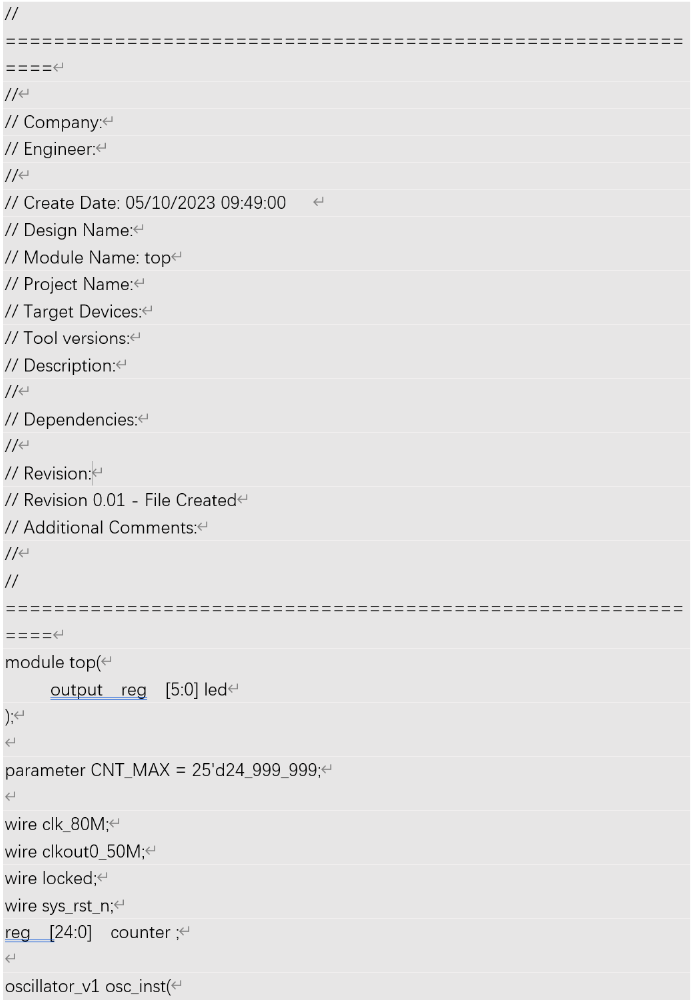

五RTL 功能实现

时钟源使用 P0 内部 osc 时钟 80MHz,osc 时钟作为 PLL 的输入,PLL clkout0 输出50MHz 时钟作为逻辑设计的系统时钟。通过计数器控制每个 LED 点亮持续 0.5s 并形成流水效果。

5.1 RTL Design

5.2 实验现象

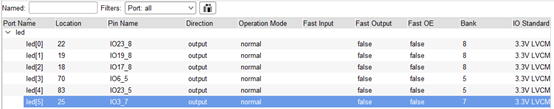

5.2.1 I/O 约束

综合编译检查是否存在语法问题;通过后进行I/O约束;

如下图:

5.2.2 生成码流与下载

然后执行 Generate Bitstream 生成码流文件,下载至 P0 开发板进行验证。

6 个 LED 灯按照设定的顺序和时间依次点亮和熄灭,说明 PLL 输出时钟和逻辑设计符合预期。

审核编辑:汤梓红

-

国产FPGA简介2023-11-20 939

-

基于LABVIEW零基础学习开发板实验指导手册2021-03-25 4979

-

【Runber FPGA开发板】配套视频教程——LED流水灯实验2021-04-12 2628

-

【Runber FPGA开发板】配套视频教程——键控流水灯实验2021-04-13 2577

-

51单片机流水灯实验报告.doc2021-07-21 5820

-

如何上手FPGA实现简单的流水灯效果2022-01-18 1712

-

LED流水灯实验的相关资料推荐2022-01-21 4350

-

紫光同创FPGA入门指导:键控流水灯——紫光盘古系列50K开发板实验教程(2)2023-04-20 1120

-

实验教程:LED 流水灯 ——紫光盘古系列高性能入门级2K开发板2023-06-26 2249

-

【紫光同创国产FPGA教程】【PGC1/2KG第二章】LED 流水灯实验例程2023-08-09 1363

-

采用FPGA DIY 开发板实现8个流水灯向左移功能2018-06-20 6345

-

京微齐力HME-P1P60 FPGA荣获年度最佳处理器/FPGA奖项2021-03-23 3191

-

C语言入门开发板实验指导电子版下载2021-03-24 950

-

C51单片机实验——LED流水灯2021-11-21 3254

-

CVI实验指导(八)Lab WindowsCVI制作流水灯2022-01-17 1277

全部0条评论

快来发表一下你的评论吧 !