半导体工艺装备现状及发展趋势

描述

集成电路前道工艺及对应设备主要分八大类,包括光刻(***)、刻蚀(刻蚀机)、薄膜生长(PVD-物理气相沉积、CVD-化学气相沉积等薄膜设备)、扩散(扩散炉)、离子注入(离子注入机)、平坦化(CMP设备)、金属化(ECD设备)、湿法工艺(湿法工艺设备)等。

集成电路前道工艺及设备的标志性指标为集成电路的特征尺寸,主要沿摩尔定律方向持续延伸,根据国际器件与系统技术路线图IRDS(2021),集成电路前道关键工艺、器件结构对应的设备加工技术能力将由当前的5 nm、3 nm发展到2.1 nm、1.5 nm直至等效1 nm、0.7 nm技术节点,如表1所示。

表1集成电路逻辑器件技术路线图[1]

近期(2021-2025):FinFET晶体管结构继续延伸,由5 nm直至3 nm、2.1 nm节点。 为进一步提升栅极控制能力,从3 nm节点开始, LGAA(Lateral gate-all-around,水平围栅)结构开始引入并逐渐替代FinFET结构,相应的制造设备应该随之进行技术迭代,支撑到这个制造节点的要求。

中期(2026-2030):晶体管全面进入2.1 nm以下节点,根据IRDS(2021)规划,2.1 nm和1.5 nm这两个工艺节点预计将分别在2025年和2028年出现。 LGAA晶体管结构可以继续支撑这两个制造节点的要求,相关制造设备需要根据工艺特征尺寸缩小的要求做进一步提升。

远期(2031-2035):晶体管进入等效1 nm工艺节点和等效0.7 nm工艺节点,晶体管的工艺特征尺寸达到极限,多层垂直堆叠的LGAA晶体管结构将成为下一步发展方向。 单片三维堆叠工艺及设备技术将是这个阶段的主要需求。

主要技术挑战

(1)EUV光刻设备。 光刻技术直接决定了集成电路的特征尺寸(光刻线宽与***曝光波长成正比,与成像系统数值孔径呈反比),是摩尔定律演进的核心驱动力之一。 传统的193 nm***在经历了“浸没式技术”及“多重曝光”两次重要技术升级后,已经大规模应用在10 nm节点集成电路制造中。 进入7 nm以下节点,虽然193 nm浸没式光刻+多重曝光从技术上仍然可以满足集成电路制造的需求,但工艺复杂度直线上升,造成了难以解决的良率和成本问题。 因此,采用13.5 nm极紫外光源的EUV***成为7nm及以下集成电路大生产首要选择,在7 nm节点,EUV光刻工艺步骤是193 nm浸没式光刻的1/5,光刻次数是后者的1/3[4]。

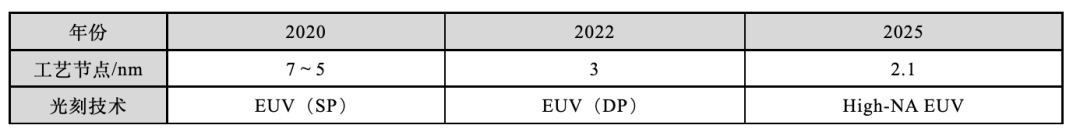

当前EUV***已经在产线批量应用并支持7~5 nm节点的工艺制程要求。 随着摩尔定律继续延伸,EUV光刻主要是按照两个方向演进:一是由单重曝光(Single Patterning, SP)发展至双重曝光(Double Patterning,DP); 另一个就是提高EUV数值孔径(High-NA EUV)。 根据IRDS光刻技术发展路线图预测,在3 nm节点(2022年),集成电路大生产将采用双重曝光EUV技术; 在2.1 nm节点(2025年),集成电路大生产将采用高数值孔径EUV技术,如表2所示。

当前ASML正在研发第二代EUV***,数值孔径将由现在的0.33提升至0.5,同时不断提升光源功率,预计量产时间为2024年,将支撑2025年之后集成电路制造的需求。

表2 光刻技术发展路线图

(2)GAA(围栅晶体管)制备设备。 GAA(Gate-All-Around)晶体管将是继FinFET后的下一代晶体管结构。 相对于FinFET的三面栅控结构,GAA晶体管沟道为水平或垂直纳米线,栅极四面环绕沟道,栅控能力更强,可以有效降低短沟道效应[5]。 GAA结构预计于2022年3 nm节点开始导入集成电路大生产线,并于2025年2.1 nm节点成为主流器件结构。

GAA晶体管结构的引入和特征尺寸的进一步微缩,对集成电路制造工艺设备提出了更高的要求:离子注入机将更加强调共形掺杂(Comformal Doping)、薄膜和刻蚀工艺更加强调原子级的精度控制(ALD-原子层沉积、ALE-原子层刻蚀)、其他设备(如CMP、ECD、湿法工艺设备等)也需要做相应调整,以满足更高精度加工、非铜互联材料、 新型HKMG材料等方面的需求。 下面就共形掺杂设备、原子层刻蚀设备、原子层沉积设备做详细介绍。

共形掺杂的离子注入设备:晶体管采用三维结构以后,对共形掺杂(各向同性的掺杂,各个方向上均匀掺杂)的要求不断提升。 传统的离子注入设备中,离子通过加速电场加速注入晶圆,掺杂的定向性强,为满足三维晶体管共形掺杂工艺的需求,离子注入设备有以下两个发展方向:(1)进一步提升离子注入机的束线角度、束线形状和注入剂量的控制能力,如应用材料公司的VIISta900 3D系统; (2)采用等离子体浸没式注入设备[6],在一层贴合晶圆表面结构的等离子体辅助下,实现各个方向的均匀掺杂,如应用材料公司的VIISta PLAD系统。

原子层沉积(Atomic layer deposition, 缩写ALD)和原子层刻蚀(Atomic layer etching, 缩写为ALE)[7]:进入纳米尺度以后,半导体制造对加工精度要求不断提高。 以IMEC的堆叠纳米线GAA晶体管结构为例,制备过程为:在衬底上沉积多层SiGe/Si超晶格结构,完成Fin刻蚀后,通过选择性刻蚀去除SiGe,释放Si纳米线,然后沉积高K介质及金属栅(置换式金属栅工艺); 在此过程中,SiGe结构刻蚀和纳米线的释放需要对实现对多层Si纳米线之间SiGe的横向精确去除,高K介质及金属栅的沉积需要在SiGe去除后的极小空间内完成,以上工艺均需通过ALE和ALD设备实现。 ALE和ALD技术可以以一种自我限制且有序的方式在原子尺度逐层去除/沉积材料,赋予人们原子尺度的精细加工能力。

(3)设备智能化。 集成电路技术在赋能信息技术产业的同时,新一代信息技术也在促进集成电路产业的发展,推动其不断迈向“智能制造”。 集成电路制造设备智能程度不断提升,将逐渐具备晶圆状态追溯、先进工艺控制(缺陷监测、工艺过程控制)、设备能耗管理、预测性排产、预测性维护和虚拟量测等功能。

要实现这些,除设备需要具有相应的信息采集及决策执行功能外,还需要产线信息系统的配合,单纯从设备的角度,根据IRDS预测,设备将按照表3所示的技术路线图发展,逐步支持智能化功能的实现。

表3 设备智能化技术路线图[1]

(4)450 mm(18英寸)设备。 在一次工艺过程中,更大的晶圆尺寸可以生产更多的芯片,可以显著降低单颗芯片成本。 晶圆尺寸不断增大是集成电路产业一直以来的发展趋势之一,由最初的100 mm (4英寸)、150 mm(6英寸),一直发展到今天的300 mm(12英寸,2001年引入,最早用于0.13 μm产线)。

2008年起,450 mm(18英寸)晶圆及其制造设备的生产被提上日程,初定于2012年组建18英寸试验产线,2015年开始大生产线替代。 目前450 mm (18英寸)大硅片及450 mm(18英寸) 设备接口标准早已完成,但是由于450 mm(18英寸)设备研发及晶圆厂建线耗资巨大,450 mm(18英寸)晶圆设备的应用时间一再拖期。 根据最新的IRDS技术路线图,450 mm(18英寸)设备的大生产线替代时间已经延后到了2025年之后。

审核编辑:汤梓红

-

半导体工艺与制造装备技术发展趋势2023-05-23 2564

-

工业电机行业现状及未来发展趋势分析2025-03-31 359

-

无线传感器网络的研究现状及发展趋势2012-08-15 4442

-

半导体工艺技术的发展趋势2019-07-05 4521

-

新兴的半导体技术发展趋势2019-07-24 2963

-

5G创新,半导体在未来的发展趋势将会如何?2019-12-03 3434

-

广播电视发展现状及趋势2021-07-21 2211

-

云计算产业发展现状及趋势2021-07-27 5182

-

恒兴隆机电:深圳电主轴行业市场现状及发展趋势是什么?2021-12-24 1628

-

国外半导体设备现状与发展趋势2009-04-07 1028

-

高清视频监控技术的现状及发展趋势2009-12-25 2040

-

智能化逆变弧焊电源控制策略现状及发展趋势2016-03-31 1526

-

张波教授论述功率半导体的现状及发展趋势2021-12-01 6890

-

半导体工艺装备现状及发展趋势2023-06-03 2231

-

全球与中国半导体熔断器市场现状及未来发展趋势.zip2023-01-13 703

全部0条评论

快来发表一下你的评论吧 !