3D-NAND 闪存探索将超过300层

存储技术

描述

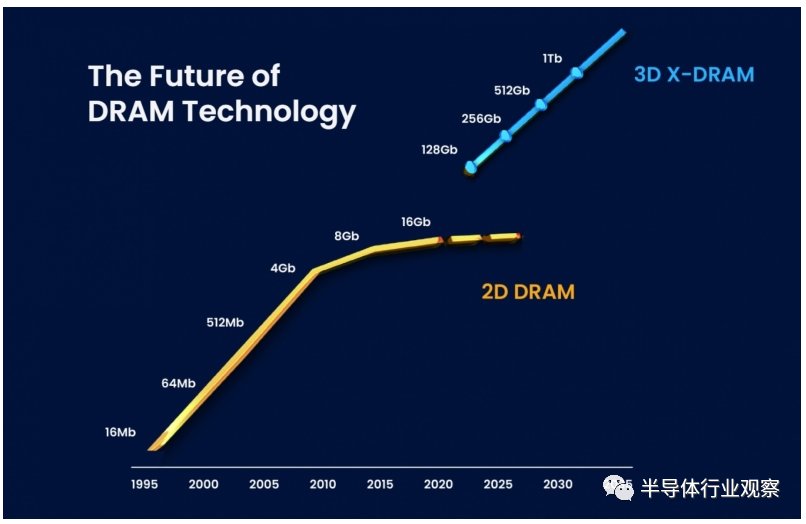

初创公司 NEO Semiconductor 表示,其 3D X-DRAM 技术可以生产 230 层的 128Gbit DRAM 芯片——是当前 DRAM 密度的八倍。

NEO 专注于半导体存储器并开发了X-NAND技术,NAND 芯片具有多个平行平面以加速数据访问——第一代顺序写入带宽为 1,600MBps,第二代为 3,200MBps。它表示全行业都在努力将 3D 单元带入 DRAM 的方法,NEO 现在拥有 3D DRAM 技术。与 3D NAND 一样,它可以显着提高 DRAM 密度。

该公司联合创始人兼首席执行官 Andy Hsu 乐观地表示:“3D X-DRAM 将是半导体行业未来绝对的增长动力。” Hsu 于 1995 年从伦斯勒理工学院获得硕士学位后,在一家未命名的半导体初创公司工作了 16 年。他于 2012 年 8 月创立了 NEO Semiconductor,并拥有 12 项专利。NEO本身拥有23项专利。

他补充说:“今天我可以自信地说,NEO 正在成为 3D DRAM 市场的明显领导者。与当今市场上的其他解决方案相比,我们的发明非常简单,制造和规模化成本更低。通过我们的 3D X-DRAM,业界有望每十年实现 8 倍的密度和容量提升。”

NEO 表示,3D X-DRAM 是解决由下一波 AI 应用(例如 ChatGPT)驱动的对高性能和大容量存储器半导体的需求增长所必需的。

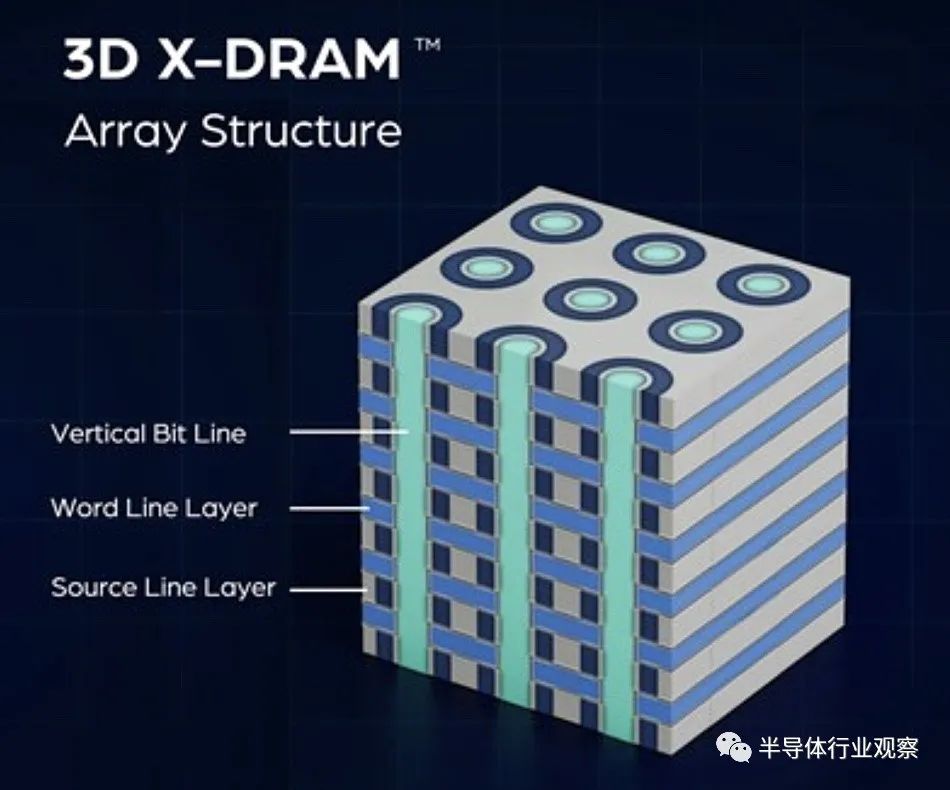

一张图展示了 3D X-DRAM 的概念:

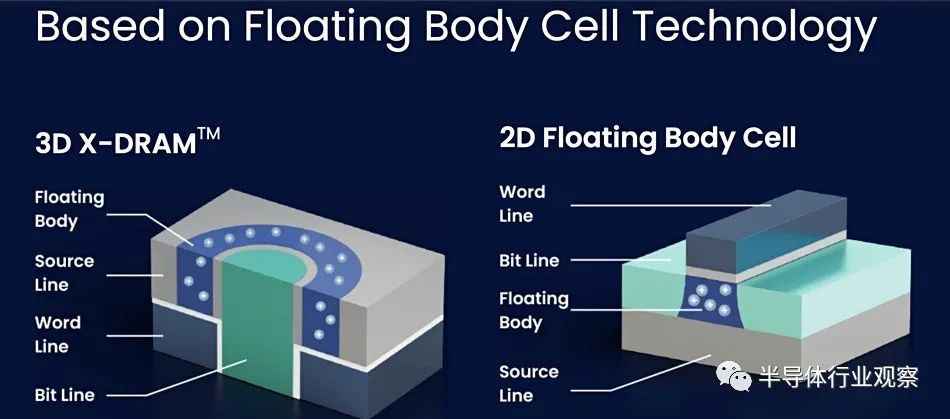

该概念具有基于无电容器浮体单元 (FBC) 技术的类 3D NAND DRAM 单元阵列结构。这种 FBC 技术使用一个晶体管和零个电容器将数据存储为电荷。NEO 表示它可以使用当前的 3D NAND 类工艺制造,并且只需要一个掩模来定义位线孔并在孔内形成单元结构。这提供了一种高速、高密度、低成本和高产量的制造解决方案,这是一个重要的主张。

全行业正在努力将 3D 引入 DRAM。采用 3D X-DRAM 仅涉及利用当前成熟的 3D NAND 工艺,这与学术论文提出和内存行业研究的许多将 DRAM 迁移到 3D 的替代方案不同。如果没有 3D X-DRAM,该行业将面临潜在的等待数十年,应对不可避免的制造中断,并减轻不可接受的产量和成本挑战。3D X-DRAM 是满足由 ChatGPT 等下一波人工智能 (AI) 应用推动的对高性能和大容量存储器半导体需求增长的必要解决方案。

Network Storage Advisors 总裁Jay Kramer表示:“从 2D 到 3D 架构的发展为 NAND 闪存带来了引人注目且极具价值的优势,因此在整个行业范围内实现 DRAM 的类似发展是非常可取的。” “NEO Semiconductor 的创新 3D X-DRAM 允许内存行业利用当前的技术、节点和工艺来增强具有 NAND 类 3D 架构的 DRAM 产品。”

据了解,NEO 将寻求将其技术授权给 DRAM 制造公司,例如美光、三星和 SK 海力士。Kioxia 和 Western Digital 等 NAND 制造商也可能获得许可。

3D-NAND 闪存,探索超过 300 层

在即将举行的 2023 年 VLSI 技术和电路研讨会上,多篇论文涵盖了 3D-NAND 闪存非易失性存储器。会议定于 6 月 11 日至 16 日在日本京都举行。

来自 Kioxia Corp. 的论文 C2-1,“A 1Tb 3b/Cell 3D-Flash Memory of more than 17Gb/mm2 bit Density with 3.2Gbps Interface and 205MB/s Program Throughput”提供了使用 210 个字线层的单片 1Tbit 存储器. 这代表了使用 3.2Gbps 读取接口和每秒 205MB 编程吞吐量进行优化的练习。该组件每个存储单元存储三位,并实现每平方毫米 17Gbits 的密度。

物理 8 平面架构实现了 40 微秒的读取延迟和每秒 205 字节的高程序吞吐量。单脉冲双频闪技术将感测时间减少了 18%,并有助于实现 205MB/s 的程序吞吐量。

Kioxia 和长期合作伙伴 Western Digital 的研究人员将提交论文 T7-1 “Highly Scalable Metal Induced Lateral Crystallization (MILC) Techniques for Vertical silicon Channel in Ultra-High (> 300 Layers) 3D Flash Memory”

金属诱导的横向结晶允许在超过 300 层的垂直存储孔中形成 14 微米长的“通心粉”格式通道。作者描述了最近开发的镍吸杂技术。112 字线分层 3D NAND 闪存在不降低存储单元可靠性的情况下,读取噪声降低了 40% 以上,通道传导性能提高了 10 倍。

半导体制造设备供应商 Tokyo Electron Ltd. 的一篇论文帮助绘制了一种 400 多层 3D-NAND 闪存的方法,使当今的商业技术水平翻了一番。

论文 T3-2 是“Beyond 10 micron Depth Ultra-High Speed Etch Process with 84% Lower Carbon Footprint for Memory Channel Hole of 3D NAND Flash over 400 Layers.” Tokyo Electron Miyagi 的作者在本文中讨论了一种使用低温和无碳化学进行高纵横比孔图案化的新型蚀刻工艺。作者发现,可以在大约 33 分钟的时间内将孔蚀刻到晶圆上 10 微米深。据说蚀刻剖面非常好。与其他蚀刻工艺相比,温室气体排放量减少了 84%。

编辑:黄飞

- 相关推荐

- 热点推荐

- DRAM

- Nand flash

-

3D-NAND浮栅晶体管的结构解析2024-11-06 5090

-

3D NAND闪存来到290层,400层+不远了2024-05-25 6372

-

三星:2030年3D NAND将进入1000层以上2023-07-04 3456

-

什么是3D NAND闪存?2023-03-30 4715

-

美光科技宣布已批量出货全球首款 176 层 3D NAND 闪存2020-11-12 2870

-

144层3D NAND将引领闪存容量的重大革命2019-10-11 1539

-

中国量产64层3D NAND闪存芯片会带来什么影响2019-09-23 1569

-

中国首次量产64层3D NAND闪存芯片会有什么市场影响2019-09-19 1262

-

三星、美光3D-NAND Flash产出比重已逾50%2018-11-16 1533

-

Sean Kang介绍未来几年3D-NAND的发展线路图,2021年堆叠层数会超过140层,而且会不断变薄2018-06-18 4369

-

美光与英特尔合作伙伴关系将终止 因3D-NAND不符合目前市场2018-01-15 1418

-

PK三星闪存 紫光2019年将量产64层3D NAND闪存2017-05-09 2595

-

SK Hynix月底量产48层堆栈3D NAND闪存 三星后第二家2016-11-09 1178

-

三星48层3D V-NAND闪存技术揭秘2016-07-13 7743

全部0条评论

快来发表一下你的评论吧 !