浅谈蚀刻工艺开发的三个阶段

描述

等离子蚀刻可能是半导体制造中最重要的工艺,也可能是仅次于光刻的所有晶圆厂操作中最复杂的工艺。将近一半的晶圆厂步骤依靠等离子体(一种高能电离气体)来完成工作。

尽管晶体管和存储单元不断缩小,工程师们仍在继续提供可靠的蚀刻工艺。

“为了可持续地制造具有纳米级精度和正确成本结构的芯片,晶圆厂设备制造商需要突破等离子体物理学、材料工程和数据科学的界限,以提供所需的设备解决方案,”Lam Research公司的蚀刻产品组营销副总裁 Thomas Bondur 说。这一点在等离子蚀刻中表现得最为明显,等离子蚀刻与光刻技术携手合作,在晶圆上创建精确、可重复的特征。

本文谈及了 3D NAND、DRAM、纳米片 FET 和互连中的关键蚀刻步骤,并展望了 2D 设备和低预算后端处理。该行业还在寻求更具可持续性的蚀刻化学品,以减少其工厂的等效而养护毯排放量。

对于许多工具制造商来说,工艺建模在蚀刻工艺开发中起着举足轻重的作用。目标是缩短上市时间,同时降低晶圆和掩模成本。

“对一些最棘手的步骤进行蚀刻工艺优化可能需要一年或更长时间才能完成,”Lam Research 高级营销总监 Barrett Finch 说。“我们最近在三周内完成了一些过程模拟工作,如果使用典型的基于硅的测试和开发,预计需要三个月的时间。”

光是设备制造商的光罩和晶圆成本,就可能达到数十万甚至数百万美元。

蚀刻基础

蚀刻工艺与光刻工艺密切相关。蚀刻之前通常先进行薄膜沉积(通过外延、化学或物理气相沉积等)。通常,CVD薄膜涂有光刻胶,然后使用光刻(248nm 或 193nm UV、13.5nm EUV)通过图案化的掩模版(掩模)曝光,光刻作用产生了图层。在单晶圆等离子蚀刻室中,通常蚀刻化学品和离子轰击并去除光刻胶没有反应的CVD 薄膜(在正胶中)。蚀刻后,光刻胶灰化、湿法化学清洗和/或湿法蚀刻去除残留物。

等离子蚀刻工艺可大致分为电介质、硅或导体蚀刻。二氧化硅和氮化硅等电介质最好使用氟化气体蚀刻,而硅和金属层与氯化学反应最好。基本上存在三种干法蚀刻模式——反应离子蚀刻(reactive ion etching)、等离子蚀刻(plasma etching)和溅射蚀刻( sputter etch:ion beam)。蚀刻工艺都是关于化学反应物、等离子体和晶圆材料之间复杂的相互作用。当 RF bias应用于反应性气体时,电子和带正电的离子轰击晶圆以物理去除(蚀刻)材料,同时化学物质和自由基与暴露的材料反应形成挥发性副产物。蚀刻可以是各向同性的(垂直和水平反应相等),

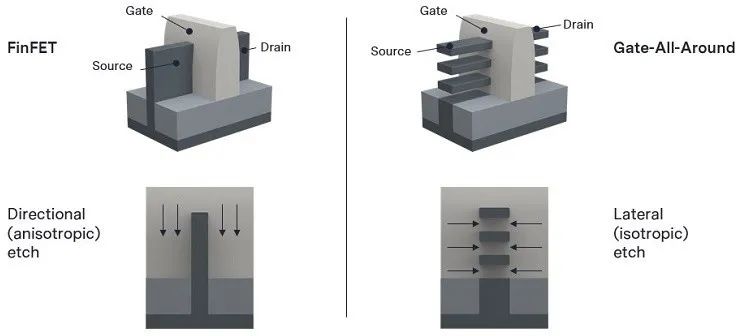

图1:从 finFET 到 GAA 的过渡推动了关键的各向同性选择性蚀刻要求

蚀刻工程师最关心的指标是蚀刻速率(etch rate)、轮廓控制(profile control)、均匀性(整个晶圆)和蚀刻选择性(etch selectivity),因为这些会影响良率和生产率。蚀刻选择性只是您要蚀刻的材料相对于其底层的去除率——例如,硅上的SiO 2 。在蚀刻过程中,不要去除过多的光致抗蚀剂也是有利的。但在这种情况下,通常会先将图案转移到硬掩模(二氧化硅、氮化硅、SiOC、TiN)上,然后再转移到底层薄膜上。

选择性规格从 2:1 到 1,000:1(高选择性蚀刻)不等。随着每个新节点的出现,这些规范变得更加严格。“随着High NA EUV 在未来四年内开始取代常规 EUV,焦点要低得多,所以你不能再曝光厚光刻胶——我指的是 30 纳米厚,” imec干法蚀刻研发工程师 Philippe Bézard 说。“但你仍然需要在下面图案化相同的薄膜厚度。所以现在你要求更高的选择性,而不是 2:1,我们必须达到更接近 10:1,这是选择性突然提高 4 到 5 倍。”

从概念验证 (POC:proof of concept) 到大批量制造 (HVM)

Bézard描述了蚀刻工艺开发的三个阶段:

确定执行蚀刻所需的蚀刻机、气体、辅助层等;

展示在规格范围内完全去除薄膜的性能,并在一个晶圆上保持工艺均匀性;

确定如何在 HVM 中以高产量和小漂移在数千个晶圆上重复该过程;

通常,熟练的蚀刻和集成工程师会处理开发的前两个阶段。第三阶段可能会再次利用工程专业知识,但机器学习可以提供帮助。

“一般来说,机器学习和数据分析只在第三阶段有用,”他说。“它非常强大,因为它可以访问大量数据,并且可以理解一百万个相互作用的微小、简单的事物。因此,对于人脑来说,试图解决这个问题非常困难,但对于计算机程序而言,它更易于管理。但如果你有一个新的应用程序、新的蚀刻材料或新的集成,它并没有显示出比人类有任何改进。”

ML 的使用还与制造成本有关,因为在第三阶段使用了数千个晶圆——至少比第一和第二阶段使用的晶圆大一个数量级。

Lam Research 蚀刻产品组高级总监 Barrett Finch 将新工艺探索描述为从标称工艺流程和布局中进行概念验证,并在晶圆上开发一个或多个工作设备。然后将该 POC 转移到晶圆厂的产品开发团队,以扩大流程并提高良率。

Finch说:“将名义上的概念验证转变为可行的高收益产品所需的工作量往往被低估,这与盈利能力存在巨大差距。”“工艺窗口建模试图通过在研发寻路的早期阶段引入工厂变化来缩小这一差距。” 他建议虚拟 DOE 和基于 Monte Carlo 的分析跨多个过程参数,通过模拟预期的可变性来测试 POC。

“工艺窗口建模可以回答这个问题,我必须保持什么样的 CD 或可变性水平才能达到最低设备性能和良率?'我们已经在几天内完成了超过 100 万个虚拟晶圆的虚拟工艺窗口测试,这在现实生活中是不可能完成的,”他说。

多个参数影响蚀刻速率(rate)、轮廓(profile)和选择性(selectivity)。一个关键是温度。“我们的客户在控制蚀刻速率、选择性和蚀刻轮廓时看到了热效应对蚀刻加工的影响。Lam Research 半导体工艺和集成工程高级经理 Benjamin Vincent 表示,所有这些参数都会影响器件产量和晶圆厂生产率。他认为,当一个工艺步骤具有多种可能的配置(工艺空间很大),或者该步骤的下游结果高度不可预测时,模拟可能特别有用。

Esgee Technologies 的产品营销经理 Alex Guermouche 表示:“蚀刻工艺依赖于晶圆的表面温度,而这又取决于多种热通量——包括热传导、离子碰撞能量、表面反应和等离子体辐射热通量。”“因此,等离子体模型需要结合所有这些物理特征,以准确描述晶圆表面的温度变化。工艺模拟软件可以对一系列蚀刻属性进行建模,使我们能够更快地获得更好的蚀刻结果,并加快客户提高产量或优化产量的能力。”

蚀刻工艺的精确计时

对于更紧密的几何形状和更薄的薄膜,需要在蚀刻速率与对其他操作参数的良好控制之间取得平衡。

“随着设计规则的缩小,许多蚀刻工艺正在转向非常快速的等离子体蚀刻工艺步骤,这需要对所有反应输入进行高度精确的控制:功率、压力、化学和温度,”Finch 说,并指出优化等离子体的趋势脉冲行为产生特定的离子与中性比,然后清除副产物。“此类条件的高级建模对于实现进一步的设备缩放至关重要。”

一段时间以来,蚀刻系统制造商一直在使用建模软件来加快下一个节点的开发或提高产量。考虑到该过程及其所有变量的绝对复杂性,这并不奇怪。

“在开发下一节点技术时,根本没有足够的时间或足够的晶圆来执行所有可能的工艺实验,”Finch 说。“蚀刻设备设置组合的数量可能达到数百万,甚至数十亿,使用所有工艺可能性的强力晶圆开发是根本不可能的。”

当然,所有好的模型都是在实际芯片上验证的。“一个准确的模型应该具有预测性,它应该解决用户想要解决的目标问题,”Finch说。“每次根据模拟工作推荐工艺或设计变更时,实际的晶圆厂数据应该反映推荐的结果。在我们的案例中,我们已经能够使用基于模型的结果准确预测流程变化的影响,并快速解决困难的流程和技术开发问题。”

工具供应商还致力于先进的蚀刻工艺,以更紧密地集成生产线,并将曾经的双掩模级工艺(两个光刻步骤)转变为一个工艺,以简化工艺并降低成本。

Bézard 说:“公司没有采用现有的硬件来让瑞士军刀装备得更好,而是引入了特定于应用程序的技术,例如解决尖端问题的新系统。” 目的是使彼此面对的两条线靠得更近,目前这涉及线图案化步骤,然后是切割掩模。“应用材料公司和其他公司正在推出的是一种在水平方向上直接蚀刻的方法。” 这样的过程也可以加宽通孔。

纳米片 FET 的蚀刻步骤

纳米片工艺流程中最关键的蚀刻步骤包括虚拟栅极蚀刻、各向异性柱蚀刻、各向同性间隔蚀刻和通道释放步骤。通过硅和 SiGe 交替层的剖面蚀刻是各向异性的,并使用氟化化学。优化内部间隔蚀刻(压痕)和通道释放步骤,以极低的硅损失去除 SiGe。

沟道释放步骤至关重要。“纳米片的释放需要极高的选择性,”Bézard 说。“大多数纳米片是硅,然后是硅锗和硅。你有交替层,你需要删除一个而不修改另一个。” 一些出版物已经讨论了执行多步骤 SiGe 蚀刻以减少由单个蚀刻步骤引起的结构应力。

该制程的下一步是形成自对准触点。“在这里,我们试图做的基本上是蚀刻二氧化硅,而不是接触或凹陷氮化硅。比方说,目前的规格是 3nm 凹陷,但人们要求零损失,”Bézard 说。“在这种情况下,我们甚至没有使用选择性这个词。我们只是谈论休会(recess)——而且是零休会(zero recess)。”

3D NAND

对于3D NAND闪存,层数不断增加,未来需要采用多个堆叠层,最终创建堆叠设备的垂直串。“此外,随着层数的增加,为了继续增加位密度,有很大的动力来缩放层的字线间距或垂直/Z 间距,”TEL的技术总监和高级技术人员 Robert Clark说。“从工艺的角度来看,蚀刻和沉积工艺将需要不断改进,以适应持续缩放所需的越来越小的关键尺寸和越来越高的纵横比。”

Clark描述了未来的变化。“着眼于多层电荷陷阱器件的先进节点,需要对栅极堆叠进行工程设计,以实现更短的栅极长度、每个单元更多的电平和更高的编程效率——可能通过采用高 k 材料。未来也可能需要更高导电率的通道来取代多晶硅通道,”他说。

3D NAND 中最关键的蚀刻之一涉及通过多层氧化物-氮化物堆栈(200 层以上)深度蚀刻约 100 纳米的孔,深度可达 10 微米。Imec 的 Bézard 说这个蚀刻步骤特别昂贵。

“我们有一种物理现象发生,称为差异充电效应( differential charging effect),”他说。“在等离子体中,我们有电子、离子和中性物质可以简化很多。电子向各个方向移动,但离子垂直于表面加速。所以你在孔的底部有正电荷,在顶部有负电荷,你会得到一个试图排斥进入的离子的电场。”

结果,需要高功率水平来完全蚀刻沟槽。“我们正试图在没有电弧的情况下维持 30 到 50 gigawatts的功率,因此卡盘必须经过极好的抛光和制造,”他说。

深蚀刻还会产生需要最小化的应力,特别是因为多层 NAND 制造随后需要晶圆减薄、精确对准和与下一层的混合键合。

其他工艺

并非所有芯片制造商都生产需要 EUV 光刻的尖端芯片。许多晶圆厂正在扩展其 193 纳米光刻和蚀刻工艺。

“我们有一种最近开始推出的高温 SOC 材料,它可以扩展其图案化能力并能承受更高的温度,无论它是用作 CVD 层还是掩模的底层,”Brewer Science半导体产品多元化总监 Brian Wilbur 说。

预计最紧密金属线的BEOL将经历从双镶嵌集成方案到除铜以外互连的减法沉积和蚀刻的巨大转变。在这里,两种金属——钌和钼——得到了最彻底的开发。然而,钼在蚀刻过程中更容易氧化,使其更适合双镶嵌方案。钌是一种贵金属,因此不存在同样的腐蚀问题,但成本更高。

设备结构也变得不能容忍边缘放置错误。据 TEL 的 Clark 称,将需要新的层与层之间以及通孔和线路之间的自对准方案。“第一个实施可能是用于 DRAM 中的埋字线,以及用于逻辑的小间距 MOL 金属层,这些地方需要更高的热稳定性以及更低的电阻率或无衬垫金属。”

下一代发展

从长远来看,该行业理想情况下将过渡到较低热预算的后端工艺(接近 300°C 而不是 400°C),以便将设备集成到后端互连层中。

“该行业确实需要开始将设备构建到更多层中,”TEL 的Clark说。“这意味着我们需要在 BEOL 热预算内在 BEOL 内构建内存和逻辑设备。”

到目前为止,使用半导体氧化物制造的设备看起来很有前途,既可以用于将存储设备集成到逻辑 BEOL 流程中,也可以用于在 DRAM 的存储阵列之上构建 CMOS 阵列。

另一个重大转变涉及二维材料的集成,研究机构和领先的芯片制造商已经开始对其进行测试。正在考虑对二硫化钨或二硫化钼等材料进行蚀刻工艺。这些薄膜由单层材料组成,因此开发集成它们的制造工艺极具挑战性。

可持续性

芯片制造商和材料供应商正在寻求替代化学品以减少碳排放。在蚀刻中,罪魁祸首是具有高全球变暖潜能值的氟化气体。

“有问题的 PFOS(全氟辛烷磺酸)的一个原因是因为分子非常稳定,”imec 的 Bézard 说。“大气中的光或化学反应不足以分解它。”他说,许多含氧量较高的替代气体混合物更容易分解,并且具有较低的 GWP。“然而,任何候选人都必须提供同样好的甚至更高的表现才能开始。”

但可持续性并不是蚀刻或沉积的特别挑战。这是从光刻到封装的整体行业挑战,其中新材料的影响影响整个设备处理。

编辑:黄飞

-

湿法蚀刻工艺的原理2022-07-27 4100

-

在PCB外层电路中什么是蚀刻工艺?2017-06-23 3167

-

【AD问答】关于PCB的蚀刻工艺及过程控制2018-04-05 4339

-

PCB线路板外层电路的蚀刻工艺详解2018-09-13 3185

-

详谈PCB的蚀刻工艺2018-09-19 3861

-

PCB外层电路的蚀刻工艺2018-11-26 4265

-

PCB蚀刻工艺质量要求2020-03-03 4734

-

湿法蚀刻工艺2021-01-08 4870

-

PCB蚀刻工艺原理_pcb蚀刻工艺流程详解2018-05-07 49031

-

PCB板蚀刻工艺说明2020-07-12 5495

-

关于湿法蚀刻工艺对铜及其合金蚀刻剂的评述2022-01-20 3476

-

蚀刻工艺 蚀刻过程分类的课堂素材4(上)2022-08-08 1804

-

简述光刻工艺的三个主要步骤2024-10-22 4008

-

芯片湿法蚀刻工艺2024-12-27 1993

-

新型HERB技术如何重塑芯片蚀刻工艺2026-03-24 171

全部0条评论

快来发表一下你的评论吧 !