PCB Layout设计要点与技巧

PCB设计

描述

在集成电路应用设计中,项目原理图设计完成之后,就需要进行PCB布板的设计。PCB设计是一个至关重要的环节。设计结果的优劣直接影响整个设计功能。因此,合理高效的PCB Layout是芯片电路设计调试成功中至关重要的一步。本次我们就来简单讲一讲PCB Layout的设计要点。

PCB Layout设计要点

元器件封装选择

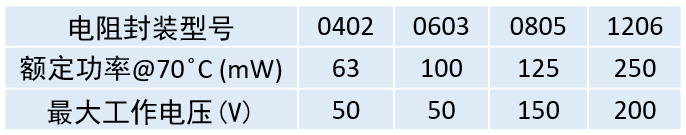

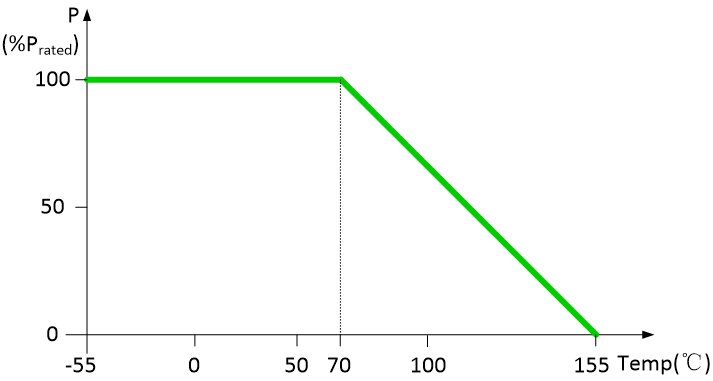

电阻选择: 所选电阻耐压、最大功耗及温度不能超出使用范围。

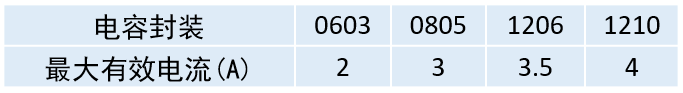

电容选择: 选择时也需要考虑所选电容的耐压与最大有效电流。

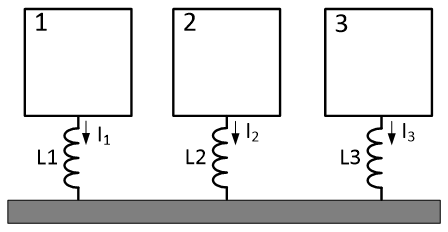

电感选择: 所选电感有效值电流、峰值电流必须大于实际电路中流过的电流。

电路设计常见干扰

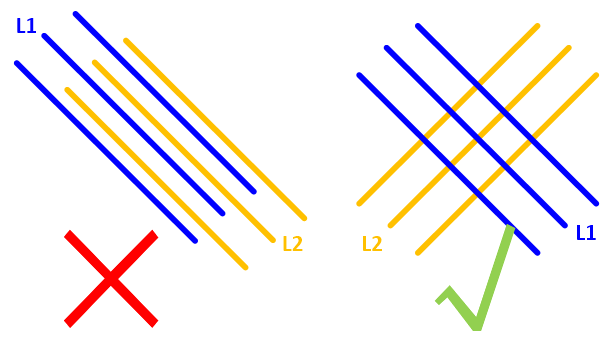

串扰: 设计线路平行走线距离过长时, 导线间的互容、互感将能量耦合至相邻的传输线。可以通过以下方法减少串扰影响:

1.加入安全走线

2.实际时尽量让相邻走线互相垂直

3.每走一段距离的平行线,增大两者间的间距

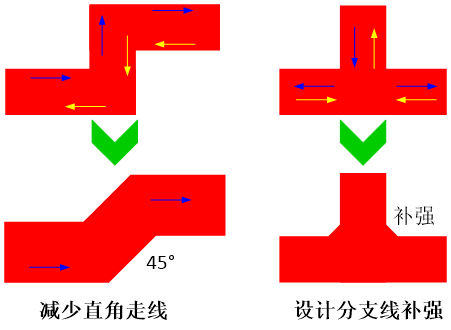

反射: 由于布线的弯角、分支太多造成传输线上阻抗不匹配,可以通过减少线路上的弯角及分支线或者避免直角走线及分支线补强来进行改善。

确定接地方式

单点接地(适用于低频电路):所有的电路接地线接到公共地线同一点, 接线简单且减少地线回路相互干扰。

多点接地(适用于多层板电路/高频电路):系统内部各部分就近接地,提供较低的接地阻抗。

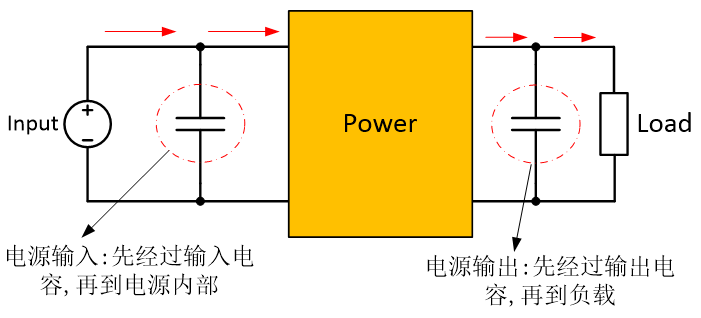

增加滤波、旁路电容

为保证输入/输出电压稳定,增加输入/输出电容。

在电源和IC间增加旁路电容,以保证输入电压稳定并滤除高频噪声。

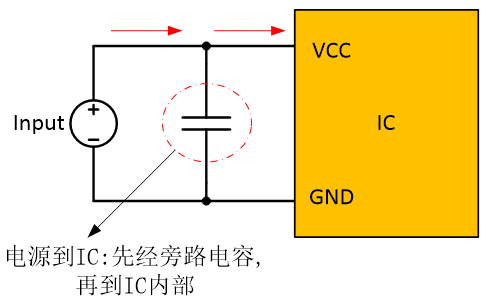

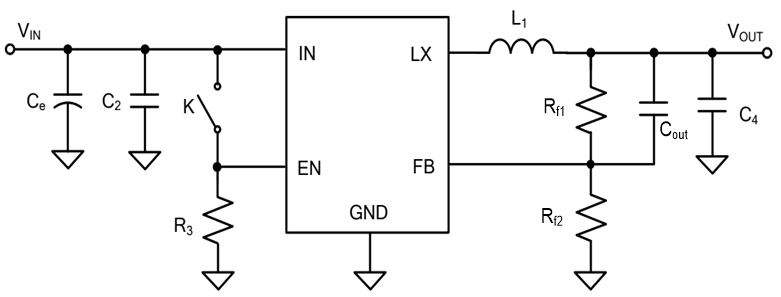

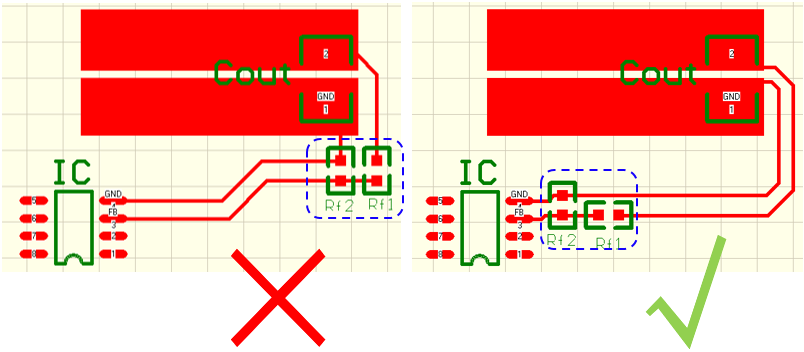

阻抗位置设计

相对来说阻抗越高的位置, 越容易被干扰。如下为一同步降压芯片的PCB阻抗位置设计。

PCB Layout设计技巧

电源/地线处理

既使在整个PCB板中的布线完成得都很好,但由于电源、 地线的考虑不周到而引起的干扰,会使产品的性能下降. 布线时尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线。

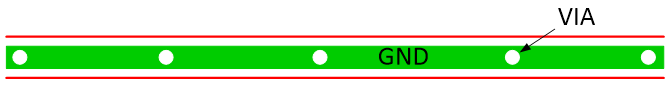

对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路不能使用该方法)。用大面积敷铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源、地线各占用一层。

数字与模拟电路的共地处理

数字电路与模拟电路的共地处理: 数字电路与模拟电路共同存在时,布线需要考虑之间互相干扰问题,特别是地线上的噪音干扰。

数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,

对地线来说,整个PCB对外连接界只有一个端口,所以必须在PCB内部进行处理数、模共地的问题,而在板内部数字地和模拟地实际上是分开的它们之间互不相连,只是在PCB与外界连接的端口处(如插头等), 数字地与模拟地有一点短接,请注意,只有一个连接点。

信号线分布层

信号线布在电源(地)层上: 在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量,成本也相应增加了,

为解决这个矛盾,可以考虑在电(地)层上进行布线。首先应考虑用电源层,其次才是地层。因为最好是保留地层的完整性。

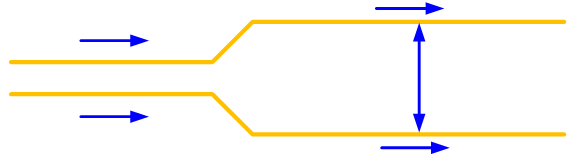

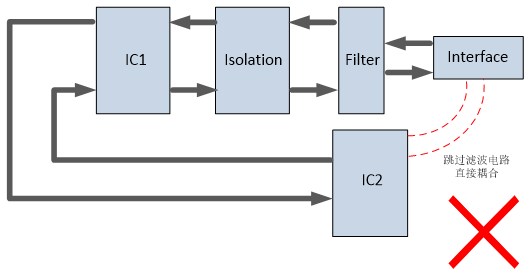

信号流向设计

PCB布局设计时,应充分遵守沿信号流向直线放置的设计原则,尽量避免来回环绕。

PCB Layout设计实例

Layout设计建议

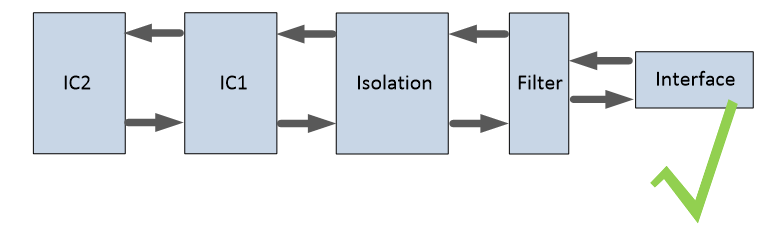

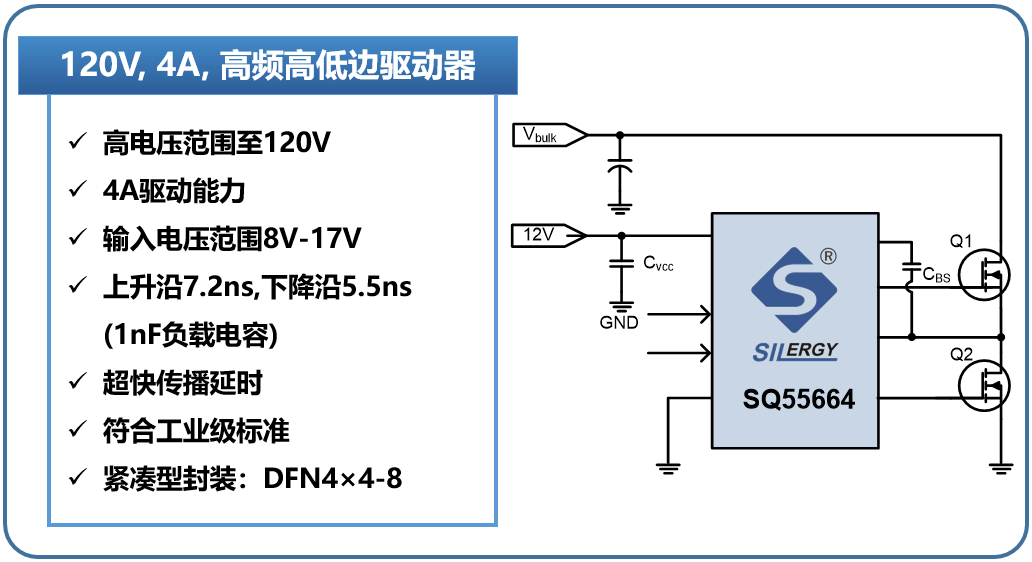

1. 驱动芯片与功率MOSFET摆放尽可能靠近;

2. VCC-GND(CVCC) / VB-VS(CBS)电容尽可能靠近芯片;

3. 芯片散热焊盘加一定数量过孔并且与GND相连接(增加散热、减小寄生电感);

4. GND布线直接与MOSFET 源极(source)相连接, 且避免与源极(source)-漏极(drain)间大电流路径相重合, VS 同理GND布线原则(避免功率回路与驱动回路重合);

5. HO/LO布线尽量宽(60mil-100mil,驱动电流比较高,降低寄生电感的影响);

6. LIN/HIN 逻辑输入端口尽量远离HS布线(避免过高的电压摆动干扰到输入信号)。

审核编辑:汤梓红

-

PCB Layout 的 9 个套路2024-07-03 2238

-

PCB Layout的设计要点及实例分享2024-04-29 2302

-

PCB Layout的设计要点及技巧2023-04-27 2534

-

PCB layout设计要点及技巧2023-04-03 3131

-

关于DC-DC芯片应用设计中的PCB Layout设计要点2022-12-28 1449

-

PCB Layout的设计要点2022-11-29 1324

-

DC-DC芯片应用设计中的PCB Layout设计要点2022-06-12 2810

-

简单讲一讲PCB Layout的设计要点2022-02-22 2060

-

干货分享:PCB Layout 的设计要点2021-12-29 1272

-

干货分享:PCB Layout的设计要点2021-12-16 1012

-

DCDC芯片中PCB Layout的设计要点2021-09-14 10454

-

基于WLAN芯片的PCB layout的设计要点2020-12-14 4905

-

不可忽视的电源布局细节,电源 IC 的 PCB layout要点2020-07-16 4570

全部0条评论

快来发表一下你的评论吧 !