为什么串行接口速率比并行接口快?

电子说

描述

串行接口的速率会比并行快,可以从下面四个方面考虑:

①高速串口不需要时钟信号来同步数据流,也就没有时钟周期性的边沿,频谱不会集中,所以噪声干扰少很多。

以PCIE和SATA为例,时钟信息通过8b/10b编码已经集成在数据流里面,数据本身经过加扰,绝对不可能有多于5个0或者5个1的长串(利于时钟恢复),也绝对不存在周期性(避免频谱集中)。这样,通过数据流的沿变可以直接用PLL恢复出时钟,再用恢复的时钟采集数据流。这有什么好处?时钟信号消耗的功耗极多,带来的噪声也最大,不传时钟可以降低功耗,减少噪声。

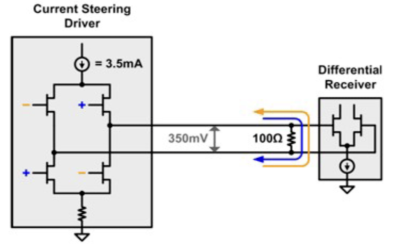

②所有高速串口都采用差分总线传输,外界噪声同时加载到两条差分线上,相减之后可以抵消,具备很强的抗干扰能力,同时因为差分线通常以电流为载体传输,远端没有电压传输的压降,因此长距离也不是问题。

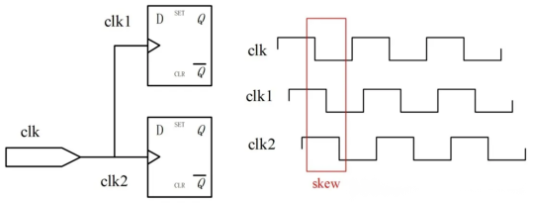

③差分信号没有时钟skew问题,因为它根本就没有同步时钟,不存在时钟和数据流的对齐问题。只需要保证差分信号线是对齐的就行,这是很容易的,因为差分信号线的值总是相反,相关性强,易控制。一根线跳的时候,另一根线经过一个非门的延时马上会跳,这个非门的延时是很容易补偿的。

并行总线最大的问题就是多根线传输的时候,无法保证所有的沿变都对齐,很有可能传着传着某些信号跟不上,落后了一个时钟周期,数据就传错了。想控制也难,因为各个信号没有相关性,互相的沿变本身就是独立的,因为布线不同,很有可能一个跳的早点,另一个跳的晚点,再加上各个传输线电阻不同,噪声不同,传一会儿就分辨不出来哪个值对应哪个周期。

④差分线线数少,干扰少。并行传输,一般32根或者64根,一根线跳变,会给旁边的线带来噪声,频率越高,这种噪声越大,很容易导致别的线值被篡改或者无法辨认,所以频率不可能很高。串行传输一般就4根数据线,分成Rx两根差分线和Tx两根差分线,差分线总是往相反方向跳,可以抵消各自的跳变噪声,比如Rx的正极性发生跳变时会产生噪声,这种噪声可以被Rx的负极性以相反的跳变直接抵消掉(因为他们是差分信号对),总的噪声为0,杜绝了内部噪声。

综上,串口传输的各种优势使得其内外噪声皆免疫,又没有信号对齐之忧,可以以极高的速率传输。比如SATA可以以6Gb的速率传输数据流,PCIE可以以8Gb的速率传输数据流。这种速率,并行传输是根本做不到的,更不要说串行传输还能节省大量引脚。

串口为啥比并口快,还有的因素是串口的特性和应用场景,决定了它更加适合采用一些可以提高单根信道速率的设计方法:差分信号(differential signaling),时钟-数据恢复(Clock-Data Recovery,简称CDR),和信道均一化(Channel Equalization,Eq)。而这些方法目前用在并口上并不合适。

既然串口有如此大的优势,为什么并口还是存在?

从现有的应用看来,有一些历史遗留速度不高的应用,还有一些需要突发性高带宽的应用,还是需要并口的应用,比如很特殊的DDR。虽然XDR/GDDR/HMC/HCM这些新标准都在试图引入SerDes, 但DRAM行业的特殊性还是让并口继续存活着。

【以上信息由艾博检测整理发布,如有出入请及时指正,如有引用请注明出处,欢迎一起讨论,我们一直在关注其发展!专注:CCC/SRRC/CTA/运营商入库】

审核编辑 黄宇

-

串行接口与并行接口的区别2024-08-25 10354

-

为什么串行接口速率比并行接口快?2023-06-06 2682

-

收藏起来!串行接口串行接口和并行接口的区别-科兰2023-06-05 3533

-

串行接口和并行接口有什么不同2022-06-21 12237

-

串行接口与并行接口相比有何优点2022-02-15 1760

-

串行接口为啥比并行接口快?你明白吗2021-05-18 2426

-

关于串行和并行接口SRAM的对比分析2019-08-26 5712

-

SRAM存储器的并行接口和串行接口对比2019-05-13 5245

-

串行接口比并行接口快的原因2018-08-30 2612

-

usb是串行接口吗_串行接口和并行接口有什么区别2018-03-26 69108

-

串行和并行接口SRAM对比,谁会是未来主流?2015-11-06 4405

-

什么是并行接口2010-01-12 9152

-

并行接口2009-03-25 2297

-

PC 并行接口定义2009-02-12 1252

全部0条评论

快来发表一下你的评论吧 !