参数随机策略:从randc到off-line cyclic random

电子说

描述

根据对randc的了解和思考,分享一种基于testcase颗粒度的"周期性"随机控制思路(off-line cyclic random)。并从编码实现上,验证了该思路的可行性。

randc背景

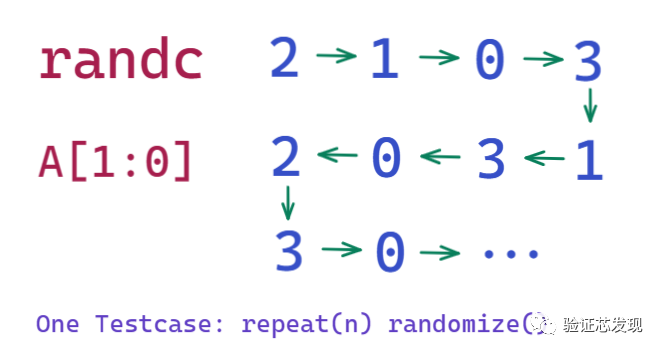

在systemverilog中,随机循环变量(randc),在一次仿真中多次调用randomize,会随机循环遍历其声明范围的所有值。随机序列中的值都被取到后,产生一个新的随机序列。

randc修饰的变量存在一些限制,如对变量类型的限制,不能参与solve before。而且randc只能是在一次仿真中具有“周期性”随机的特性,此前用例的随机结果不会影响当前仿真的周期性取值序列。也可以认为randc是一种on-line的周期性随机。

off-line cyclic random

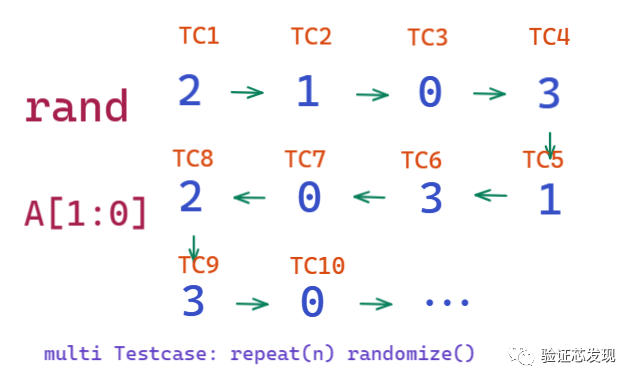

验证用例集中的testcase多次仿真时,当前testcase的随机过程无法知道此前用例的随机状态和结果。因此有一定概率会出现随机变量在多次仿真时取到相同的值。

和randc类似,有没有可能off-line的周期性随机:随机变量在testcase的多次仿真之间具有周期性。

off-line cyclic random:随机变量的随机取值不会和已有用例的随机结果重复,并能够"周期性"取值。已有的随机结果可以是已有用例的随机结果,也可以是预指定的取值集合。

编码实践

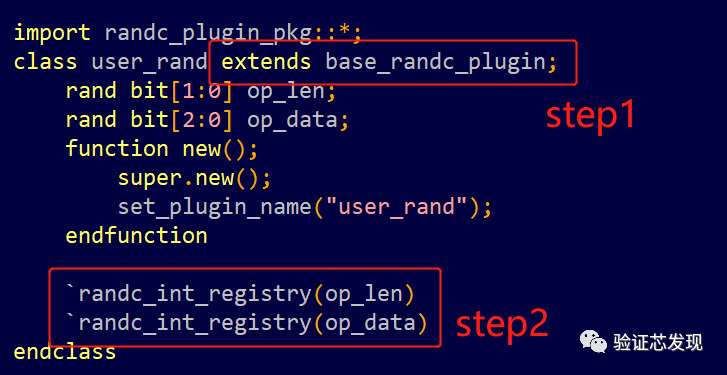

为验证上述思路的可行性,并且还要降低对已有的随机激励结构的影响,开发一个randc_plugin的package。使用时需要两步骤适配:

已有的随机激励class继承base_randc_plugin;

使用参数宏添加随机参数;

一个简单的demo如下:

参数宏randc_int_registry表示注册一个需要randc based testcase的int型变量,适用于systemverilog中的int,bit和enum类型。数组和其他复杂类型的注册宏待后续补充完整。

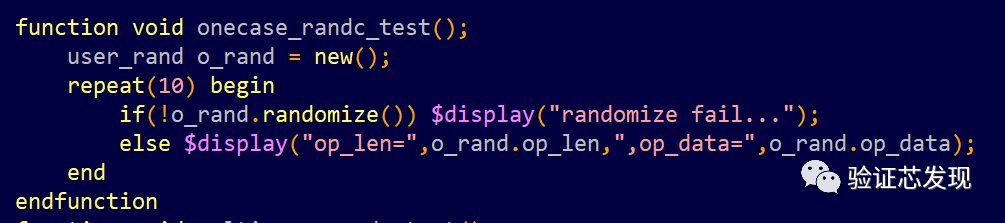

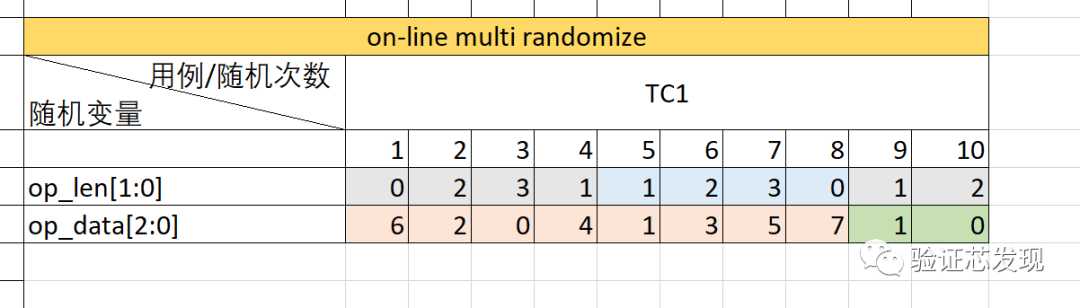

on-line multi randomize

即使是使用rand修饰的随机变量,使用randc_int_registry注册后,仍具有randc的性质,而且还可以参与solve before,并且原有的constraint不受影响。

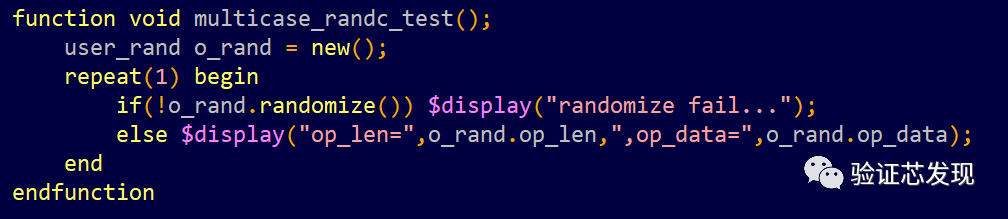

测试函数如下:

汇总得到的随机结果如下:

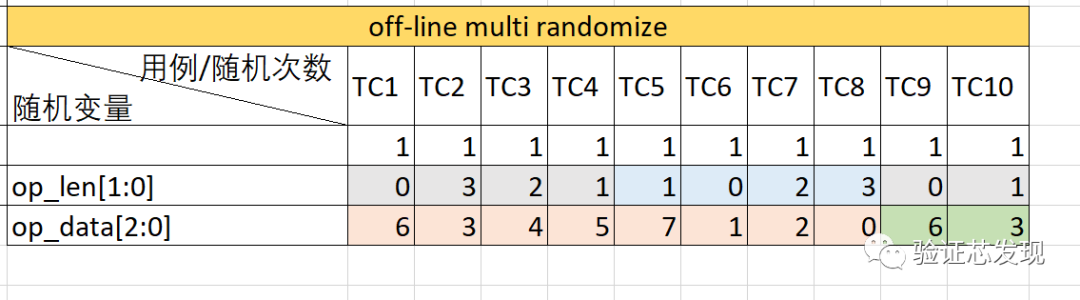

off-line multi randomize

测试函数如下:

将用例仿真10次后,汇总的随机结果如下:

由于每个领域的验证各具特色,这里仅提供一种随机控制的思路和编码实现尝试,randc_plugin还在持续完善中。

审核编辑:刘清

- 相关推荐

- 热点推荐

- 编码器

-

off-line LED driver2016-04-06 1704

-

浅析cache控制器的分配策略与替换策略2022-06-15 2605

-

LM5021,off-line pulse width mo2009-09-29 689

-

Integrated Off-Line Switcher w2009-11-02 430

-

Off-Line SMPS Quasi-Resonant P2009-11-10 632

-

Multi-Output Flyback Off-Line2010-07-30 353

-

UCC2888,UCC3888,pdf(Off-line P2010-09-30 602

-

什么是CRC (Cyclic Redundancy Chec2010-02-22 1101

-

C语言random函数伪随机数产生2011-08-25 13604

-

三相电流连续型Off-line PFC2017-09-11 834

-

如何利用SystemVerilog仿真生成随机数2021-10-30 12921

-

解析Air780E模组LuatOS开发的随机数(random) 示例篇2024-11-29 1144

全部0条评论

快来发表一下你的评论吧 !