深入探讨在FPGA设计中要避免的10大错误

可编程逻辑

描述

本文列出了FPGA设计中常见的十个错误。我们收集了 FPGA 工程师在其设计中犯的 10 个最常见错误,并提供了解决方案的建议和替代方案。本文假定读者已经具备 RTL 设计和数字电路方面的基础。接下来让我们深入探讨在FPGA 设计中要避免的 10 大错误。

异步逻辑

FPGA 设计适用于同步系统,即使异步逻辑是可综合的,它也会导致设计中的时序违规(亚稳态)。有 FPGA 工程经验的人往往会避免在他们的 FPGA 设计中使用任何异步逻辑。缓解此问题的一种方法是在驱动 LUT 的设计中同步锁存所有异步逻辑。

设计中的异步循环会增加 FPGA 的功耗,从而增加热量并可能导致不必要的“过热”问题。

以下是使用异步逻辑有益的情况:

- 在 AXI-stream协议中,最好将“tready”表示为异步,这里可以使用reg slice来减轻异步逻辑,这会增加整个设计的利用率。

- 基于 DSP slice 的计算。使用 DSP slice 的除法、乘法可以异步完成,对时序几乎没有影响。

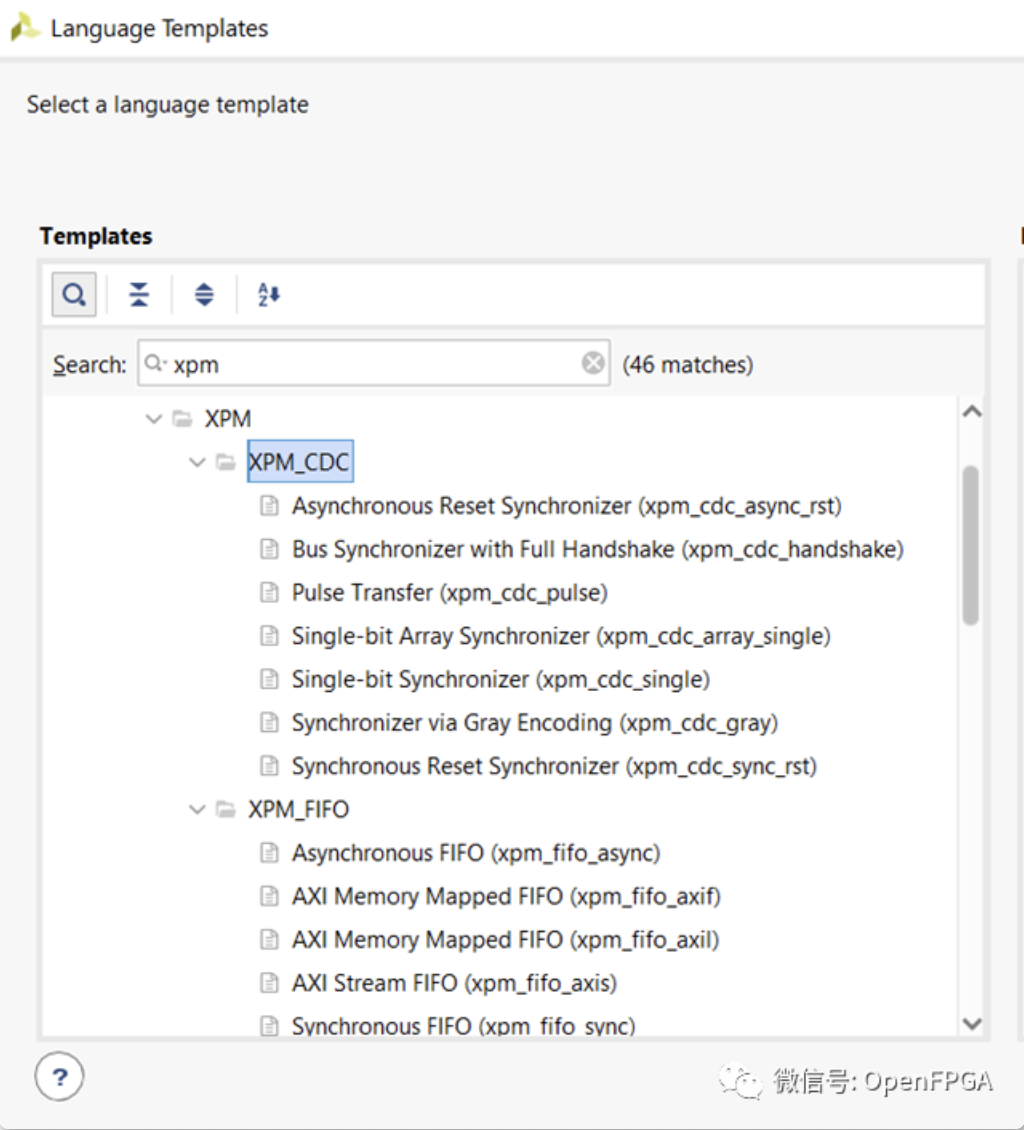

不使用厂商提供的原语

这是 FPGA 初学者常犯的错误。以Xilinx器件为例,Xilinx为时钟缓冲器、CDC、DLL、时钟分频器等提供原语。充分利用器件中现有的原语将带来更高效的设计,并大幅缩短开发时间。

例如:

1、 将 xpm-cdc 用于同步器将减少为其编写 RTL 以及为该信号定义约束的麻烦。

2、使用 bufr 进行时钟分频会自动将生成的时钟放置在时钟树上,并推断生成的时钟约束。

未充分利用 DSP Slice

在 Xilinx FPGA 中,DSP Slice 能够用作累加器、加法器、减法器、除法器和乘法器。当需要这些功能时,最好使用 DSP slice 而不是 LUT/Fabric 来执行此操作。这将减少花在设计优化以及设计结束时的时序收敛上的时间。

有些设计需要非常高的时钟频率才能工作,在这种情况下,DSP Slice可以大大减少时序问题。

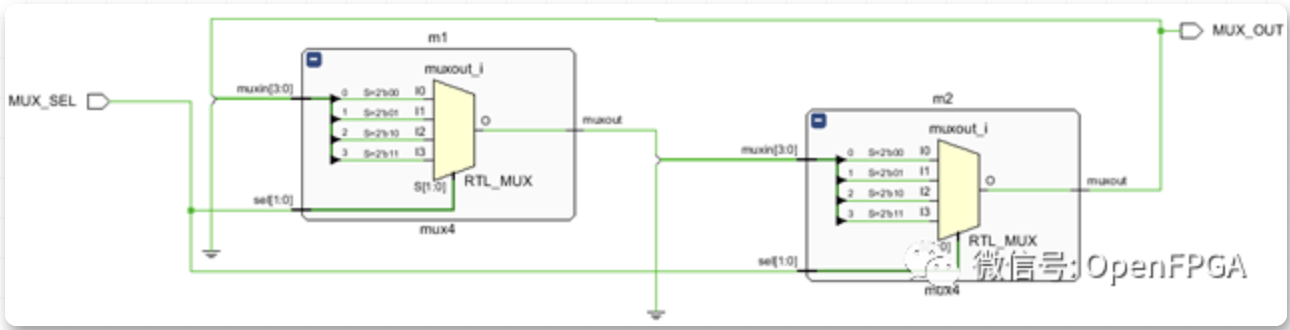

检查设计中推断的锁存器

这是一个可以用例子很好解释的案例。编写状态机时,应该有 1 个同步状态和 2 个异步状态。在异步的 NEXT STATE LOGIC 中,如果忘记考虑所有条件,工具将推断一个锁存器,即 next_state 信号将被预期为设计中的生成时钟,因为它将驱动多个 LUT。盲目忽略这种情况会导致状态机停止,并且在出现故障时无法恢复。

不在每个阶段运行 DRC 检查

DRC 检查是必须的,应该在综合和实现之后进行。应正确分析 DRC 中的任何严重警告,并在设计中加以考虑。如果不这样做,可能会导致系统不稳定,并可能在某个时间点发生故障。

不遵循正确的命名和编码约定

所有 RTL 设计工程师都应遵循其设计的标准命名约定,例如。

- 为所有输入添加 i_

- 为所有输出添加 o_

- 为所有信号添加 s_

- 为所有常量添加 c_

- 为所有通用信号添加 g_

- 时钟应命名为 i_clk_m:例如 i_clk_122m88

- 复位应命名为 i_rst_

所有代码都应正确记录、注释和测试(综合前和综合后)

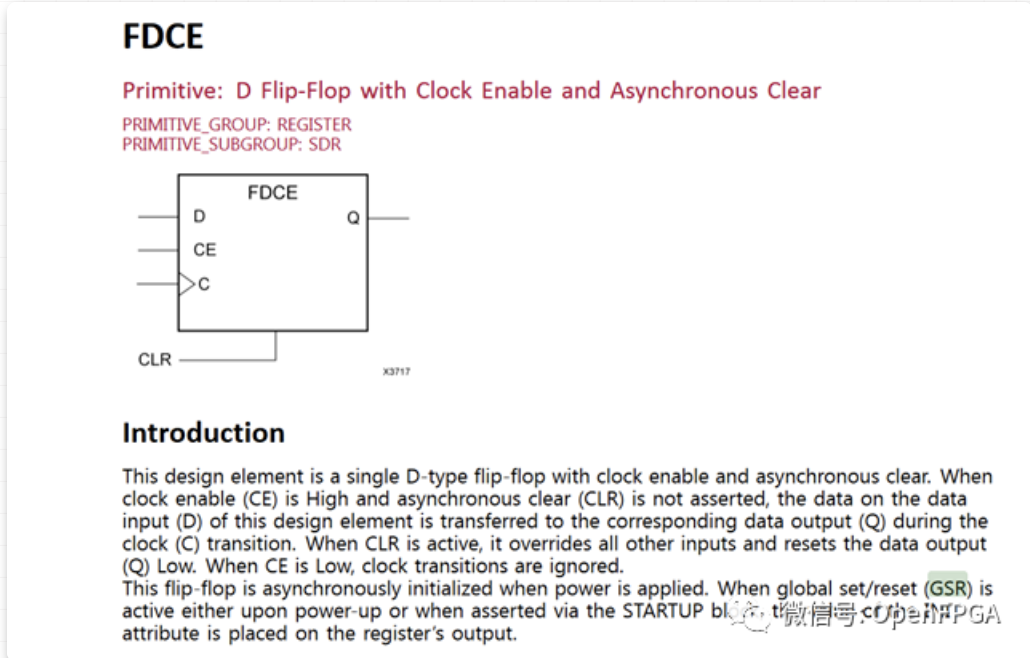

复位信号的不必要使用

在 Xilinx 设备中,使用复位引脚驱动所有信号并不是首选,因为它会大大增加设计中的扇出。相反,最好将 gsr 引脚用于所有中间信号。

即:当声明信号时,将其本身初始化为复位值。

利用率计算

在 FPGA 中,不建议完全利用所有可用资源。开始设计时,选择一个可以容纳设计并有额外 10% 到 20% 可用空间的FPGA。这样做是为了让路由有余地使用其内置逻辑满足建立和保持时间。

如果不这样做,后续的时序很难收敛,就不得不降低系统时钟。

将block design用于大型设计

block design是轻松互连 RTL 的好方法,但对于大型项目,block design在 Xilinx Vivado 中也有很多固有的错误,这会在设计中引起很多不必要的警告。

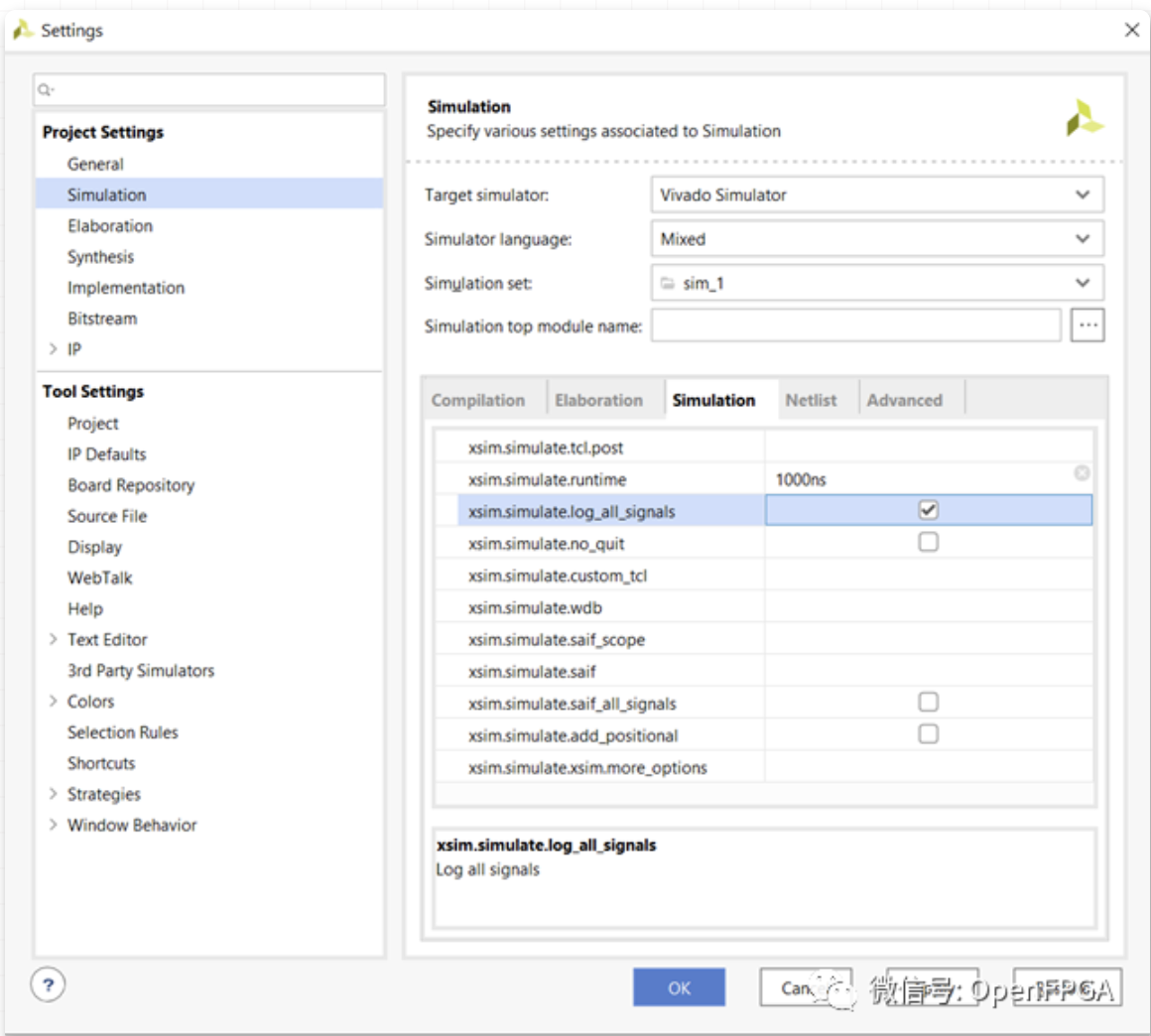

不检查仿真设置中的记录所有信号选项

在仿真设计时,最好首先检查 vivado 中的记录所有信号选项。这将避免为了向仿真波形添加附加信号而不得不重新运行整个仿真。这适用于与 vivado 结合使用的所有第三方仿真软件。

-

深入探讨电容的种类和作用2009-11-27 15827

-

FPGA设计中经常犯的10个错误2023-05-31 1692

-

深入浅出玩转fpga PDF教程和光盘资源2012-02-27 58411

-

深入探讨DFM在PCB设计中的注意要点2014-10-24 3895

-

深入浅出玩转 FPGA-吴厚航2014-12-29 2710

-

stm32 uart硬件实现及深入探讨(单片机通信学习连载4)2021-06-29 3651

-

【原创】STM32 UART通信深入探讨2021-07-15 3701

-

【视频】 stm32 uart硬件实现及深入探讨32021-09-17 2785

-

【视频】 stm32 uart硬件实现及深入探讨42021-09-22 2960

-

电工常犯的15大错误2021-09-24 684

-

深入探讨超声波风速风向仪2021-10-27 782

-

深入探讨交通安全统筹信息系统2021-10-29 968

-

深入探讨医疗应用的未来发展趋势2022-11-03 658

-

深入探讨RF信号链2023-01-03 1676

-

深入探讨软件定义架构及其意义2023-02-08 1804

全部0条评论

快来发表一下你的评论吧 !