基于DWC2的USB驱动开发-0x08 GLPI接口详解

基于DWC2的USB驱动开发-0x08 GLPI接口详解

描述

基于DWC2的USB驱动开发-0x08 GLPI接口详解 (qq.com)

1.1 前言

进行USB驱动开发,有必要了解整个数据流涉及的设备,而PHY是重要的一环,它负责物理层的处理,是模拟数字的桥梁。而PHY的了解重点是其和LINK之间的接口,USB中PHY和LINK之间的标准接口是UTMI,而ULPI是其低引脚的实现。

介绍ULPI之前有必要先了解下GLPI,因为ULPI是基于GLPI的一个具体的实现。

GLPI即Generic Low Pin Interface,通用低引脚接口,是应用于LINK和PHY之间的接口。可以基于此接口定义特定应用的接口,也就是该接口规范是一个通用的接口设计,可以基于此有具体的应用实现,比如基于该接口实现UTMI协议的低引脚接口即ULPI。

1.2信号

- GLPI定义了如下的信号,这些信号是通用的,可以用于传输不同的数据类型。根据应用的不同,数据流可以用于发送和接收数据包、访问寄存器集、生成中断,甚至重新定义接口本身。

- 所有信号都是和clock同步的,如果没有clock则所有信号也可以是异步的。也就是规范本身并没有完全限定死一定要clock,一定要是同步的。

- 作为通用接口,规范并不规定数据流本身,数据流定义是特定应用实现决定的,只要具体的实现明确定义,实现互操作性即可。

- 通常来说控制信号dir、stp和nxt是在假设PHY是数据总线的主机的情况下指定的。当然为了通用性,也并没有完全限定死。如果需要,实现也可以将LINK定义为主机此时则控制信号的方向和前者要颠倒过来。

| 信号 | 方向(以PHY的角度看) | 描述 |

|---|---|---|

| PHY****接口 | 以下都是以PHY作为主机描述 | |

| clock | I/O | 接口时钟.双向都可以,即可以LINK产生该时钟也可以PHY产生该时钟,即对应于PHY时钟的两种模式,后面文章会讲到.如果有clock所有信号都是和clock同步的.当然本规范也没有限定死,即实现也可以没有clock则所有信号都是异步的。所有信号和clock的上升沿同步。 |

| data | I/O | 双向数据总线,空闲时LINK驱动为低,LINK和PHY驱动为非0的数据则表示有数据传输。(为什么? 如果一方驱动为0则另一方怎么驱动? 因为谁低谁强) .从后面总线权限可以看出不会出现主从都驱动总线的情况,因为总线所有权由主机调度,且由dir决定。并且驱动为0只是一个特殊值,用于区别其他正常数据的情况,理论上驱动为全1也可以。这里为什么LINK一定要发一个数据是因为PHY不发数据就拉低dir监听数据,所以CLK上升沿总是会采集到数据用一个特殊值来表示空闲无效数据。 总线的拥有权是由主机决定的,比如PHY作为主机则由PHY驱动dir来决定.在clock的上升沿同步数据即单边沿模式.当然实现也可以设计为双边沿传输数据模式。 |

| dir | OUT | 主机驱动dir决定data总线的所有权.如果PHY有数据需要传输给LINK,则PHY驱动dir为高拥有总线.如果PHY没有数据要传输给LINK则拉低dir,表示LINK拥有data总线,此时PHY监听总线有非0 的数据则表示LINK发过来了数据给PHY.如果PHY不能接收LINK的数据也可以拉高dir.比如PHY的PLL没有稳定时就会拉高dir,此时LINK不能往PHY发非0数据. |

| stp | IN | 停止.LINK拉高该信号1个时钟来停止当前的数据流(LINK到PHY的或者PHY到LINK的).如果此时是LINK发送数据到PHY,LINK拉高stp则表示前一个时钟的数据是最后一个数据.原文是stp indicates thelast byte of data was on the bus in the previous cycle 我觉的从后面波形图理解来说应该不是前一个时钟而应该就是本STP拉高对应的CLK上升沿的数据是最后一个数据。 如果此时是PHY发送数据到LINK,LINK拉高stp则PHY会强制停止本次数据发送,并且PHY会拉低dir,表示交出数据总线控制权给LINK。 |

| nxt | OUT | PHY拉高nxt表示是否还有数据或者是否接收到数据.1.如果LINK发送数据给PHY,PHY拉高nxt表示当前字节被PHY接收了.LINK可以在下一个时钟继续发送数据给PHY.。2.如果是PHY发送数据给LINK则PHY拉高nxt表示后面还有数据LINK可以继续读。 |

1.3 协议

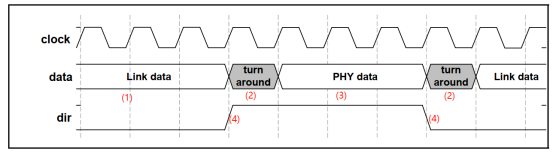

1.3.1 总线所有权

非特殊实现都是PHY作为主机,PHY驱动dir来决定总线的所有权。

PHY需要发送数据时拉高dir,其他时候都是拉低dir监听总线。

如果LINK需要获取总线权可以等PHY发送完不再需要发送数据时PHY主动拉低dir,LINK也可以主动拉高stp一个时钟来结束PHY的发送,让PHY主动让出总线所有权,让LINK来发送数据,这种情况LINK主动请求的则必须进行一次数据发送,PHY才会重新拉高dir重新拥有总线。

dir为0时LINK拥有总线所有权,LINK可以往data总线发数据,

dir为1时PHY拥有总线所有权,PHY可以往data总线发数据,

所有信号都是和CLK同步的,且在CLK的上升沿修改数据,所以CLK的上升沿时dir翻转,

dir翻转时的那一个CLK叫做turnaround,LINK和PHY都不能往data总线发送数据,LINK和PHY也要丢弃该时候的总线数据。

所以在实现时dir可以直接用于控制PHY和LINK的输出缓冲器,只是PHY和LINK两边的使能电平是反的。

- dir为低,LINK拥有总线所有权,LINK可以往总线发数据

- dir翻转时对应的那一个CLK,LINK和PHY都不能发数据,总线上的数据无效,即turnaround

- dir为高,PHY拥有总线所有权,PHY可以往总线发数据

- dir和clock同步,dir总是在clk的上升沿翻转

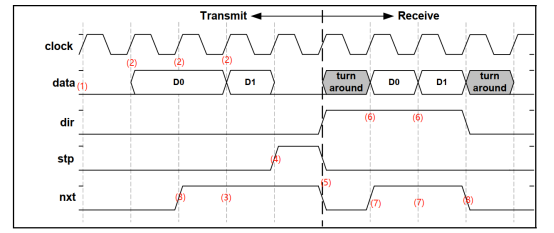

1.3.2 传输数据

- dir为0, LINK拥有总线所有权,而LINK又没有数据要发给PHY,此时就是空闲阶段,LINK驱动data总线为0,此时PHY监听到全0就认为是无效数据.

- dir为0, LINK拥有总线所有权,LINK有数据要发送给PHY,则LINK驱动总线为非0值D0。

但是此时PHY拉低了nxt,表示不能接收,所以LINK只能下一个CLK重发D0

- PHY收到LINK发送过来的数据D0,拉高nxt,表示PHY收到了,这样LINK可以继续发D1。

- LINK主动拉高stp表示结束传输

- stp保持高一个CLK后拉低,此时PHY也会拉低nxt,如果PHY需要发送数据,需要拥有总线权则会拉高dir,否则会继续拉低dir等待LINK的下一次传输。上图中dir拉高了,说明PHY需要发数据了,dir拉高的一个CLK内是turn around总线无效。

- Turn around之后PHY发送数据。

- PHY发送数据,同时拉高nxt表示后续还有数据要发。

- PHY后面没有数据要发了拉低nxt,并且拉低dir交出总线所有权。

所以PHY拉低nxt可以用于掐断数据传输(LINK或者PHY发送的数据), 在传输期间,nxt可以在拉高stp的相同周期中拉高。

从以上可以看出由LINK发送最后一个字节,转到PHY发送第一个字节需要2个周期,即stp要一个周期,turn around需要一个周期。

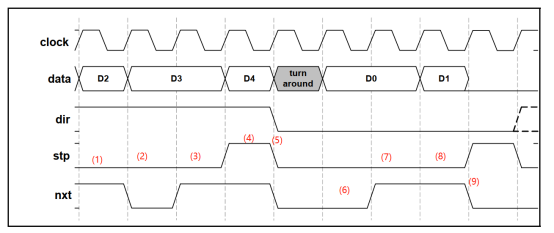

1.3.3 停止传输数据

PHY可以拉高dir用于结束LINK的发送

LINK可以拉高stp一个时钟来结束PHY的发送,此时PHY需要无条件拉低dir,准备接收LINK的数据。PHY必须等接收完LINK的数据才能重新拉高dir。也就是LINK拉高stp以结束上一次PHY的传输,告诉PHY强制拉低dir来使得LINK拥有总线权,这也是LINK主动需要切换到总线所有权的一种方式,这时则LINK必须进行一次发送,只有这样PHY才会重新拉高dir 使得PHY拥有总线权。这里有个未定义行为,假设LINK进行了stp拉高但是又不发送数据或者一直发送数据不stp,那么PHY是不是只能一直等待,不能重新拉高dir拥有总线权了?。

- dir为高 PHY在发送数据D2,nxt为高说明后面还有数据待发送

- dir为高 PHY在发送数据D3,nxt为低说明后面的数据无效

- 这个CLK由于前面一次nxt为低,所以数据无效,LINK不接收, nxt拉高说明下一个CLK PHY又有数据要发

- 这个CLK PHY发送D4, LINK接收,nxt为高表示PHY还有数据要发,但是在此时LINK想要发送数据,于是拉高stp一个CLK.

- Stp拉高一个CLK后要拉低,此时PHY无条件拉低dir交出总线所有权,同时拉低nxt.

- 一个turn around时钟后,LINK发送数据D0,此时PHY拉低nxt为0表示PHY没有准备好接收数据

- 由于上一次PHY没有准备好接收数据,LINK只能重新发D0,此时PHY拉高nxt表示接收了数据D0

- LINK继续发送D1,PHY拉高nxt表示接收了数据D1

- LINK发送stp主动结束发送,此时PHY也要拉低nxt。

之后PHY再看需要是不是要发送数据来决定是拉高还是拉低dir。

1.4 总结

GLPI的接口是比较简单的,需要注意主从机,PHY是主机LINK是从机,

Stp是从机驱动,nxt和dir是主机驱动。

需要注意总线的拥有权由主机决定,主机需要发送是拉高dir拥有总线权,其他时候拉低dir交出总线权监听总线。而LINK可以在dir为高,PHY在发送数据时主动拉高stp一个CLK来请求PHY交出总线权,PHY必须无条件交出,并且必须等LINK发送完数据之后才能重新拥有总线。

所以关键点是了解谁驱动什么信号,总线拥有权的切换,了解这两点就基本了解了该接口的逻辑了。

1.5 参考

《UTMI+ Low Pin Interface (ULPI) Specification Revision 1.1 October 20, 2004》

审核编辑:汤梓红

-

新思 DWC2 的参考手册从哪里可以下载2025-01-22 10562

-

基于DWC2的USB驱动开发-数据不能发送问题分析案例2023-08-08 4966

-

基于DWC2的USB驱动开发-抽丝剥茧再论切换到状态阶段标志DOEPINTn.StsPhseRcvd2023-07-24 4135

-

基于DWC2的USB驱动开发-USB包详解2023-07-23 4644

-

基于DWC2的USB驱动开发-设备类驱动框架2023-07-16 2950

-

基于DWC2的USB驱动开发-高速设备枚举为全速设备问题案例分析2023-07-10 2885

-

基于DWC2的USB驱动开发-USB连接详解2023-07-07 5707

-

基于DWC2的USB驱动开发-IAD描述符详解2023-06-27 491529

-

基于DWC2的USB驱动开发-0x08 ULPI接口协议概览2023-06-02 12151

-

基于DWC2的USB驱动开发-0x07 DWC2 USB2.0 IP 配置参数2023-05-17 4570

-

基于DWC2的USB驱动开发-0x02 DWC2 USB2.0 IP功能特征介绍2023-05-09 14645

-

基于DWC2的USB驱动开发-0x01开篇介绍与新思DWC2 USB2.0控制器简介2023-05-08 6869

-

如何对基于hal库的DWC2 USB IP进行调试呢2022-06-14 1288

全部0条评论

快来发表一下你的评论吧 !