嵌入式软件开发:分析代码性能如何影响 ROI和TCO

嵌入式技术

描述

在上文《嵌入式软件开发的十二大基本要素(一):代码质量》中,我们分析了代码体积如何具体影响投资回报率(ROI)和总拥有成本(TCO)。

本文为白皮书系列第二部分,讲分析代码性能如何影响 ROI和TCO。

应用的性能如何影响 BOM(物料清单)?使用 IAR Embedded Workbench与基于 GCC 的工具相比,能期望有多大的性能提升?

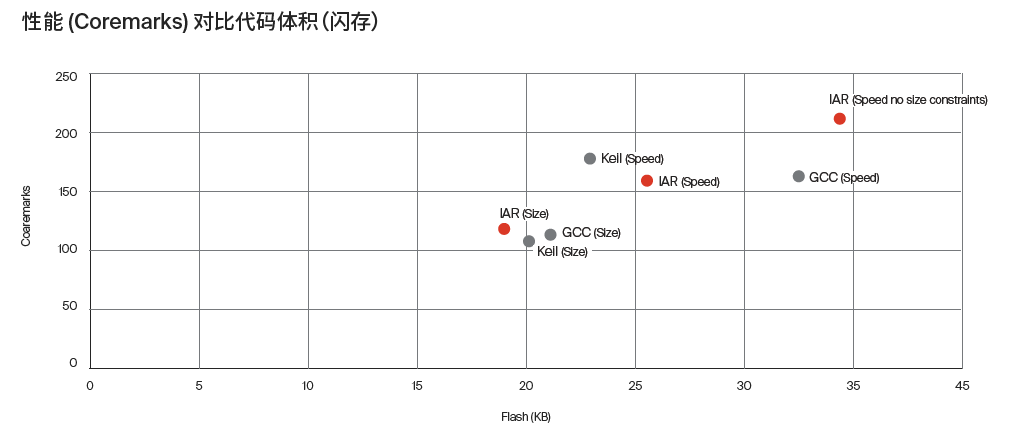

图表1:性能 (Coremarks) 对比代码体积(闪存)

显然,CoreMark 基准是一个很好的参考,因为它试图纳入开发人员做的一些更常见的事情,如矩阵操作、CRC 计算、列表处理(包括查找和排序)等等。因此,它为你提供了一个关于编译器能做什么的“真实世界”的比较,而且它还有防篡改机制,以确保编译器供应商不会通过“手工优化”CoreMark 代码来作弊。可以访问 EEMBC 网站(https://www.eembc.org/coremark/)查找包含各种 MCU 和编译器组合的 CoreMark 基准,但现在让我们来看看 Nordic Semiconductor 执行的一些具体基准。

为达到极致性能进行编译时,IAR Embedded Workbench确实远超其它工具, 特别是与 GCC 的对比,如下图所示。

图表2:性能基准

从这些基准测试中,可以看到 IAR Embedded Workbench 比 Keil 工具链高出 19.1%,比 GCC 工具链高出惊人的 29.8%。建议在 CoreMark 网页上查看当前最新的分数。也可以自己运行基准测试以获得精确的数字。

但是,除了芯片的成本之外,这种类型的优化对普通开发人员来说真的有很大意义吗?为了理解为什么应该关心这个问题,让我们进行一个类似于上文代码体积优化时的分析。

上文中,我们举例了两个完全相同的芯片,只是其中一个有更大的闪存空间,以便在使用效率较低的编译器时容纳更多代码。根据芯片的最大时钟速度进行类似的分析有点棘手,因为大多数参数搜索不允许在最大时钟速度下搜索。

然而,如果我们比较来自同一芯片供应商系列的类似Cortex-M4 芯片,具有相同的封装、相同的闪存大小和 RAM 大小、32 位定时器的数量、D/A 转换器的数量等等。它们的通信接口可能略有不同(例如 I2C 和 SPI 的数量),但主要的区别是它们的最大时钟速度(100 MHz 与 180 MHz)。

那么,180 MHz 比 100 MHz 多多少成本?根据主要经销商的说法,是相当多的。以 1 万件为单位,180 MHz 芯片的价格是每件 3.78 美元,100 MHz 芯片是每件 2.89 美元(截至 2022 年 11 月)。这意味着,如果必须提高到更大的时钟速度以获得应用所需的性能,这意味着 30.8% 的差异。对于 1 万个单元的生产,这意味着超过 9 千美元的差异。正如所见,速度优化可以对 BOM 产生更大的影响,特别是大批量生产时。

编辑:黄飞

- 相关推荐

- 热点推荐

- 嵌入式软件

-

嵌入式软件开发与AI整合2024-07-31 1811

-

嵌入式软件开发和软件开发的区别2024-01-22 3666

-

嵌入式软件开发流程2023-11-17 583

-

嵌入式软件开发基本要素之代码质量2023-05-15 932

-

IAR嵌入式软件行业白皮书 中文版《嵌入式软件开发的十二大基本要2023-02-28 738

-

嵌入式软件开发做什么?嵌入式开发培训学哪些2021-11-03 1876

-

嵌入式软件开发与非嵌入式软件开发的区别?2021-04-02 3025

-

嵌入式软件开发的优势分析2017-12-21 5766

-

嵌入式软件开发概述2017-10-18 1432

-

诚聘嵌入式软件开发2017-04-24 2961

-

ARM嵌入式软件开发2016-01-15 1320

-

嵌入式软件开发与Embedded-GIS2011-02-28 718

-

嵌入式软件开发的优缺点浅谈2009-11-28 3487

-

什么是嵌入式软件开发2009-04-20 9141

全部0条评论

快来发表一下你的评论吧 !