I2C总线的基本结构

接口/总线/驱动

描述

I2C -1-----I2C的基本结构

引言:我们将讨论一些用于实施I2C硬件的关键设计参数,利用简单、稳健的低成本协议在IC之间进行通信,同时尽可能减少引脚数量。随着外设部件的种类日益增多,I2C能够给系统设计人员带来的好处显而易见:很多器件都会使用I2C接口,这里我们只列举几种可以使用的器件:IO扩展器、温度传感器、光传感器、存储器、键盘扫描仪、压力传感器、湿度传感器、ADC、DAC以及I2C协议中使用的多种其他器件。

1.I2C的结构

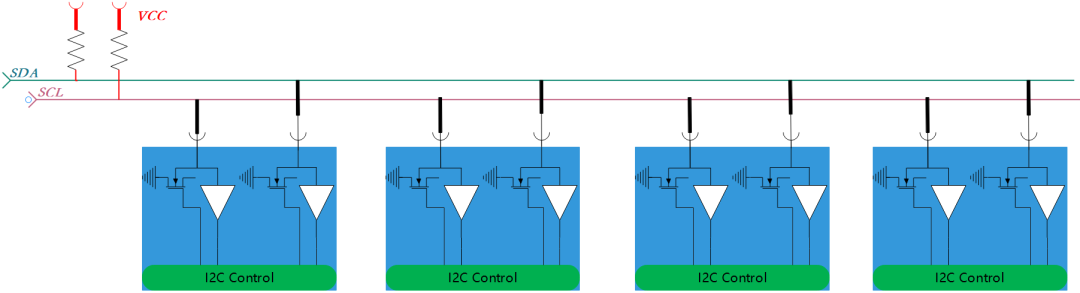

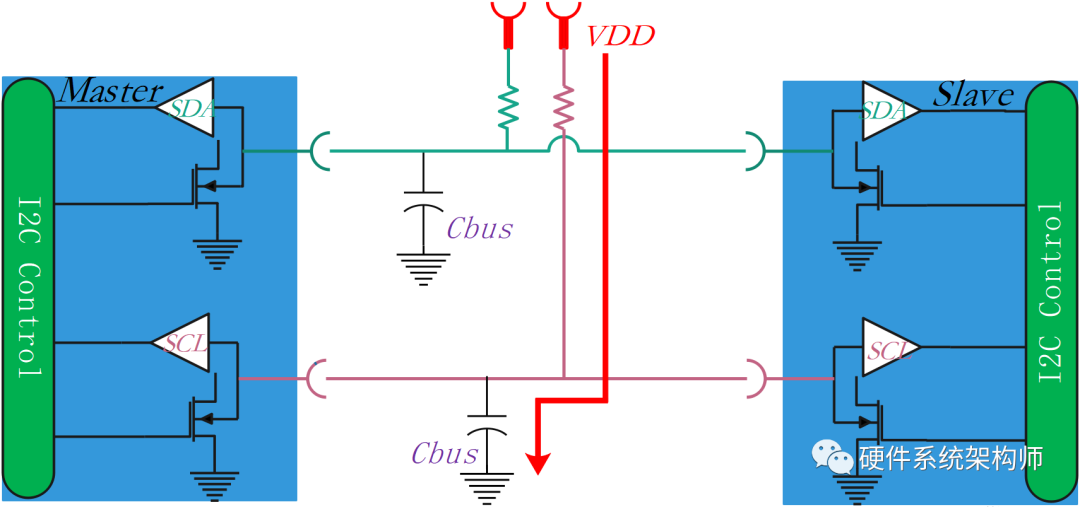

在I2C总线上,如图1-1所示,主设备可以连接到一个或多个从设备。总线只包含两条线:串行数据线SDA和串行时钟线SCL。

图1-1:I2C总线上挂四个设备

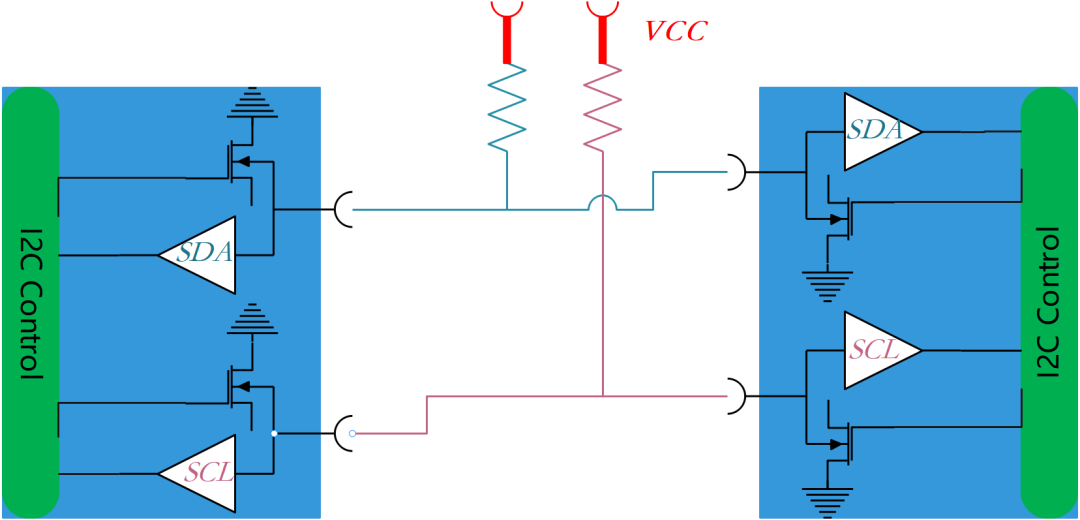

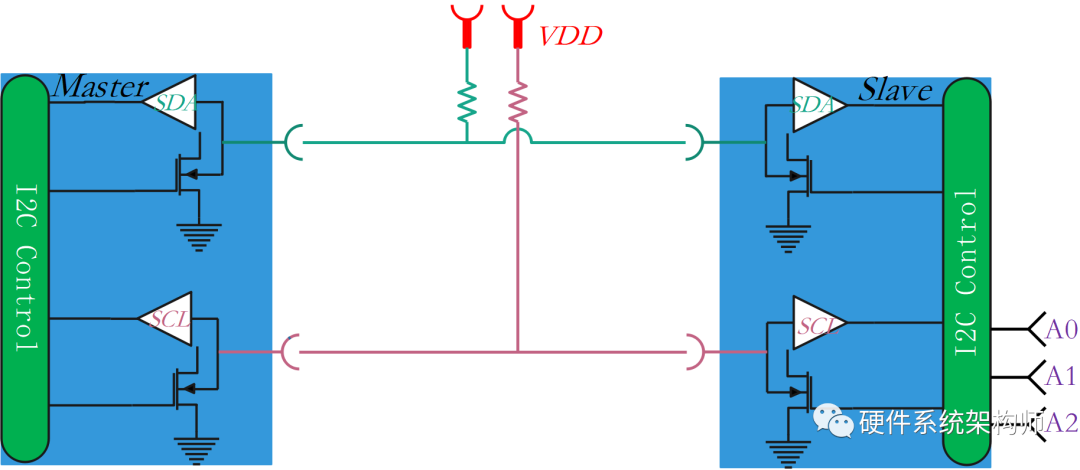

图1-2表示了SDA/SCL线上从设备或主设备的内部结构的简化视图,包括用于读取输入数据的缓冲器和用于传输数据的下拉FET。设备只能将总线拉低(提供对地短路)或释放总线(对地高阻抗),并允许上拉电阻器拉高总线电压。这是在处理I2C设备时要实现的一个重要概念,因为没有设备可以将总线保持在高位。这一特性允许进行双向通信。

图1-2:内部开漏式驱动器和缓冲器

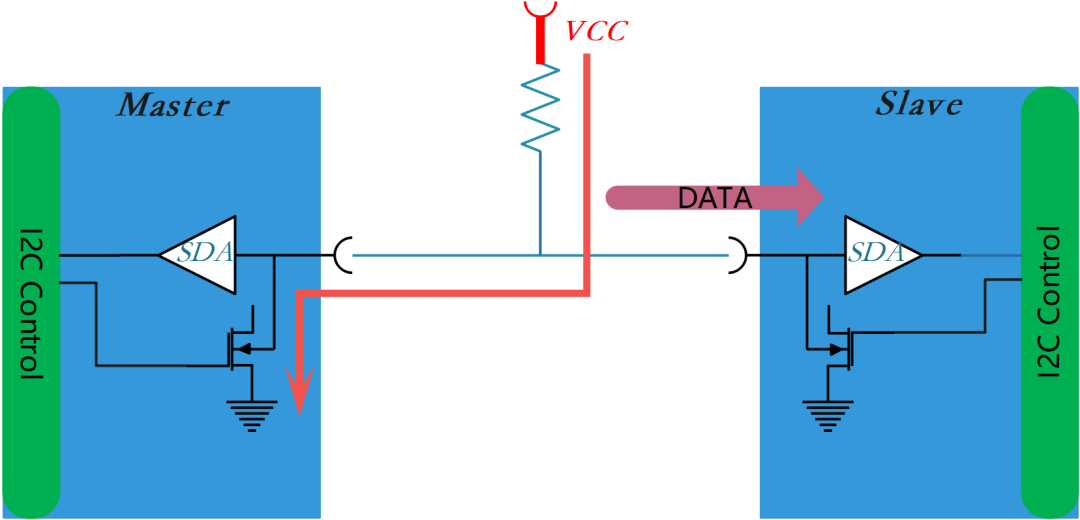

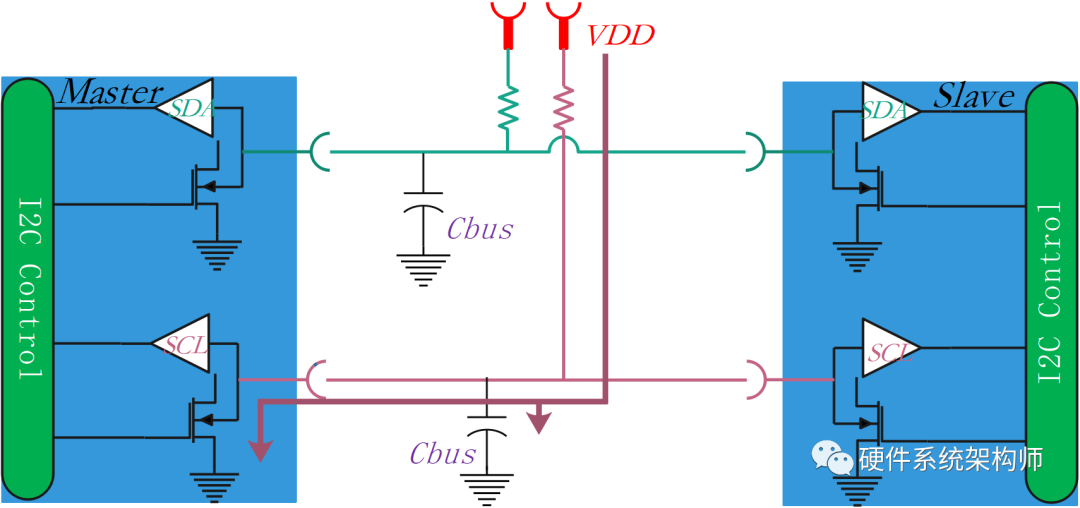

图1-3所示主器件拉低了总线,因此在总线上生成了低电平信号,信号向右传输。

图1-3:主机向从机发信息

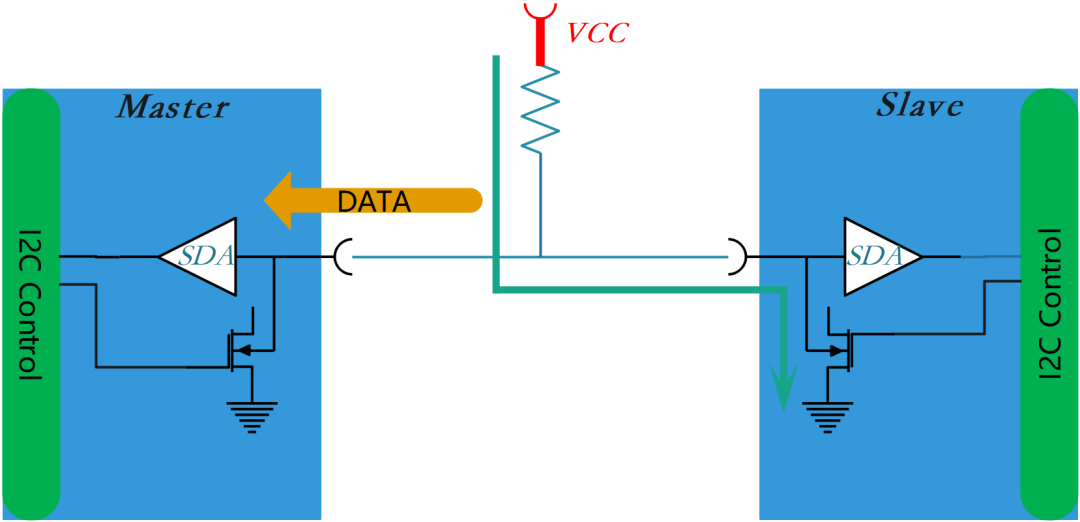

随后,我们可以看到从器件拉低了总线,然后生成了低电平信号(图1-4),信号向左传输。

图1-4:从机向主机发信息

漏极开路是指一种输出类型,它可以将总线拉低至电压(在大多数情况下为接地),或者“释放”总线,让其被上拉电阻器拉高。如果总线被主设备或从设备占用,当从设备或主设备希望传输逻辑高电平时,它只能通过关闭下拉FET来释放总线。这使总线浮动,上拉电阻器将总线电平拉至电压轨,这将被解释为高。由于没有任何设备可以在线路上强制设置高电平,这意味着总线永远不会遇到通信问题,其中一个设备可能会尝试传输高电平,而另一个设备会传输低电平,从而导致短路(电源轨接地)。I2C要求,如果多主机环境中的主机发送高信号,但看到线路低(另一个设备正在将其拉低),则由于另一设备正在使用总线而停止通信。推拉接口不允许这种自由的类型,这是I2C的优点。这样,它就具备了双向性质。

2.I2C的地址和模式

SCL(串行时钟)= 这是一个由主设备驱动的方波,控制数据发送的速度以及数据锁存到从设备的时间。

SDA(串行数据)= 主数据和从数据以半双工方式与时钟脉冲同步放置在这条线上。这条线上的数据包括地址、控制和通信数据。

I2C协议是8位数据结构,这是大多数微控制器和处理器中常用的数据格式。这样主器件 即可使用7位或10位地址与从器件进行通信。8位中的7位表示地址。最后一个位表示消息的方向,高电平表示读取操作,低电平表示写入操作。I2C协议基于地址,这意味着所有从器件都有一个唯一的地址,此地址通常是在硬件中将地址引脚连接到逻辑高电平或低电平而确定的。

• I2C中的典型寻址为7位寻址,具有用于读或写指示的附加位

• I2C总线上的每个设备必须具有唯一地址

• 重复地址将导致通信错误

• 某些设备可能具有引脚可编程I2C地址

图1-5:带器件地址编程引脚

在图1-5中,我们会看到地址引脚A2、A1、A0拉至接地。这样二进制的地址 就是1、1、1、0、0、0、0,以十六进制表示为70。有些从器件没有地址引脚,而是采用无法更改的静态内部地址,而有的则是采用寄存器配置内部地址,但它有一个默认地址。让总线采用并联连接是一种别出心裁且非常有用的做法,原因在于器件非常简单,可以连接到总线上的任意位置。此外,还可以随时连接这些版本的从器件。

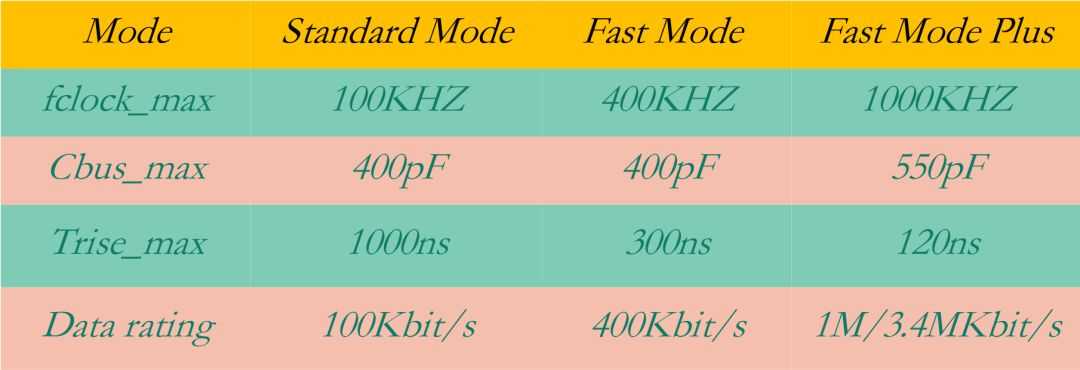

I2C总线具有多种运行模式。每种模式都涵盖多个运行时钟频率并具有多种用来约束协议的限制。对每种模式最重要的要求是最高时钟频率、最大总线电容和最长上升时间,I2C标准中定义了所有这些要求。三种最常用的运行模式包括:标准模式,运行频率介于0-100KHZ之间,最大总线电容为400pF,最长上升时间为1000ns;快速模式,运行频率介于0-400KHZ之间,最大总线电容为400pF,最长上升时间为300ns;以及超快速模式,运行频率介于0-1000KHZ之间,最大总线电容为550pF,最长上升时间为120ns。表1-1:

表1-1:运行模式一览

3.I2C的总线电容

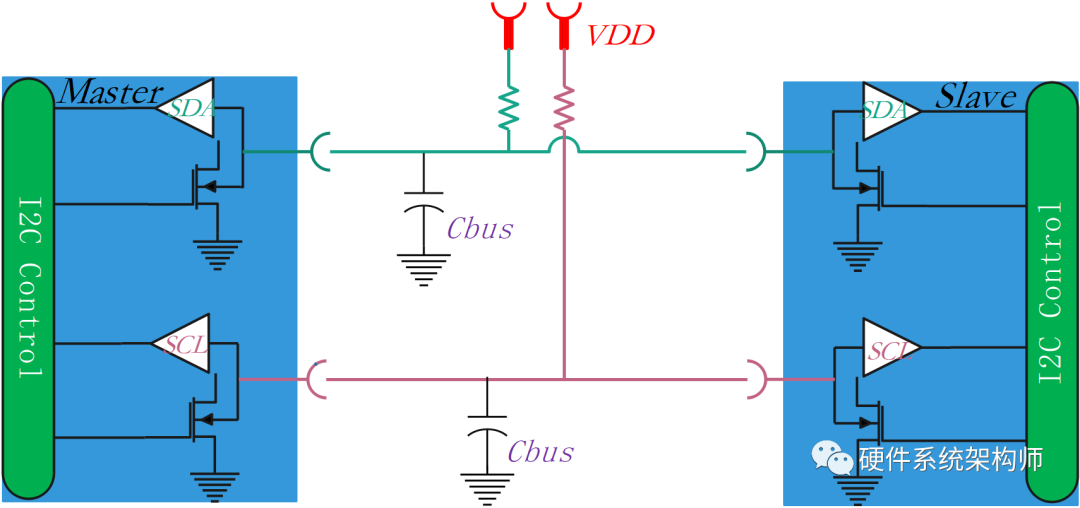

I2C协议物理层是一个简单的双线总线,利用开漏架构实现双向通信,而不像其他接口那样使用推挽或差分驱动器。主器件和从器件具有用于SCL和SDA的输入缓冲器,并可以具有用于SCL和SDA的开漏驱动器,始终存在一个用于生成高电平的外部电路。在大多数情况下,此操作由上拉电阻器执行。这表明主器件或从器件都可以 使用开漏驱动器在总线上拉低,以生成0或低电平。也就是说,会打开N通道,在某些情况下是双极NPN。 高电平完全取决于上拉电阻器。必须注意的是,I2C标准为每种运行模式指定了 最大总线总电容。这包括总线上由于迹线而产生的寄生电容(寄生电容的计算方式后面会讲到),此电容是总线及其回路接地的宽度、长度、电介质材料以及它们之间的距离的一个函数,如图1-6所示。总线中的每个器件也会导致总线的电容增大。

图1-6:I2C总线上的总线电容

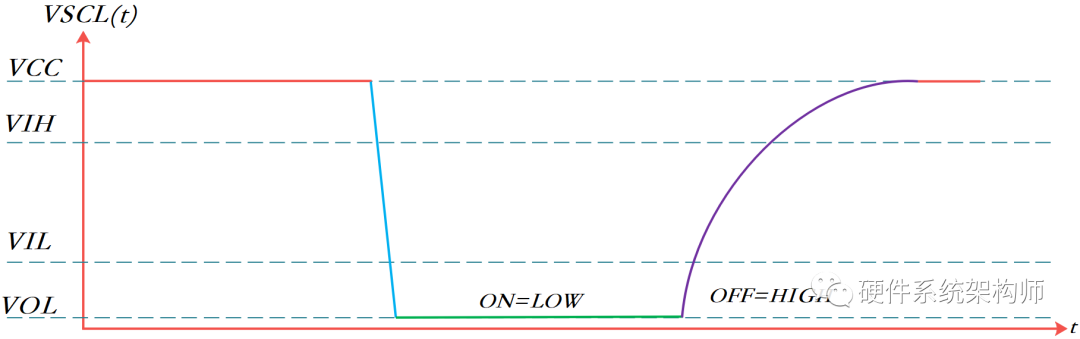

I2C标准为每种运行模式限制了总线电容Cbus的总量,此值定义了最高时钟频率。为了满足所使用运行模式的时序要求,我们需要保持在最长上升时间规格内,图1-7表征了总线电容的充放电效应导致上升沿变缓。

图1-7:总线电容充电效应带来的影响

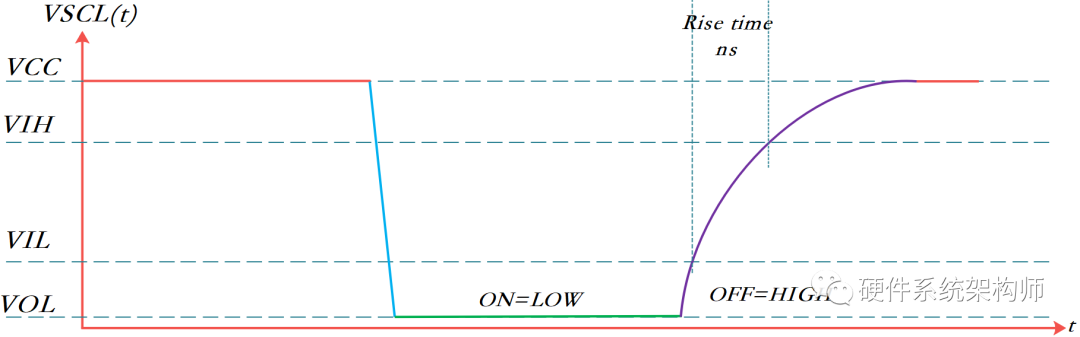

SCL和SDA的最长上升时间规格由我们的上拉NC总线所创建的RC时间常数控制,并被定义为从VIL过渡到VIH时所花费的时间如图1-8定义。

图1-8:Rise time 定义为30%-70%

-

I2C总线完全版——I2C总线的结构、工作时序与模拟编程分享2017-09-21 2100

-

i2c总线ppt(I2C总线器件应用)2008-08-13 1377

-

i2c总线的特点2009-08-05 2673

-

什么是i2c总线2007-11-05 4220

-

并口模拟I2C总线的设计2008-09-11 4733

-

基于CPLD的I2C总线接口设计2011-02-12 1420

-

I2C总线的结构、工作时序与模拟编程2015-08-05 591

-

基于51的I2c总线2016-01-13 1909

-

I2C总线的结构介绍2016-02-29 1787

-

I2C总线的构成及其在多机通信中的应用2017-10-20 1247

-

I2C总线的结构、工作时序和模拟编程2017-10-24 1305

-

i2c总线的结构和应用实例2017-12-06 3717

-

i2c总线用来做什么_i2c总线数据传输过程2020-11-24 9255

-

I2C总线的基本通信总结2021-08-26 20575

-

I2C串行总线协议是什么?I2C总线有哪些优点?2023-09-12 3326

全部0条评论

快来发表一下你的评论吧 !