基于DSP48E1的FIR滤波器设计

描述

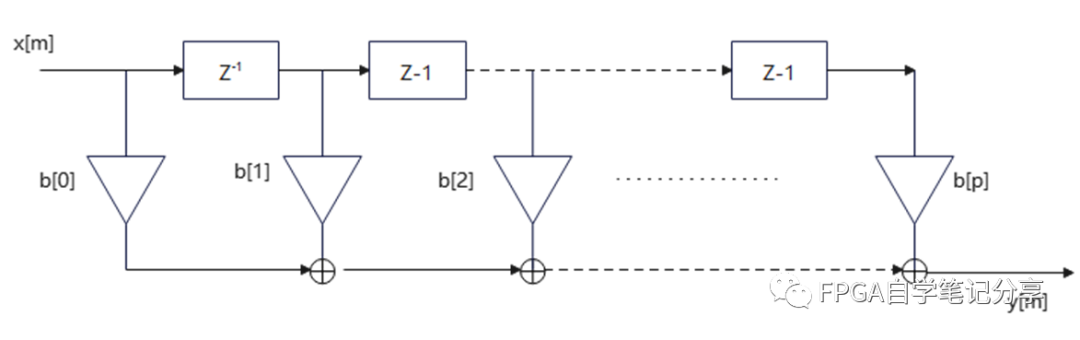

FIR滤波器公式为:

y[m] = b[0]x[m] + b[1]x[m-1] + …. + b[p]x[m-p]

其运算结构如下:

详细的计算过程为:

可以看到需要p+1个乘法器。

在数字信号处理中为了保证时延稳定性以及节省乘法器,通常使用对称系数的滤波器 ,即:

b[0] = b[p] b[1]=b[p-1] …..

此时滤波器结构为:

此时fir的卷积计算可以化简为:

y[m] = b[0]x[m] + b[1]x[m-1] + …. + b[p]x[m-p]

=b[0] (x[m]+x[m-p]) + b[1] (x[m-1] + x[m-p-1]) +….

此时滤波需要的乘法为ceil((P+1)/2),可以发现这种结构将节省一半的乘法器。

此时我们回头看一下dsp48e1的结构(详细可见FPGA的底层资源之DSP48E1),发现dsp的结构中就有预加、乘法、级联累加(红框所示),刚好用来实现对称结构的fir滤波器。

可以得到dsp48e1实现fir滤波器实现结构为:

在回顾一下之前讲dsp48e1使用的重点:

inmode使用00101,让A、B、D三个端口对齐输入,C延后两个clk

opmode[3:0]使用0101,使用M作为X,Y的数据;

DSP48E1使用总结:

1、 A、B、D三个端口对齐在同一时刻输入;

2、P在数据 A、B、D输入后的第四个clk输出;

3、C数据在数据 A、B、D输入的第二个clk输入;

4、Pcin级联时数据要在数据 A、B、D输入的第三个clk输入;

5、 OPMODE,ALUMODE在数据 A、B、D输入的第二个clk输入;

OPMODE的配置说明:

好了,dsp48e1实现对称系数的fir滤波器的结构就是这个样子了,大家可以尝试编写一下fir滤波器,下一篇文章上代码和仿真。

-

FIR滤波器代码及仿真设计2023-06-02 2832

-

DSP48E1详解(3): DSP48E1属性2022-07-25 7158

-

7系列FPGA DSP48E1的参数特点概述2022-06-21 3638

-

DSP48E1详解(2):简化DSP48E1片操作2021-01-29 1753

-

如何简化DSP48E1片操作2021-01-27 1394

-

7系列FPGA DSP48E1片的特点2021-01-08 1802

-

DSP48E1的属性详解2020-12-23 1394

-

使用DSP设计和仿真FIR滤波器2020-09-01 1216

-

为什么BUFG驱动DSP48E1的CE会出现问题?2020-06-12 1424

-

System generator DSP48E1 (1):端口说明2017-02-08 1300

-

fir滤波器的dsp设计2008-01-26 810

-

什么是fir数字滤波器 什么叫FIR滤波器2008-01-16 17695

全部0条评论

快来发表一下你的评论吧 !