高速信号集成电路测试方法

描述

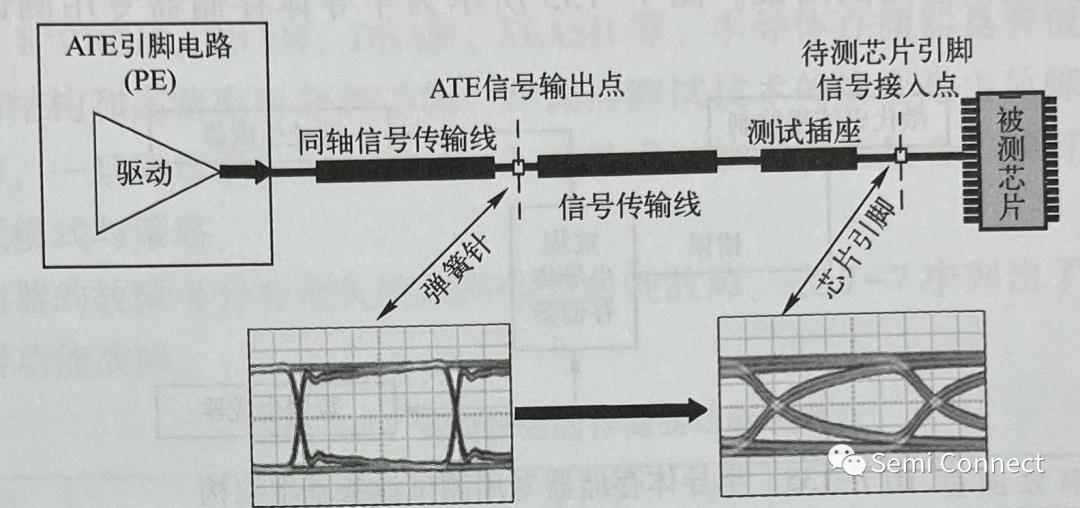

随着集成电路技术的发展,高速信号的设计技术指标不断更新,系统中的数据传输速率已经提高到数十 Gbit/s 乃至数百 Gbit/s,这就给测试系统、测试硬件设计、测试信号传输质量等带来了新的挑战和更高的难度。我国采用的通用方案是通过误码率测试分析对高速接口电路性能进行评价,但这种方法测试效率低,且无法系统、全面地评价高速接口的电平和时序特性,以及可靠性等。高效、系统性的测试评价方案是应用自动测试装备 (ATE),结合高端 ATE 的高质量资源、砂件设计技水及测试算法开发,不仪可以保证高速信号测试位输的质量,还可以实现对高速信号芯片智能化,自动化的全面性测试评估。图所示的是高速信号从ATE输出端到被测芯片引脚的变化。

通常,测试中评价高速信号的参数包括误码率(BER)、眼图(EveDiagram)、电压摆幅(Voltage Swing)、共模电压 (Gommon Mode Voltage)、输出偏斜 (Output Skew)、抖动(Jitter) 等。评价高速串行数据传输端口特性的主要参数如下所述。

(1) 高速端口电压特性参数:主要包括共模输人电压范围、差模输人电压范围.预加重电压和去加重电压的幅度、共模输出电压、端口漏电。

(2)高速端口时间特性参数:主要包括高速信号的频率范围、输出信号的上升/下降时间、发送/接收时延。

(3)传输可靠性特性参数:主要包括本地时钟抖动容限、高速串行信号输人抖动容限和高速串行信号输出抖动幅度。

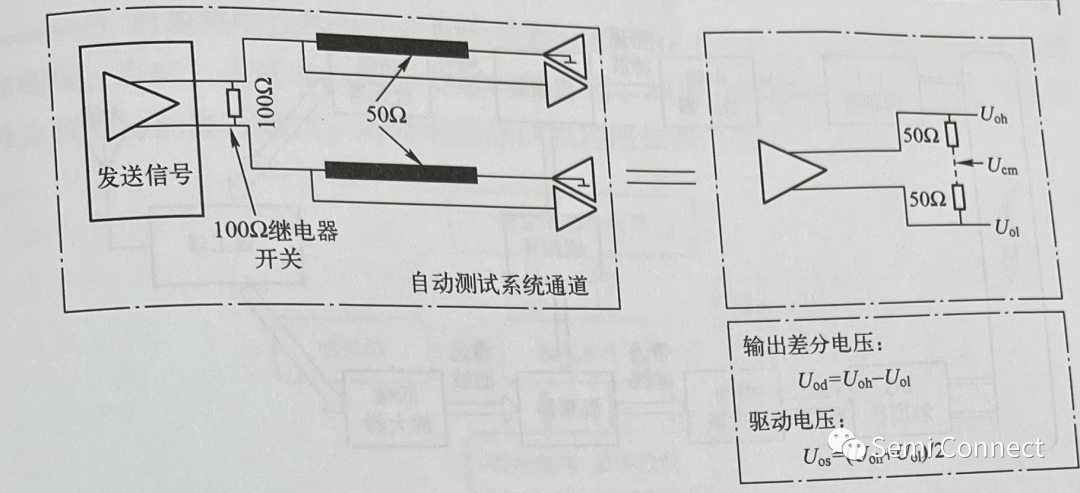

进行高速信号测试时,为解决低电压差分信号 (Low Voltage DifferentialSignals, LVDS)的测试难点,可以将自动测试系统的两个差分通道 (DifferentialChannel)与待测芯片的发射端或接收端相连,并在待测芯片附近设计 100Ω的电阻作为终端。图所示的是典型 LVDS 发射芯片测试方案。

日前,主流高速信号集成电路测试系统驱动电平的精度可达 10mV,比较器的最小过驱动(Overdrive) 电平为 50mV,可以满足 LVDS 高速小信号测试的要求。但末来下一代超高速信号将会给测试带来更多的挑战,需要从新波形和系统设计仿真、频谱和信号分析、光通信和高速测试等方向研发更加灵活、可靠的测试方案,以期获得准确、稳定的测试结果。

审核编辑:汤梓红

-

集成电路代换方法与技巧2010-09-19 2245

-

集成电路应用电路识图方法2013-09-05 2002

-

电子元器件基础:集成电路应用电路识图方法2015-08-20 7860

-

集成电路应用电路识图方法分享2018-07-13 2624

-

集成电路应用电路图的功能和识图方法2018-08-28 3492

-

集成电路可测性设计方法2021-07-26 1607

-

集成电路电磁骚扰测试方法2009-10-07 751

-

集成电路型号命名方法2009-09-19 2220

-

大规模集成电路相关测试标准2011-05-20 1542

-

集成电路测试技术与应用2016-09-01 1363

-

集成电路测试仪器有哪些_集成电路测试仪组成结构介绍2017-12-20 15439

-

基于ATE的集成电路测试原理和方法综述2021-06-17 2352

-

混合信号集成电路测试方法2023-05-29 3494

-

如何用集成电路芯片测试系统测试芯片老化?2023-11-10 2664

-

集成电路测试方法与工具2024-11-19 2694

全部0条评论

快来发表一下你的评论吧 !