利用FPGA开发板进行ASIC原型开发的技巧

描述

ASIC设计在尺寸和复杂性上不断增加,现代FPGA的容量和性能的新进展意味着这些设计中的2/3能够使用单个FPGA进行建模。然而,这些设计中仍然保留有1/3(那就是说,所有ASIC设计中的1/9)要求一个基于多个FPGA的原型开发板。

在不太遥远的过去,对ASIC设计团队而言,在这类情况下主要的解决方案就是在内部建立他们自己的定制多个FPGA的原型开发板。然而,今天,使用现成的多个FPGA原型开发板——例如,由Synplicity公司的原型开发伙伴生产的开发板——与合适的设计工具相结合能够节省数周时间,否则的话将花费几个月的验证时间以及在NRE费用上花费数万美元。

本文首先讨论了ASIC验证能够采用的主要技术。接着,文章考虑了与使用一个现成的产品相比,建立一个定制的多个FPGA的原型开发板的优势和缺陷。,论文介绍了目前的用于验证大型设计的分割和综合设计工具,其采用内部开发或现成的多个FPGA的原型开发板。

可供选择的验证技术

今天高端ASIC,例如那些在手机、通讯、图形子系统以及信号处理应用中使用的,经常包含多个CPU和DSP内核,其结合了硬件加速器、外围设备、接口和存储器管理内核。(由于这些讨论的目的,术语ASIC被假设包括了ASSP和SoC器件。)所以,为了满足芯片的市场需求,尽可能早的在设计阶段开发、端口、集成、调试和验证任何嵌入式软件的内容。

ASIC的RTL全功能验证——其本身与任何嵌入式软件——是ASIC设计过程中耗费时间和困难的部分之一。统计表明今天ASIC设计中的70%要求重制。除了费用极其昂贵之外,重制能够引起项目失去其市场空间,这将严重损害公司的声誉和金融底线。

对ASIC设计者开放的三个主要验证选择是仿真,模拟和FPGA原型开发。

*仿真:基于软件的仿真被广泛使用,但即使在一个真正的高端(并且,相对昂贵)的计算机平台运行时,其运行比实际的ASIC硬件慢六到十个数量级,这使得其成为一项极大花费时间并且效率极差的技术。为了提供整个系统的尺寸认识,软件仿真能够典型地达到仅仅几Hz相当的速度(那就是,设计的系统时钟相对真实时间每秒钟的几个周期)。实际上,这意味着仅仅在一小部分设计中能够实现广泛的软件验证。

*模拟:基于硬件的模拟是另一个可供选择的方法,但它仍然比实际的ASIC硬件至少慢三个数量级,因为大量的有关的复用技术将验证速度减慢到仅仅500 KHz到2 MHz。此外,这种方法在预算和资源方面(依赖于模拟器的大小,每个相等的门电路成本能够从25美分到一美元)是极其昂贵的。设计者需要的是一种可供选择的方法,这将允许他们以较低的风险和成本投放市场。

*基于FPGA的原型开发:在许多情况下,“快速”验证设计是必要的。例如,就视频处理芯片来说,部分验证可能包含评估视频输出流的主观品质。相似地,在嵌入式软件中验证硬件要求极高的速度。其答案就是使用运行在10到80 MHz速度下的多个FPGA原型开发板,其相等于(或相当于)真实时间的ASIC速度(“真实激励输入,真实响应输出”)。当将设计定制开发板与使用现成的开发板进行比较时,后者——当与恰当的设计工具结合时——能够削减数周时间,不然的话,将花费数月的验证时间并且(在每个相等的门电路为一美分的典型值下)节省数万美元的NRE费用。

所关心的同样是,除了提供一个软件开发平台和硬件的软件验证之外,该公司设计ASIC简单地要求尽可能快的完成设计的全部功能;例如,证明硬件可以进行商业展示。

全定制与现成的原型开发板

大约在本文写作前的三至五年,所有多个FPGA的原型开发板是“建立你自己的”全定制品种。相反,今天有着众多现成的多个FPGA的原型开发板供应商群体。

提供一些参考,传统的硬件模拟目前的市场是每年一亿美元。比较起来,在过去几年中,没有任何人真正注意到,现成的多个FPGA的原型开发板工业已经增长到硬件模拟市场规模的四分之三。

工程师认为任何通用的都是次的。事实上,工程师经常希望建立他们自己的定制原型开发板,因为他们认为其性能将更好,他们相信与真实的世界接口将更容易,这些接口将更接近于他们想要的,他们认为这将减少项目成本,并且这将减少产品推向市场的时间。让我们依次列出这些观点:

*更好的性能:在包含了两个或三个以上FPGA的原型开发板情况下,定制实现方式将超过它的现成对应物的性能是非常不可能的。这是因为设计这样一块电路板要求非常高水平的知识和经验,这只能通过在几年内设计数代这样的电路板得到提高。

*消除创新:如果一项ASIC设计适合单个的FPGA,然后设计和实现一块定制的电路板是相对简单的。比较起来,在一项要求两个FPGA的ASIC设计的情况下,该问题变得非常令人感兴趣;并且,当使用三个或更多的FPGA时,事情变得按指数规律增加复杂性。

*消除接口:如果一项ASIC设计适合单个的FPGA,然后有一些令人信服的原因来设计定制电路板。其中一个原因是,在同一块卡上按照任何接口逻辑实现该FPGA通常是有意义的。然而,在多个FPGA的原型开发板的解决方案中,通过使用很的现成电路板以及集中努力在特制的接口卡设计上,接口问题几乎总是很简单的。

*减少成本:设计和实现高端多个FPGA原型开发板要求大量的设计工程师和版图工程师,这将比简单的购买现成的电路板增加非常大的成本。

*减少产品推向市场的时间:即使对一家设计和实现多个FPGA原型开发板的公司而言,高端电路板的制作能够很容易的花费掉9个月(并且这假设多个工程师和版图设计师分多班倒班工作)的时间。不必惊讶,一个非的团队将几乎肯定花费更长的时间,这能够很容易的造成项目落后于它的进度表,并且失去它的市场空间。作为一个多个FPGA原型开发板设计问题复杂性的例子,考虑来自Dini集团的DN8000K10电路板。Dini集团是Synplicity原型开发计划的合作伙伴成员。

DN8000K10是一个USB 2.0主机逻辑原型系统,其能够用二到十六个高容量的FPGA来组装。在其的配置中,该电路板能够被用于代表保守值相当于24,000,000 ASIC门的原型设计。

DN8000K10的设计和实现共花费九个月的时间。为该项目的一部分,六位版图工程师分两班轮班工作了几个月。终的产品是28层的电路板,其芯片间通讯是在350 MHz下采用低压差分信号(LVDS)实现的。(在设计管脚受限的情况下,每个LVDS管脚对支持集成的SERDES,这能够提供高达10:1的复用。)在这一复杂度上,噪声的处理问题和信号完成性问题要求很高的知识和经验水平。这一水平的电路板完全超过了今天现成的自动布线工具能够找到解决方案的能力的一至两个数量级;所以,每个管脚是“手工挑选”,并且每条路径是“手工连接”——没有使用自动布线(除了该电路板周围的外围设备之外)。

手工分割和综合多个FPGA设计

在手工分割的情况下,任何ASIC中心结构(门控时钟,Synopsys的DesignWare?实例等),在原始的RTL源代码中,在进行分割之前,不得不手工将它们翻译为与它们的FPGA相等同的代码。除其它东西之外,这直接导致了两个分离的代码流,这可能失去同步,从而导致在FPGA原型和ASIC之间所代表的功能不同。

当开始分割处理时,工程师们尝试将不同的功能模块组集合在一起,在这里每组在不同的FPGA上实现。这种组合(分割)以门级的传统方式实现。近,一些流程支持在RTL级分组,此时每个分成的组通过传统的FPGA综合工具,并且仅在这一点上,不同FPGA的实际资源利用是已知的。

所有这些方案都有一个问题,就是对于不同组的面积和资源的影响而言,工程师们是“临时的盲人”,这导致了许多耗时的迭代。首先,工程师根据“A模块可能将消耗‘xxx’的资源,而模块B可能要求‘yyy’的资源”而进行“估算”。这些估算是根据大量“分组”命令,然后综合(在基于RTL分割的情况下),然后是结果的分析,以及然后是大量的“取消组”和“再次分组”命令来估算不同的实现方式。

该任务由于这一事实而进一步混淆,该事实就是这些原型经常被FPGA上的I/O管脚的数量所限制;一个无效的解决方案很容易耗费一个器件上100%的I/O资源,然而与此同时,仅仅其相对少量的内部逻辑资源可以实现。为了克服这些I/O限制,I/O的多重分组和/或在多个FPGA中复制同一个逻辑模块是必要的。(为了达到特定的性能目标,逻辑复制也是经常要求的。)

假设在这种原型中使用的每个FPGA可能有超过1000个管脚,一项管理连接的电子表格方法能很容易地包含几千个单元。不足为奇地是,记录分配给每个FPGA的模块和连接矩阵(在不同FPGA之间的连接)是一项繁重的任务,这将是资源密集型的、耗时的以及容易出错的。

自动分割和综合多个FPGA设计

来自Synplicity的CerTIfy? RTL原型开发工具是业内时间长和强大的多个FPGA分割和综合工具。很令人感兴趣的是,当CerTIfy软件在上世纪90年代晚期创立时,对ASIC设计团队而言,没有任何现成的多个FPGA原型开发板能够得到。在那时,CerTIfy软件被设计成一个ASIC团队设计他们自己的定制的多个FPGA原型开发板的辅助工具。

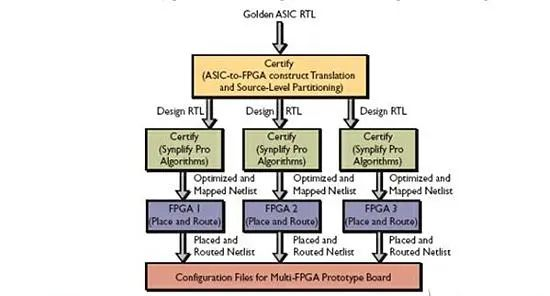

使用CerTIfy软件,工程师们能够定义电路板上的FPGA的数量和类型以及它们之间的互连线。随后,该数据被用于对通过多个FPGA进行ASIC设计自动地分割RTL,并且将被分割的RTL综合成用于FPGA编程的配置文件。

一旦工程师们已经使用Certify工具来定义电路板的基本结构,来自该软件的输出之一是描述FPGA以及它们之间连接的网表。以Verilog来描述的该网表的格式由Synplicity定义,并且是的*.vb(Verilog模版)格式。

设计团队希望建立他们自己的定制电路板今天仍然使用这种技术。这一点使得Synplicity的*.vb格式很快变成这种类型应用的事实上的工业标准。现在,每个现成的多个FPGA原型开发板供应商采用通用的*.vb文件交付他们的电路板,其作为定义每块开发板结构的输入被读入到Certify软件。

Certify工具能够采用Verilog、VHDL和混合语言进行设计。该流程中的个要素是采用Certify软件,自动将任何ASIC专用代码转换为相当的FPGA结构。就目前现成的多个FPGA原型开发板而言,用户简单地通知软件使用下拉式列表框的开发板的类型,该列表框包括来自所有主要第三方供应商所提供的开发板。(换句话说,如果这是一块定制的电路板,Certify工具有能力建立一个在传输过程中的“虚拟的”多个FPGA开发板,接下来这块虚拟的开发板能够作为建立真实电路板的基础来使用。)接下来,Certify软件用于通过多个FPGA自动分割设计(图 2)。

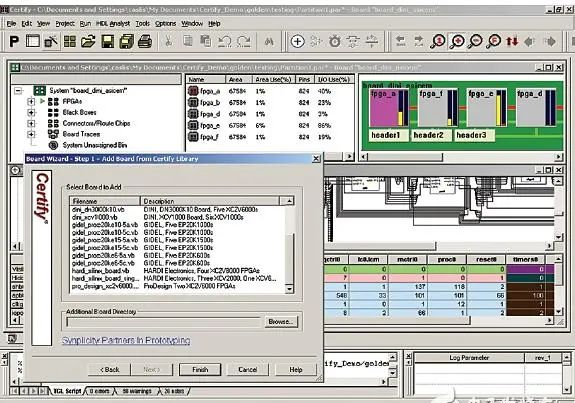

与Certify软件紧密集成在一起的是Synplicity的HDL分析器,其以的层次化的模块图以及接着综合相应的门级电路的形式,自动地产生设计的技术独立的图形视图。Certify和HDL分析器工具在HDL源代码和模块级以及门级电路之间,支持全双向交叉探测,所以允许设计者在设计以及定位感兴趣的信号和逻辑功能之间,进行快速定位。除设计的各种其他视图之外,Certify软件提供一个形成原型开发板的FPGA的图形表示(第6页图3)。这些虚拟器件中的每一个有两个关联的“温度计型”显示:其反映I/O的应用和器件的其他面积/资源应用。

以I/O和相关的逻辑资源以及FPGA和在FPGA之间的布线资源的认识为基础,Certify软件能够自动地实现管脚分配和交互地执行分割——通过简单地拖曳代码模块和将它们下拉到不同的FPGA——或者两种技术可以混合使用。

Certify软件提供大量非常强大的工具来帮助分割任务。例如,接下来的分割,软件能够分析结果和向用户提出使用Certify管脚复用(CPM)的时机,信号的复合设置是一起复用来减轻在相关器件I/O资源上的负载。除了在多个器件上促进逻辑复制外,Certify工具也提供位片应用,其中宽的数据路径结构能够?裂成更小的分支。此外,Certify软件提供成熟的“撕裂”能力,借此将大的模块分解成更小的部分(这些部分能够依次分配给不同的FPGA)。

作为一个候选的分割实现方式就是建立,其他非常有用的特性使其能够被命名和保存。这允许用户维持对多个可选择的分割方案的控制。这种能力能够与Certify软件的影响分析特征一道使用,其允许用户就在该多个FPGA开发板上能够得到的面积和I/O而论,估计布局和/或移动逻辑。而不是用户不得不推测这个逻辑应该被分配给哪个FPGA,影响分析产生关于以那个分割决定为基础的特定信息。

一旦分割已经被执行,Certify软件用于综合与不同的FPGA器件有关的代码流。该工具使用同一个基本的综合技术,就是起重要作用的Synplicity的主导市场的Synplify Pro? FPGA综合引擎。例如,Certify软件充分利用Synplicity的BEST? (Behavior Extracting Synthesis Technology?)算法,其分析RTL和在主要综合步骤前实现优化。并且,Certify工具以拥有Synplify Pro软件的先进的综合能力为自豪,例如资源共享、寄存器平衡、重定时、复制以及再次综合。

这个过程一个关键的方面是Certify软件把不同的FPGA简单看作设计层次中一个额外的层。这意味着该工具提供针对性能优化时序路径的独特能力,甚至当这些路径越过多个FPGA时(Certify软件也能够提供一个时序,其告知设计者原型在硬件被编程之前能够达到的性能)。

总结

建立ASIC原型设计的必要性正在不断增加,按照系统要求其实现是“飞速”地。达到这一性能水平的节省成本的技术就是,建立基于FPGA的原型开发。已经证明有九分之一的ASIC设计师使用多个FPGA的原型开发板,这一趋势正在不断增长。在这种情况下,人们越来越普遍使用现成的原型开发板,这来自Synplicity的原型开发伙伴之一,包括Dini集团、Hardi电子、GiDel和Altera。

当使用与来自Synplicity的Certify RTL原型开发软件时,与建立定制的原型开发板相比,这些技术的电路板在更低的成本上提供了更高的性能,并且减少了产品推向市场的时间。现成的多个FPGA的原型开发板和Certify软件的组合意味着ASIC项目能够节省数月的验证时间,这是在所有的器件和系统层次,允许设计团队与真实的硬件相比进行测试得出的结论,并且可以在设计过程中较早的发现难以察觉的问题。通过较早的允许硬件原型用于软件开发和系统集成,可以更进一步的缩短产品推向市场的时间。

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:利用FPGA开发板进行ASIC原型开发的技巧

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

- 相关推荐

- 热点推荐

- F

-

Renesas FPB - RX140快速原型开发板使用指南2025-12-29 773

-

fpga开发板使用教程2024-03-14 2958

-

fpga开发板与linux开发板区别2024-02-01 4907

-

#硬声创作季 #ASIC 可编程ASIC设计-01.04DE2开发板上FPGA水管工 2022-09-25

-

关于FPGA开发板和原型验证系统对比介绍2022-04-28 3868

-

如何利用现成FPGA开发板进行ASIC原型开发?2021-05-08 2086

-

采用FPGA的原型开发板进行ASIC验证与开发设计2019-05-16 4035

-

NanoBoard 3000系列FPGA开发板助你数日内完成FPGA原型设计2018-10-20 1902

-

利用FPGA开发板进行ASIC原型开发的技巧2017-11-25 1384

-

fpga开发板哪个好?fpga开发板推荐2017-10-23 27747

-

谈谈如何利用FPGA开发板进行ASIC原型开发2017-02-11 1408

-

fpga开发板电路图2012-04-19 2705

-

Altium推出智能FPGA开发板NanoBoard 3002009-11-04 1523

全部0条评论

快来发表一下你的评论吧 !