实现一个在ARM中通过APB总线连接的UART模块

接口/总线/驱动

描述

功能

实现一个在ARM中通过APB总线连接的UART模块(Universal Asynchronous Receiver/Transmitter),包括设计与验证两部分。

项目需求

- 系统时钟最大工作频率满足100MHz,功能时钟满足26MHz

- 具有系统和功能时钟域的复位功能

- 配置接口满足AMBA2.0-APB总线接口时序,总线位宽16bit

- 数据传输满足通用串口时序,奇偶校验功能可配置

- 波特率满足115200,或可配置

- 接收和发送FIFO复位单独可控,触发深度可配置

- 数据收发中断功能可配置

- 数据发送间隔可控

- 具有状态指示功能

- 具有FIFO数据量指示功能

框架

uart框架

设计

- 波特率产生模块

- 根据功能时钟和配置,产生收发波特率时钟。

- 数据接收

- 根据RX波特率时钟接收数据,进行奇偶校验,存放数据到RX FIFO,再由CUP经过APB总线读取数据。内含接收数据状态机。

- 数据发送

- CUP通过APB总线将需要发送的数据放到TX FIFO,根据TX波特率时钟进行数据发送。内含发送数据状态机。

- 寄存器配置

- 实现APB读写寄存器功能,中断操作,功能选择,模块状态指示等。

验证

- 波特率产生

- 产生仿真环境使用的波特率时钟。

- 数据接收

- 仿真环境的接收数据模型。

- 数据发送

- 仿真环境的发送数据模型。

- APB总线

- 仿真环境的APB总线模型,模拟cpu响应中断和实现各种功能。

- 数据对比

- 根据对比发送和接收的数据和时序,产生不同的对比结果,便于仿真时对结果的观察。

- Testcase产生

- 通过不同的激励或配置产生不同的case,验证功能是否符合。

AMBA-APB协议

AMBA

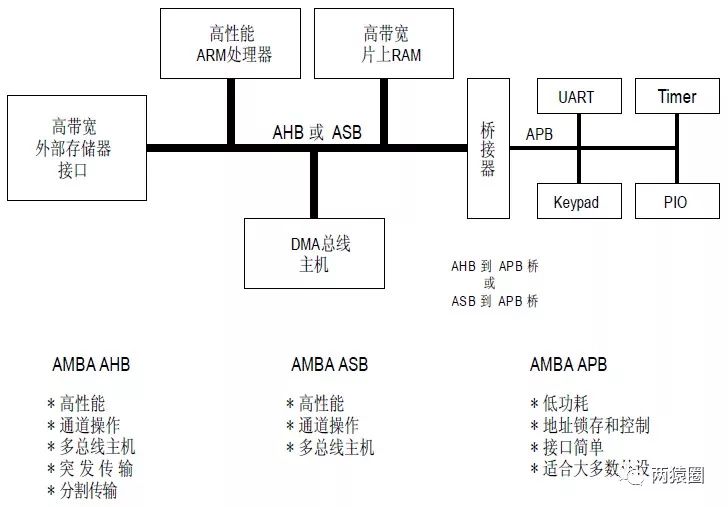

AMBA总线是ARM研发的高级微控制器总线体系(Advanced Microcontroller Bus Architecture),定义了在设计高性能嵌入式微控制器时的一种片上通信标准。AMBA2.0定义了三种不同的总线:AHB、ASB、APB。

AMBA典型系统

典型的基于AMBA的微控制器由一个高性能系统中枢总线(AHB或者ASB)组成,能够支持高带宽外部存储器,包括CPU,片上存储器和其他直接数据存取(DMA)设备。这条总线为上述单元之间大多数的传输提供高带宽接口。在这条高性能总线上也有一个桥接器以连接低带宽的APB,而在APB上连接着大多数的系统外设。

APB

- 接口信号

PCLK (input):APB总线的时钟,所有的传输都和它的上升沿同步。

PRESETn (input):APB总线的复位信号,低有效。

PADDR (input):APB的地址总线。

PSELx (input):APB模块的选择信号,高有效。这个信号选择需要和APB总线传输数据的模块。

PENABLE (input):APB模块的触发信号,标志APB传输的第二个时钟周期。

PWRITE (input):APB总线上的写(高有效),读(低有效)信号。

PWDATA (input):APB总线的写数据信号,由APB总线桥来驱动。

PRDATA (output):APB总线的读数据信号,由APB模块来驱动。

说明:

- APB总线的传输需要两个时钟周期

- input,output是相对APB模块(slave)的输入,输出信号

- “写”操作是将数据从APB总线传输到APB模块,“读”操作是将数据从APB模块传输到APB总线

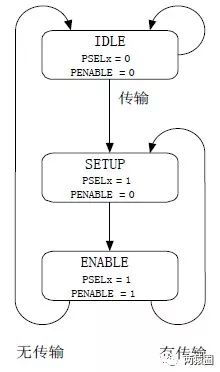

apb状态图

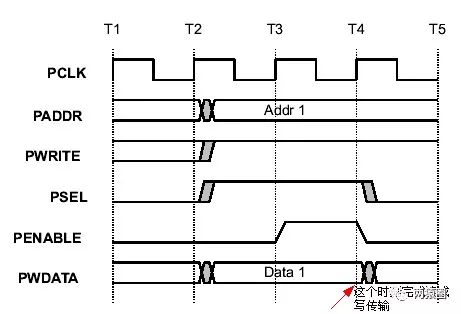

- APB写操作

-

PADDR,PWRITE,PSEL,PWDATA信号有效时刻相同

如果只有一个“写”操作,上述信号只持续两个周期。

如果有多个“写”操作(如Burst方式),PWRITE,PSEL可以保持不变,PADDR,PWDATA每两个周期改变。

-

PENABLE信号在PSEL有效之后一个周期有效,持续一个周期。

如果有多个“写”操作,PENABLE信号在每两个周期内,保持一个周期低电平,一个周期高电平

-

apb写操作时序图

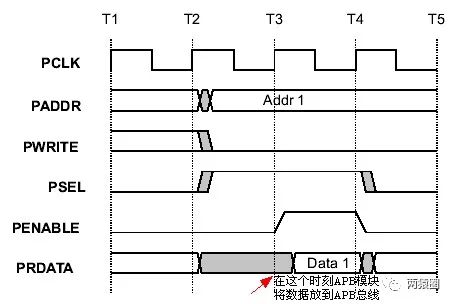

- APB读操作

-

PADDR,PWRITE,PSEL信号有效时刻相同

如果只有一个“读”操作,上述信号只持续两个周期。

如果有多个“读”操作(如Burst方式),PWRITE,PSEL可以保持不变,PADDR每两个周期改变。

-

PENABLE信号在PSEL有效之后一个周期有效,持续一个周期。

如果有多个“读”操作,PENABLE信号在每两个周期内,保持一个周期低电平,一个周期高电平

-

APB模块需要在PENABLE有效的时刻,将“读”操作需要的数据送到APB总线上,并保持一个周期。

-

apb读操作时序图

-

基于hbirdv2的APB总线添加外设(一)2025-10-29 262

-

SOC设计中APB协议总线的工作原理2024-01-17 3819

-

AMBA总线中APB interconnect的介绍2024-01-13 1980

-

AMBA总线—apb简介2023-06-05 3863

-

在SpinalHDL中如何快速地实现总线连接2022-11-28 1468

-

AMBA中的APB总线协议详解2022-06-07 3919

-

分享一个APB slave的verilog实例2022-04-07 3985

-

ARM总线协议AMBA中AHB、APB的区别与联系2022-02-09 2474

-

数字IC验证:ARM总线协议AMBA中AHB、APB的简介、区别与联系2021-12-05 2295

-

基于APB总线的UART接口软核该如何去设计?2021-06-18 3981

-

跨时钟域fifo要如何工作才能最大的优化uart和APB总线之间的连接呢?2019-02-12 3977

-

请问基于APB总线的UART连接接收过程是什么样的?2019-01-22 4111

-

16550兼容的UART,可以连接APB总线2012-08-10 3006

全部0条评论

快来发表一下你的评论吧 !