AMBA总线—ahb简介

接口/总线/驱动

描述

1

AHB概述

AHB(Advanced High-performance Bus),高性能总线的意思。该总线协议是ARM公司提出的AMBA总线结构之一,主要用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。它支持以下特性:

- Burst传输

- Split事务处理

- 单周期master移交

- 单一时钟沿操作

- 无三态

- 更宽的数据总线配置(64/128)

- 流水线操作

- 可支持多个总线主设备(最多16个)

2

AHB协议简介

AHB2 支持多个Bus Master,例如有三个Master,有四个slave,但是同时只有一个Mater可以拿到Bus的访问权。所以,总线的使用权就需要Master去申请,也就需要一个仲裁器(Arbiter)。同时也支持突发传输,分段传输,字节、半字节和字的传输,也可配置总线位宽。

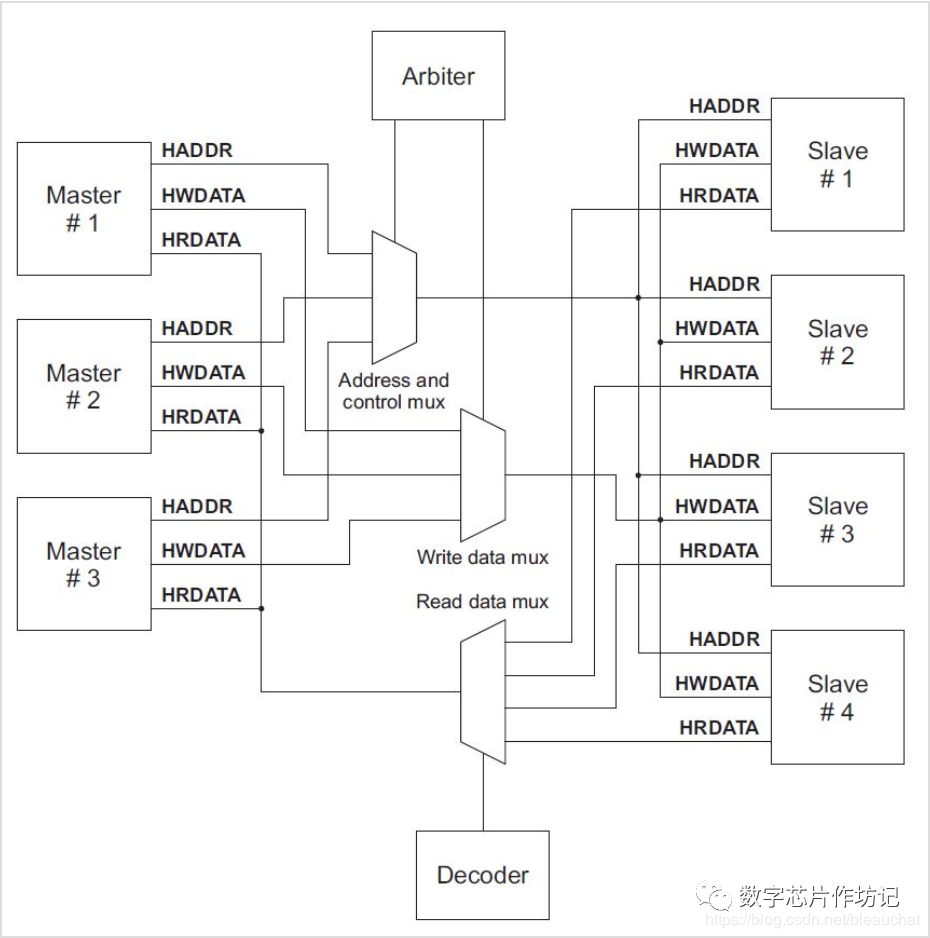

AHB 系统由主模块、从模块和基础结构(Infrastructure)3部分组成,整个AHB总线上的传输都由主模块发出,由从模块负责回应。基础结构则由仲裁器(arbiter)、主模块到从模块的Mux、从模块到主模块的Mux、译码器(decoder)、虚拟从模块(dummy Slave)、虚拟主模块(dummy Master)所组成。其互连结构如下图所示。

AHB2协议要求Slave 的地址空间至少是以1KB为单位,这个要求在AHB-lite也存在。

AHB-lite是AMBA 3,在AHB2的基础上互连逻辑和slave设计上做了简化,为单Bus Master设计的(低端MCU的SoC系统使用的Bus master个数相对比较少)。

当然AHB3系统也是有办法实现支持多个Master的,多个Mater连接到一个MUX输入,slave连接该MUX输出,相当于一个简单的仲裁器。MUX 也可以只连接其中一个Master,这样其他Master就无法访问MUX连接的Slave,相当于该Slave就是连接到MUX上 的Master私有Slave,如下图:

AHB5是AMBA 5,在2015年发布,在AHB-lite的基础上增加功能,支持secure/non-sucure,配合v8系列架构的处理器,引入trustzone机制。

3

AHB信号描述

下表给出了AHB的基本信号:

4

AHB传输

AHB传输分为以下几个部分:

- 主机获取总线使用权:主机向判决器发送总线请求信号,判决器发送应答后主机可以开始传输

- 数据传输:主机向从机传输数据,分为以下两个部分:

- 发送地址和控制信号:包括地址,位宽,突发类型(增量突发和回卷突发)等控制信号,仅一个时钟周期

- 数据传输:进行数据交换,一个或多个时钟周期

- 从机应答:从机通过HRESP和HREADY标记完成状态,对于HRESP,有以下状态:

- OKAY:标记传输完成,当HRESP为该状态且HREADY拉高时,传输完成

- ERROR:标记传输出错

- RETRY和SPLIT:标记传输未完成,主设备仍需要占用总线

关于突发传输,理论上进行突发传输的主设备应当一直占据总线,但是为了缩短等待时间,AHB允许打断突发传输,并在一段时间后重启该突发传输。AHB的基本传输过程由两个部分组成:

- 地址/控制传输:传输地址信息和控制信息,仅占一个时钟周期

- 数据传输:可能需要多个时钟周期,由信号HREADY决定(拉高才结束数据传输)

- 无等待传输

无等待传输下,一个传输与三个时钟沿有关:

-

第一个时钟沿:第一个时钟沿后,主机将地址信息和控制信息发送到总线上

-

第二个时钟沿:第二个时钟沿上,从机采样主机的地址信息和控制信息。第二个时钟沿后,从机将响应信号和数据发送到总线上

-

第三个时钟沿:主机采样从机响应信号和数据,传输完成

- 有等待传输

有等待传输下,数据传输阶段可以扩展,即在HREADY拉高之前,数据传输阶段不结束。要求写数据在HREADY拉高前保持稳定,主机在HREADY拉高后采样读数据

- 流水线传输

AHB总线支持流水线传输,即将传输分为地址-数据两个部分流水进行,本次传输的地址必然在上一次地址之后,本次传输的数据必定紧跟在本次传输地址之后。因此,当上一次的数据传输阻塞导致传输周期增加时,下一传输的地址周期也会相应的变长:

- A1和C1为第一次传输的地址和控制信号

- WD1和RD1是第一次传输的数据,该传输为单时钟即无阻塞的传输,同时发送的还有下一次传输的地址和控制信号:A2和C2

- 第二次传输为多周期传输,因此WD2和RD2占据多个时钟周期,对应的,同时发送的第三次传输地址和控制信A3和C3也被延迟相同的时钟周期数

- WD3和RD3为第三次传输的数据

5

传输类型

传输类型使用端口HTRANS标记,有以下取值:

- IDLE(00):标志主机占有AHB总线,但是没有数据传输发生。从机需要使用OKAY状态回应该类型

- BUSY(01):标志主机占有AHB总线并在进行突发传输,但下一个传输不能立刻发生。从机需要使用OKAY状态回应

- NONSEQ(10):标志主机当前发送的地址和控制信号与上一次传输无关(单次传输就是该状态)

- SEQ(11):标记主机处于突发传输的中间部分,即当前发送的地址和控制信号与上一次地址和控制信号有关

例子如下图所示:

- 第一次传输,开启一次突发传输,因此该地址与上一次传输无关,使用类型NONSEQ

- 第二次传输,无法立刻进行传输,因此使用BUSY标记延迟一个周期,延迟后可以进行传输,且处于突发传输中,因此地址与上一次地址有关,使用SEQ标记

- 之后均为突发传输,均使用SEQ类型

- 突发类型

突发传输分为两类:

- 增量突发:传输过程中传输地址递增。下一次传输的地址是上一次地址加上一个增量

- 回卷突发:猝发的地址范围被限制在一个固定范围之内,传输地址递增,若是超出则回到地址范围的开始的地址。例如从0x34进行增量为4,范围为16的回卷突发,地址顺序为0x34、0x38、0x3c,0x30

突发类型使用字段HBURST标记,含义如下表所示:

注意一次突发传输不能跨越1kB的地址区间,且传输的起始地址必须与数据类型对应,例如传输字数据的二进制起始地址必须满足后两位为00。

- 突发终止

从机通过监控HTRANS发现突发传输的终止:

- 若下一个HTRANS标记为BUSY或SEQ:突发传输未终止

- 若下一个HTRANS标记为NONSEQ或IDLE:上一次突发传输已经终止

若突发传输是提前终止的,如总线控制权被剥夺,那么主机需要在可以进行传输时重建突发传输。例如一个4拍传输仅发送了一拍就终止,主机需要使用INCR类型的突发构建3拍传输以重建。

- 数据总线

当传输位宽不同时,数据总线的使用情况如下所示(小端传输):

-

AMBA AHB协议规范2025-02-11 462

-

聊聊AMBA总线-AHB2023-05-04 2697

-

AMBA中的AHB总线协议详解2022-06-07 5248

-

AMBA AHB总线与APB总线资料合集2022-04-07 5221

-

AMBA、APB、AHB简介2022-02-17 2441

-

ARM总线协议AMBA中AHB、APB的区别与联系2022-02-09 2478

-

STM32菜鸟学习手册——AMBA、APB、AHB简介2021-12-22 1186

-

数字IC验证:ARM总线协议AMBA中AHB、APB的简介、区别与联系2021-12-05 2298

-

介绍AMBA2.0总线2021-09-06 4083

-

基于AMBA总线介绍2021-05-19 2878

-

AHB总线应用教程2017-11-15 22760

-

基于AMBA-AHB总线的SDRAM控制器设计方案2014-01-02 5292

-

基于AMBA片上总线的片上系统2010-09-01 2425

全部0条评论

快来发表一下你的评论吧 !