基于DWC2的USB驱动开发-0x0B ULPI接口寄存器介绍

基于DWC2的USB驱动开发-0x0B ULPI接口寄存器介绍

描述

基于DWC2的USB驱动开发-0x0B ULPI接口寄存器介绍 (qq.com)

一. ULPI(寄存器介绍)

1.1 前言

前面同步模式中我们介绍了寄存器的读写, 对于软件的角度来说无非就是通过LINK的ULPI接口读写PHY的寄存器来设置和获取状态,同时通过ULPI接口来进行USB数据的收发。

只是这个过程主要由硬件LINK完成,软件只需要进行一些中断的处理简单的设置即可。当然在某些必要的时候我们也需要通过软件直接读写PHY的寄存器以进行操作和获取状态,这主要是在某些底层问题调试或者性能分析时需要用到。DWC2提供了直接访问PHY寄存器的寄存器接口,这个后面再讲。

1.2 寄存器读写回顾

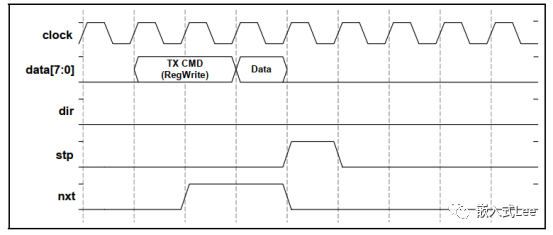

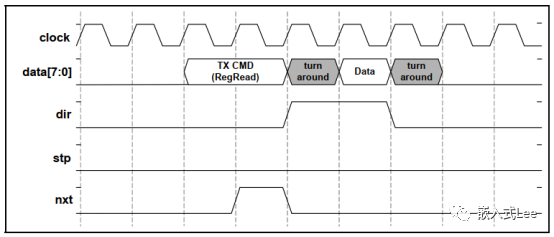

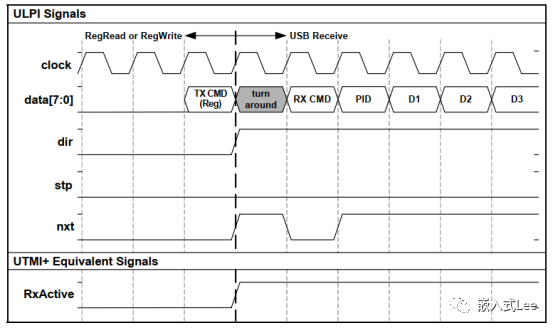

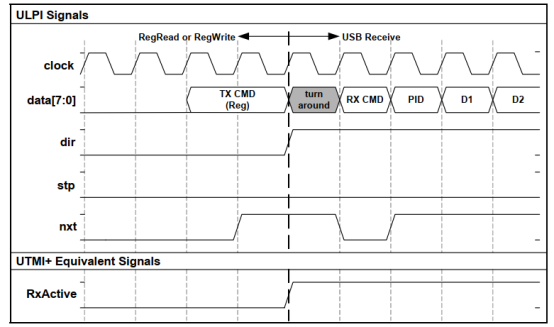

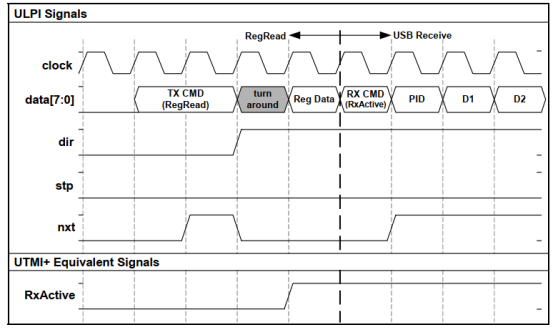

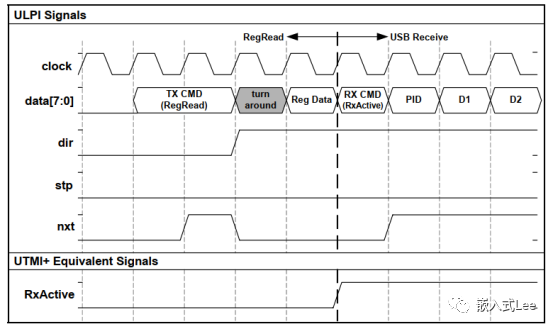

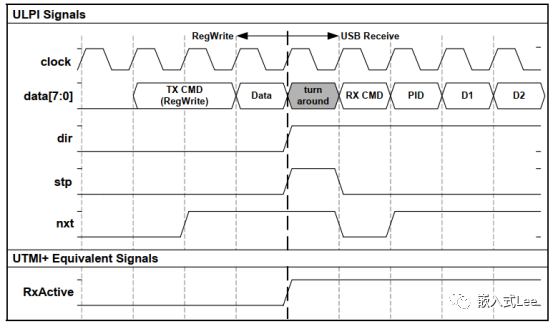

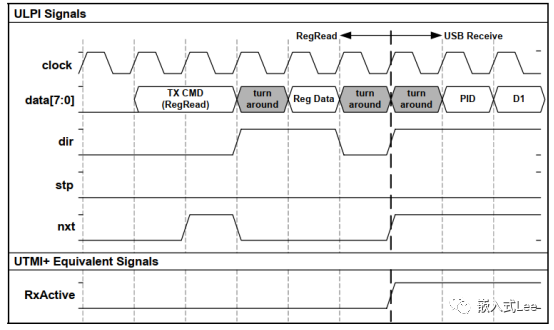

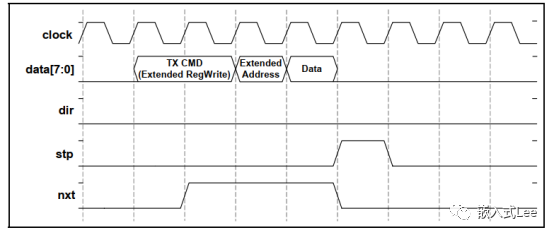

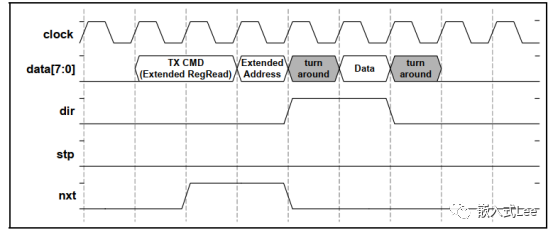

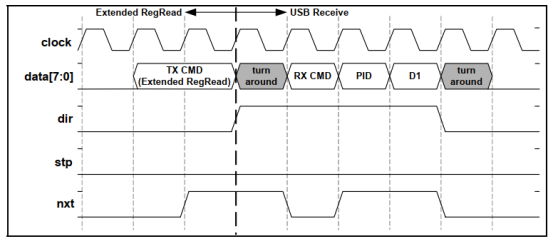

在同步模式介绍中详细介绍了寄存器的读写操作,这里重新回顾下对应的时序图。

立即寄存器写

立即寄存器读

立即寄存器读写在TX CMD时被USB接收中断

立即寄存器读写在turn around时被USB接收中断

USB接收和寄存器读的Data时钟在同一个时钟,USB接收延迟

寄存器读后紧接着USB接收

寄存器写stp拉高时紧接着USB接收

寄存器读紧接着USB接收

扩展寄存器写

扩展寄存器读

扩展寄存器读在扩展地址对应的时钟被USB接收中断

1.3 寄存器表

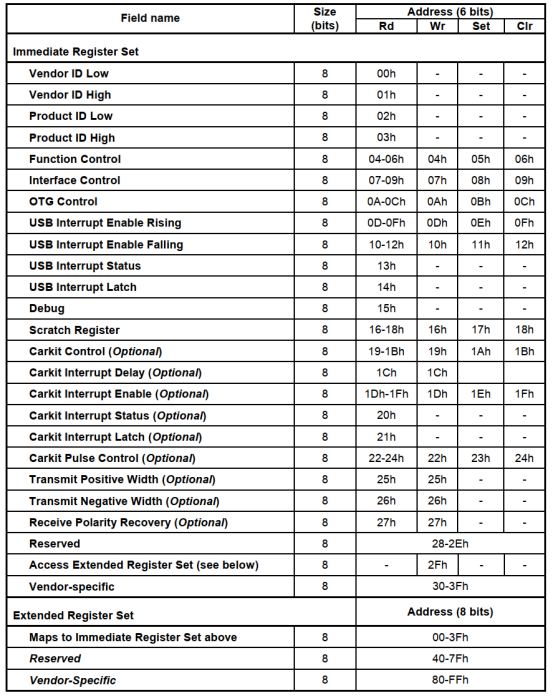

如表所示,ULPI提供了一个立即寄存器集,该寄存器集具有6位地址,该地址构成传输命令字节Transmit Command Byte的一部分。扩展寄存器还提供需要额外时钟周期才能完成的8位地址。立即数寄存器集被映射到扩展地址的低位。也就是说,读取或写入扩展地址“00XXXXXX”实际上将对立即寄存器集进行操作。PHY必须支持立即和扩展寄存器操作。

扩展寄存器访问需要多一个CLK来发送寄存器地址,因为地址大小为8位,不能直接编码在命令字节中了,所以要单独发送。实际上立即寄存器也可以使用扩展寄存器的方式操作,即寄存器地址的高2位为0,所以采用扩展寄存器方式是统一编码所有寄存器的,操作高2位为0的扩展寄存器和立即寄存器操作是一样的。那为什么不统一为扩展寄存器操作一种方式呢,

因为USB关注数据传输带宽,所以要减少其他控制操作:寄存器读写占用的ULPI接口带宽,

所以把关键的寄存器直接编码在命令字中,减少一个CLK的时间,减少寄存器读写占用的带宽,提高数据传输的带宽。

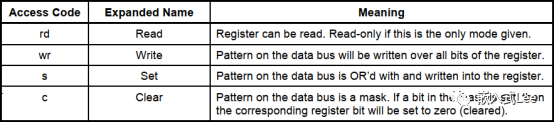

下表的寄存器访问图例适用

支持位操作,在只需要置位或者清除某些位时比"读-修改-写"更高效,

因为ULPI接口即要进行USB数据传输又要进行寄存器读写控制,数据传输才是重点,要保证高数据传输带宽所以要尽量减少寄存器读写占用的带宽,所以增加set clr两种寄存器操作模式,而不是只有rd和wr,不同的操作通过寄存器地址区分。

1.4立即寄存器

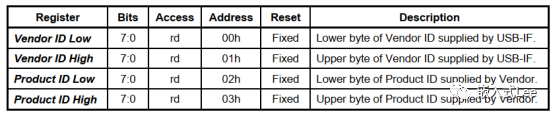

1.4.1 VID和PID

地址:00h-03h只读。

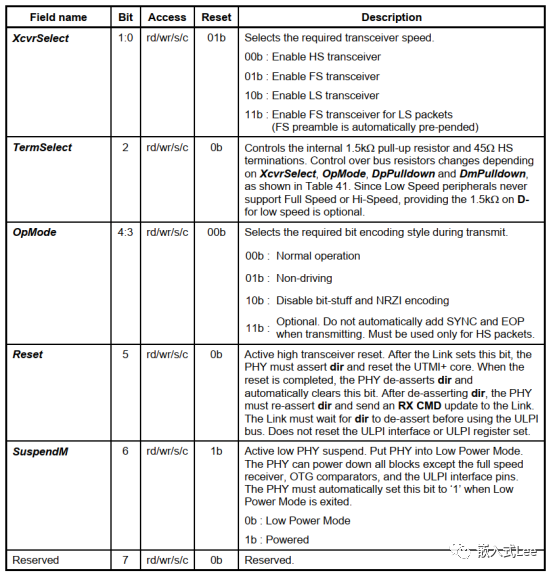

1.4.2 功能控制Function Control

控制PHY的UTMI功能设置,是最频繁使用的寄存器。

地址:04h-06h(读取)、04h(写入)、05h(设置)、06h(清除)。

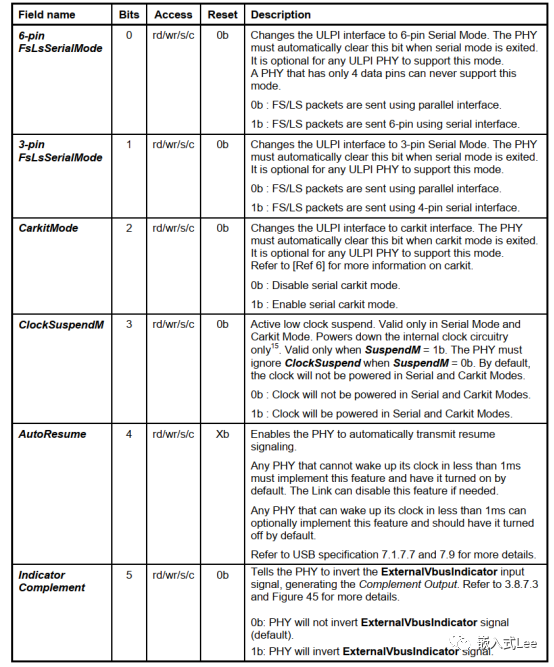

1.4.3 接口控制Interface Control

启用替代接口和物理层功能。此寄存器中的所有位都是PHY的可选功能

地址:07h-09h(读取)、07h(写入)、08h(设置)、09h(清除)。

15:适用于切换到串行或Carkit模式的LINK实现,并且不需要来自PHY的时钟源。

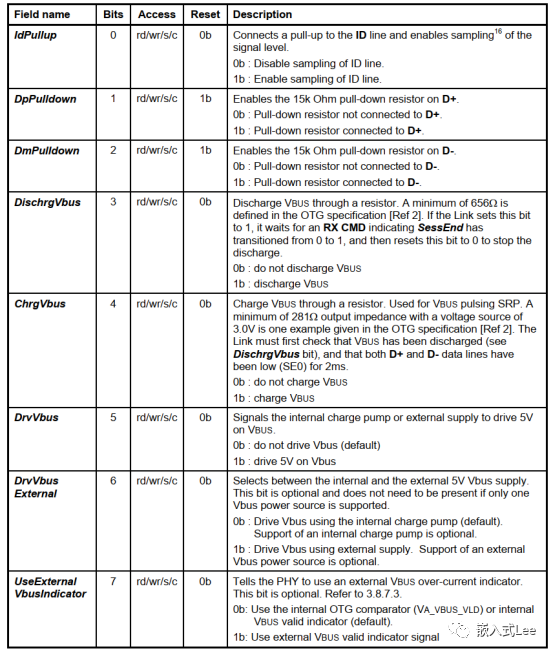

1.4.4 OTG控制 OTG Control

控制PHY的UTMI+OTG功能。

地址:0Ah-0Ch(读取)、0Ah(写入)、0Bh(设置)、0Ch(清除)。

16:如果采用Carkit模式寄存器,上拉电阻器和检测电路应符合[CEA-936A]

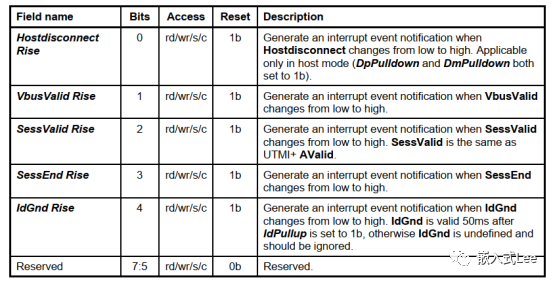

1.4.5 USB中断上升沿使能

地址:0Dh-0Fh(读取),0Dh(写入),0Eh(设置),0Fh。

如果设置,则当相应的PHY信号从低变高时,该寄存器中的位导致生成中断事件通知。默认情况下,所有转换都处于启用状态。RxActive和RxError必须始终立即通信,因此不包括在此寄存器中。当上升沿和下降沿使能都被禁用时,中断电路可以在任何模式下断电。

为了确保时钟断电时能够检测到中断,LINK应同时启用上升沿和下降沿。

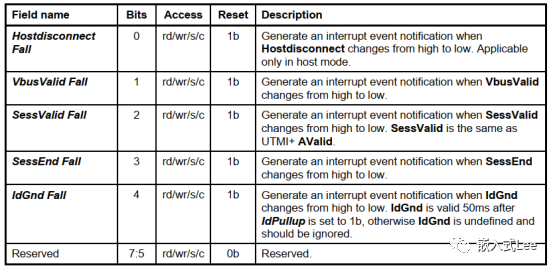

1.4.6 USB中断下降沿使能

地址:10h-12h(读取)、10h(写入)、11h(设置)、12h(清除)

如果设置,则当相应的PHY信号从高变为低时,该寄存器中的位导致生成中断事件通知。默认情况下,所有转换都处于启用状态。RxActive和RxError必须始终立即通信,因此不包括在此寄存器中。当上升沿和下降沿使能都被禁用时,中断电路可以在任何模式下断电。为了确保时钟断电时能够检测到中断,LINK应同时启用上升沿和下降沿。

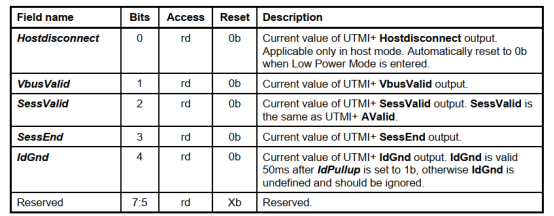

1.4.7 USB中断状态

地址:13h(只读)。

指示中断源信号的当前值。当上升沿和下降沿使能都被禁用时,中断电路可以在任何模式下断电。为了确保时钟断电时能够检测到中断,LINK应同时启用上升沿和下降沿。

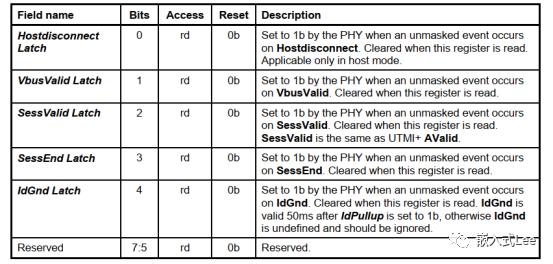

1.4.8 USB中断锁存

地址:14小时(只读,自动清除)。

当在对应的内部信号上发生未屏蔽的改变时,这些比特由PHY设置。当LINK读取此寄存器时,或当进入低功率模式时,PHY将自动清除所有位。无论ClockSuspendM的值如何,当进入串行模式或Carkit套件模式时,PHY也会清除此寄存器。当上升沿和下降沿使能都被禁用时,中断电路可以在任何模式下断电。为了确保时钟断电时能够检测到中断,LINK应同时启用上升沿和下降沿。

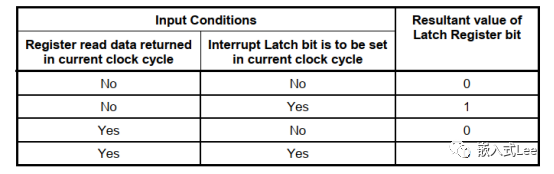

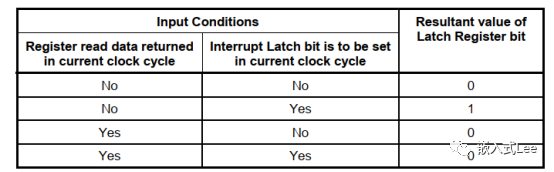

PHY必须遵循下表中的规则来设置任何锁存寄存器位。需要注意的是,如果寄存器读取数据在设置USB中断锁存位的同一周期内返回到LINK,则中断条件会立即在寄存器读取数据中给出,而锁存位不会设置。

注意,LINK在同步模式下读取USB中断锁存寄存器是可选的,因为RX CMD字节已经直接指示中断源。

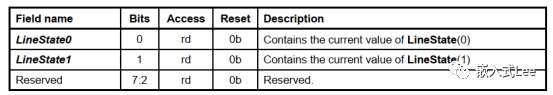

1.4.9 调试寄存器

地址:15h(只读)

指示对调试有用的各种信号的当前值。

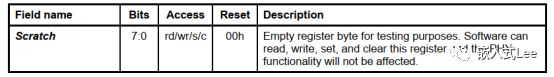

1.4.10 自定义使用寄存器Scratch寄存器

地址:16h-18h(读取)、16h(写入)、17h(设置)、18h(清除)。

用户可自定义写入任何值,可作为测试使用

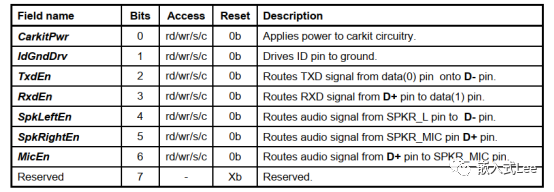

1.4.11 Carkit控制寄存器

地址:19h-1Bh(读取)、19h(写入)、1Ah(设置)、1Bh(清除)。

此寄存器是可选的控制PHY内Carkit电路的操作。如果未设置接口控制寄存器中的CarkitMode位,则忽略TxdEn和RxdEn位。如果CarkitMode位被设置,而RxdEn位未被设置,则数据(1)引脚保持在逻辑高。

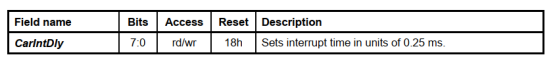

1.4.12 Carkit中断延迟

地址:1Ch(读取),1Ch(写入)。

此寄存器是可选的当Carkit中断电话时,它会在很长一段时间内将D+拉低。如果D+在TPH_DP_INT时间内低于VPH_DP_LO电压阈值,则电话必须检测到中断。

只要设置了Carkit中断启用寄存器中的CarIntDet位,PHY中的Carkit中断定时器就会启用。如果启用,当D+电压低于VPH_DP_LO时,Carkit中断定时器会递增。如果D+电压高于VPH_DP_LO,则车载套件中断定时器复位。当D+高于VPH_DP_LO的时间短至TCR_INJ_WDTH时,Carkit中断定时器必须复位。

当Carkit中断定时器达到存储在CarIntDly中的值时,设置Carkit中断锁存寄存器中的CarIntDet位,并生成中断。

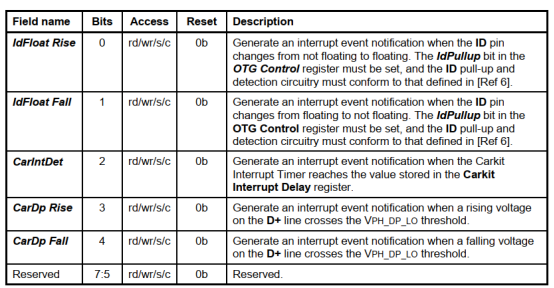

1.4.13 Carkit中断使能

地址:1Dh-1Fh(读取)、1Dh(写入)、1Eh(设置)、1Fh(清除)。

此寄存器是可选的如果设置,则当相应的PHY信号发生变化时,该寄存器中的位会导致生成中断事件通知。默认情况下,此寄存器中的所有位都被清除。

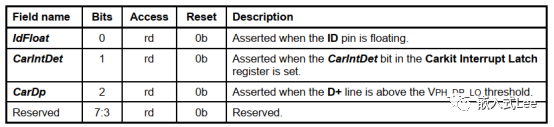

1.4.14 Carkit状态寄存器

地址:20h(只读)。

此寄存器是可选的当carkit中断事件通知发生时,LINK可以读取此寄存器,以确定是哪个事件触发了中断。

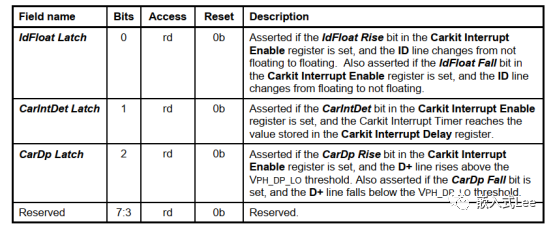

1.4.15 Carkit中断锁存

地址:21h(只读,自动清除)

此寄存器是可选的上一页当LINK读取此寄存器时,或当进入低功率模式时,PHY将自动清除所有位。

PHY必须遵循下表中的规则来设置任何锁存寄存器位。需要注意的是,如果寄存器读取数据在与设置Carkit中断锁存位相同的周期内返回到LINK,则中断条件会立即在寄存器读取数据中给出,而锁存位不会设置。

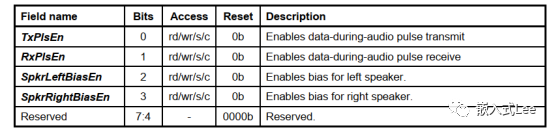

1.4.16 Carkit脉冲控制

地址:22h-24h(读取)、22h(写入)、23h(设置)、24h(清除)。

此寄存器是可选的它在PHY内的音频功能期间控制Carkit数据的操作。如果未设置接口控制寄存器中的车载设备模式位,则忽略TxPlsEn和RxPlsEn。

TxPlsEn:当设置TxPlsSen位,并设置Carkit控制寄存器中的SpkLeftEn位时,PHY应在79UTMI+低引脚接口规范(修订版1.1,2004年10月20日)数据(0)线上的每个上升沿或下降沿后,在D线上输出一个正脉冲,然后输出一个负脉冲。当生成这样的脉冲对时,PHY应执行Carkit规范中定义的步骤。以下步骤列表提供了有关Carkit规格意图的信息。

1.三态驱动D线的扬声器缓冲器

2.将D线驱动至3.3V+/-10%的电压

3.等待传输正宽度寄存器中指定的时间

4.将D路驱动至地

5.等待传输负宽度寄存器中规定的时间

6.停止将D路驱动器至地

7.启用驱动D线扬声器缓冲器

RxPlsEn:当RxPlsSen位被设置,并且Carkit控制寄存器中的MicEn位被设置时,每当在D+线上检测到下降沿超过VPH_DP_LO的车载套件中断阈值时,PHY应切换数据(1)输出。设置RxPlsEn位时,应启用接收极性恢复计时器。

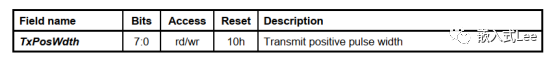

1.4.17 发送正脉冲宽度

地址:25h(读),25h(写)

此寄存器是可选的它指定设置TxPlsEn位时在D线上输出的正脉冲的宽度。%1小时必须支持的最小TxPosWdth为8。必须支持的最大TxPosWdth为64。

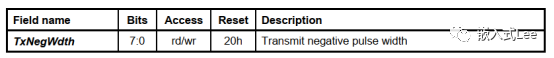

1.4.18 发送负脉冲宽度

地址:26h(读),26h(写)

此寄存器是可选的它指定设置TxPlsEn位时在D线上输出的负脉冲的宽度。%1小时必须支持的最小TxNegWdth为8。必须支持的最大TxNegWdth为64。

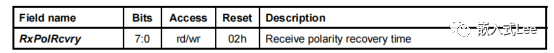

1.4.19 接收极性恢复

地址:27h (Read), 27h (Write)

该寄存器是可选的

当在Carkit中启用了音频中的数据功能时,然后,Carkit通过将非归零(NRZ)的UART信号转换为一系列脉冲,将UART数据发送到手机,将这些脉冲信号通过D+发送到手机。

然后,在每次接收到一个脉冲时,手机中的PHY通过切换到数据(1)线,将这些脉冲转换为NRZ UART信号。如果PHY错误地错过了一个脉冲,或者检测到一个额外的脉冲,那么数据(1)线上的极性将是不正确的。为了从此条件中恢复,当数据(1)行的极性为逻辑极性低时,PHY自动将数据(1)行的极性重置为逻辑高。

只有在设置了Carkit脉冲控制寄存器中的RxPlsEn位时,接收极性恢复才会被激活。时间以0.25 ms为单位测量。必须支持的最小RxPolRcvry为1。必须支持的最大RxPolRcvry为255。

1.4.20 保留

28H~2EH部分保留以后使用。

1.4.21 访问扩展寄存器集

2FH(读/写)

命令字中的低6位填该值,在下一个CLJ中发送8位的扩展寄存器地址。

1.4.22 厂商指定

30H~3FH

厂商自定义使用

1.5扩展寄存器

扩展寄存器集的地址00h到3Fh直接映射到立即寄存器集。对扩展地址00h到3Fh的读、写、设置或清除操作实际是在立即寄存器组上操作。地址40h到7Fh被保留以供将来使用。地址80h至FFh被分配给供应商特定用途。

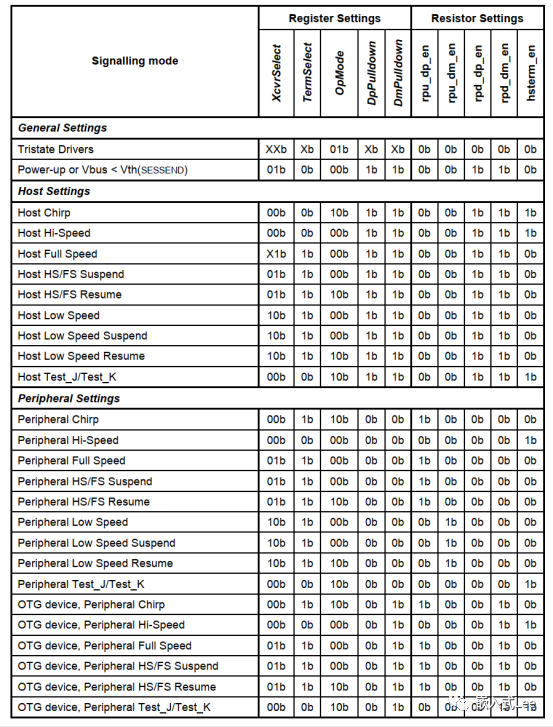

1.6所有上行和下行信号模型的寄存器设置

前面也说过ULPI是通过将UTMI的一部分相对静态的的信号映射到寄存器,通过寄存器去操作这些信号来减少引脚的数量的。

下表显示了LINK必须应用哪些寄存器设置才能实现所需的信号模式。PHY必须根据需要自动生成正确的信号、准备SYNC和附加EOP。该表还显示了由于寄存器设置而启用的电阻器。

以下信号概念上存在于PHY内部。所有电阻器信号均为高电平有效,值1b启用电阻器,值0b禁用电阻器。

1.rpu_dp_en启用D+上的1.5kΩ上拉电阻器

2.rpu_dm_en启用D-上的1.5kΩ上拉电阻器

3.rpd_dp_en启用D+下的15kΩ下拉电阻器

4.rpd-dm_en启用D-上的15kΩ下拉电阻器

5.hsterm_en启用D+和D-上的45Ω终端电阻器。

1.7总结

以上详细介绍了PHY相关的寄存器内容,标准部分是所有PHY都需要按照该规范实现的,还有厂商自定义部分可以自定义。正是因为规范对寄存器功能进行了规范所以LINK部分的IP才能做到兼容通过。

PHY寄存器的内软件开发人员容一般情况接触不到,但是真正遇到底层疑难问题时可能只有通过PHY的一些寄存器才能进行进一步分析,所以也是需要了解的。

审核编辑:汤梓红

-

将LDC1000配置了0X0B寄存器,各寄存器的值都变成了相应寄存器的Deffault值,为什么?2025-01-02 309

-

基于DWC2的USB驱动开发-控制传输中断相关寄存器2023-07-24 5504

-

基于DWC2的USB驱动开发-DOEP接收相关的其他寄存器详解2023-07-19 3032

-

基于DWC2的USB驱动开发-设备类驱动框架2023-07-16 2929

-

基于DWC2的USB驱动开发-USB复位详解2023-07-07 193686

-

基于DWC2的USB驱动开发-0x0E 使用逻辑分析仪分析ULPI数据2023-06-07 3270

-

基于DWC2的USB驱动开发-0x0D PHY寄存器读写代码编写与测试2023-06-06 4740

-

基于DWC2的USB驱动开发-0x0A ULPI接口同步模式介绍2023-06-04 7148

-

基于DWC2的USB驱动开发-0x08 ULPI接口协议概览2023-06-02 12120

-

基于DWC2的USB驱动开发-0x05 DWC2 USB2.0 IP 寄存器介绍2023-05-16 5557

-

基于DWC2的USB驱动开发-0x02 DWC2 USB2.0 IP功能特征介绍2023-05-09 14584

-

基于DWC2的USB驱动开发-0x01开篇介绍与新思DWC2 USB2.0控制器简介2023-05-08 6833

-

MPU6050寄存器介绍2021-12-06 1492

全部0条评论

快来发表一下你的评论吧 !