UART整体的仿真方法和testbench结构讲解

电子说

1.4w人已加入

描述

仿真框架

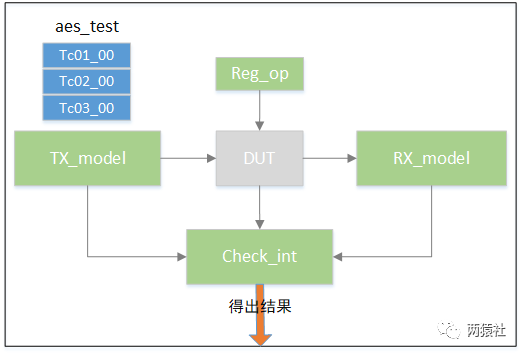

仿真部分结构和设计类似,同样有波特率、接收数据和发送数据模型。仿真的实现比较灵活,不用考虑可综合性。主要实现master功能,配置部分对DUT配置,发送模型发送数据到DUT,接收模型接收到数据后与发送数据进行对比,验证基本功能的正确性。

仿真框架

伤真顶层产生时钟、复位,信号的初始化,测试用例的选择以及全局变量或参数的定义(如寄存器地址和某些多模块需要用到的变量)。

////////////////////////////////////////

`timescale 1ns/1ps

//`define tc01_00

//`define tc02_00

`define tc03_00

module top();

reg clk; // ARM clk

reg clk26m; // 26M function clk

reg rst_; // ARM clk's rst_

reg rst26m_; // function clk's rst_

reg tx_data; // send data line

wire rx_data; // receive data line

wire uart_int; // uart interrupt

// APB signals

reg [3:0] paddr;

reg [31:0] pwdata;

reg psel;

reg penable;

reg pwrite;

wire [31:0] prdata;

reg baud_tclk; // send data baud clk

reg baud_rclk; // receive data baud clk

reg start; // receive data baud enable signal

reg rx_done; // receive one data done

reg w_state; // write reg using signal

reg r_state; // read reg using signal

reg [7:0] tx_data_mem[0:999]; // send data memory

reg [7:0] rx_data_mem[0:999]; // receive data memory

reg [31:0] uart_tx;

reg [31:0] uart_rx;

reg [31:0] uart_baud;

reg [31:0] uart_conf;

reg [31:0] uart_rxtrig;

reg [31:0] uart_txtrig;

reg [31:0] uart_delay;

reg [31:0] uart_status;

reg [31:0] uart_rxfifo_stat;

reg [31:0] uart_txfifo_stat;

// when tx_model is runing a second time ,we don't want tx_cnt clean,

// so defind tx_cnt in top

integer tx_cnt;

parameter clk_period = 10;

parameter clk26m_period = 38;

parameter uart_tx_addr = 4'h0;

parameter uart_rx_addr = 4'h1;

parameter uart_baud_addr = 4'h2;

parameter uart_conf_addr = 4'h3;

parameter uart_rxtrig_addr = 4'h4;

parameter uart_txtrig_addr = 4'h5;

parameter uart_delay_addr = 4'h6;

parameter uart_status_addr = 4'h7;

parameter uart_rxfifo_stat_addr = 4'h8;

parameter uart_txfifo_stat_addr = 4'h9;

`include "UART_baud.v"

`include "reg_op.v"

`include "check_int.v"

`include "uart_tx_model.v"

`include "uart_rx_model.v"

`include "tc01_00.v"

`include "tc02_00.v"

`include "tc03_00.v"

// cases of uart

UART_TOP DUT(

.clk(clk),

.clk26m(clk26m),

.rst_(rst_),

.rst26m_(rst26m_),

.paddr_i(paddr),

.pwdata_i(pwdata),

.psel_i(psel),

.penable_i(penable),

.pwrite_i(pwrite),

.urxd_i(tx_data),

.utxd_o(rx_data),

.uart_int_o(uart_int),

.prdata_o(prdata)

);

// always produce clk

always#(clk_period/2) clk = ~clk;

always#(clk26m_period/2) clk26m = ~clk26m;

// signals initialize

initialbegin

clk = 1'b0;

clk26m = 1'b0;

rst_ = 1'b1;

rst26m_ = 1'b1;

baud_tclk = 1'b0;

baud_rclk = 1'b0;

tx_data = 1'b1;

start = 1'b0;

rx_done = 1'b0;

w_state = 1'b0;

r_state = 1'b0;

uart_tx = 32'h0;

uart_baud = 32'hf152;

uart_conf = 32'h34;

uart_rxtrig = 32'h1;

uart_txtrig = 32'h0;

uart_delay = 32'h2;

uart_status = 32'h0;

tx_cnt = 0;

#50;

rst_ = 1'b0;

rst26m_ = 1'b0;

#100;

rst_ = 1'b1;

rst26m_ = 1'b1;

end

initialbegin

@(posedge rst_) beginend

fork

UART_baud();

check_int();

uart_rx_model();

join

end

initialbegin

@(posedge rst_) beginend

`ifdef tc01_00 tc01_00(10); `endif

`ifdef tc02_00 tc02_00(); `endif

`ifdef tc03_00 tc03_00(); `endif

end

endmodule