怎么设计一个Glitch Free的时钟切换电路呢?

电子说

1.4w人已加入

描述

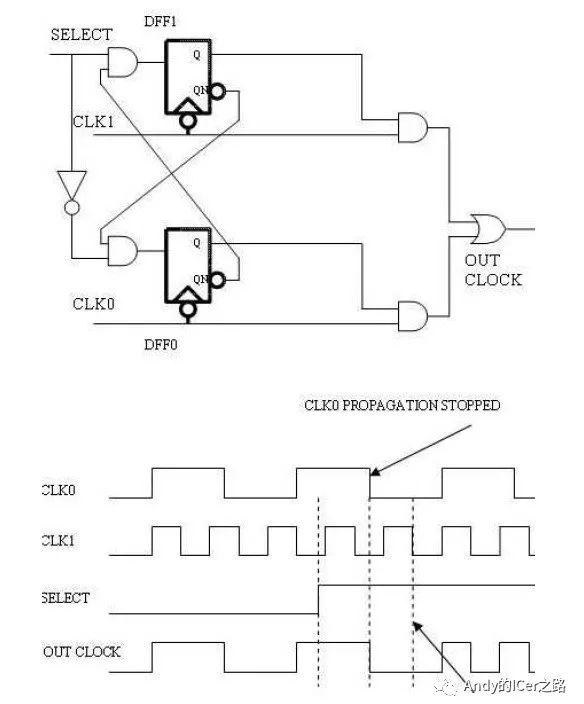

输入sel,clka,clkb,sel为1输出clka,sel为0输出clkb。

一、两个时钟源是倍数的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out1;

reg out0;

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= ~out0 & select;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= ~select & ~out1;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule

二、两个时钟源为异步时钟的关系

module Change_Clk_Source(

input clk1,

input clk0,

input select,

input rst_n,

output outclk

);

reg out_r1;

reg out1;

reg out_r0;

reg out0;

always @(posedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r1 <= 0;

else

out_r1 <= ~out0 & select;

end

always @(negedge clk1 or negedge rst_n)begin

if(rst_n == 1'b0)

out1 <= 0;

else

out1 <= out_r1;

end

always @(posedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out_r0 <= 0;

else

out_r0 <= ~select & ~out1;

end

always @(negedge clk0 or negedge rst_n)begin

if(rst_n == 1'b0)

out0 <= 0;

else

out0 <= out_r0;

end

assign outclk = (out1 & clk1) | (out0 & clk0);

endmodule

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

异步时钟切换电路2014-05-08 6142

-

多时钟设计中时钟切换电路设计案例2020-09-24 6670

-

图解时钟切换电路使用方法2023-01-16 3226

-

数字电路之时钟切换电路解析2024-02-18 5624

-

FPGA的时钟门控是好还是坏?2019-02-21 5921

-

时钟切换时容易出现的问题汇总2022-01-18 590

-

毛刺在时钟切换电路的影响及其防止措施的介绍2017-09-29 1901

-

比特翻转现象:GLitch是第一个利用JavaScript入侵智能手机2018-05-17 9685

-

一个时钟异步切换原理图2020-11-10 2589

-

基本时钟切换术语和标准输入时钟切换配置资料下载2021-04-05 1116

-

HMC305S:Glitch Free.5 db-5位Serical Service Serical Services Services Attrator,0.4-7.0 GHz数据Sheet2021-05-17 597

-

时钟切换电路设计方案2023-03-29 2577

-

FPGA为什么有时候还需要一个时钟配置芯片提供时钟呢?2023-10-25 2630

-

如何实现分频时钟的切换2023-12-14 1636

-

什么是时钟信号?数字电路的时钟信号是怎么产生呢?2024-01-25 15806

全部0条评论

快来发表一下你的评论吧 !