低功耗技术(一)动态功耗与静态功耗

电源/新能源

3642人已加入

描述

一、动态功耗

①翻转功耗(Switching Power)

翻转功耗是由充放电电容引起的动态功耗,其推导过程很简单,但是这个最终的结果却十分重要。

- switching power 和负载电容、电压、0到1变化事件的发生次数、时钟频率有关;

- switching power和数据无关,也就是传输的数据不会影响翻转功耗,但是数据的翻转率会影响翻转功耗。

由这个公式我们很容易得到如果想减少功耗,那么方法就是:

- 降低电压;

- 降低翻转率;

- 减少负载电容;

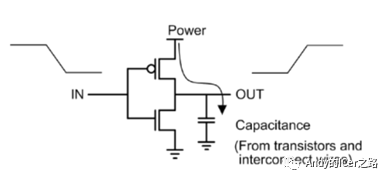

②短路功耗(Internal Power)

短路功耗又可以称为 内部功耗 ,主要原因是直接通路电流引起的功耗,即短路造成的。短路功耗是因为在输入信号进行翻转时,信号的翻转不可能瞬时完成,因此PMOS和NMOS不可能总是一个截止另外一个导通,总有那么一段时间是使PMOS和NMOS同时导通,那么从电源VDD到地VSS之间就有了通路,就形成了短路电流,如下面的反相器电路图所示:

二、静态功耗

静态功耗是由于漏电流引起的,在CMOS门中,漏电流主要来自4个源头:

- 亚阈值漏电流(Sub-threshold Leakage, ISUB): 亚阈值泄漏电流是晶体管应当截止时流过的电流。

- 栅极漏电流(Gate Leakage, Igate): 由于栅极氧化物隧穿和热载流子注入,从栅极直接通过氧化物流到衬底的电流。

- 栅极感应漏电流(Gate Induced Drain Leakage, IGIDL): 结泄漏电流发生在源或漏扩散区处在与衬底不同电位的情况下。结泄漏电流与其他泄漏电流相比时通常都很小。

- 反向偏置结泄漏(Reverse Bias Junction Leakage ,IREV):由少数载流子漂移和在耗尽区产生电子/空穴对引起。

MOS管的结构图如下:

漏电流组成如下图所示:

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

物联网系统中TCP低功耗产品长连接状态下降低功耗功能的实现方案2024-09-29 1778

-

浅析CMOS电路的静态功耗和动态功耗2024-04-01 10432

-

#硬声创作季 #STM32 手把手教你学STM32-044 待机唤醒实验-低功耗-M4-2水管工 2022-10-29

-

低功耗设计相关资料推荐2021-11-11 1672

-

低功耗设计2021-11-06 788

-

如何采用创新降耗技术应对FPGA静态和动态功耗的挑战?2021-04-30 1305

-

芯片设计中的低功耗技术介绍2020-07-07 3349

-

FPGA系统设计的静态功耗和动态功耗分析与进行仿真建模2020-01-16 10396

-

FPGA设计中常用的低功耗技术是什么?2019-08-27 1763

-

基于FPGA实现低功耗系统设计2019-07-12 1699

-

FPGA设计技巧,如何能有效降低静态功耗?2019-07-05 28473

-

基于FPGA静态和动态功耗解决方案介绍2019-05-16 9757

-

蓝牙低功耗技术2011-05-13 3624

全部0条评论

快来发表一下你的评论吧 !