掌握多片FPGA的多路复用

可编程逻辑

描述

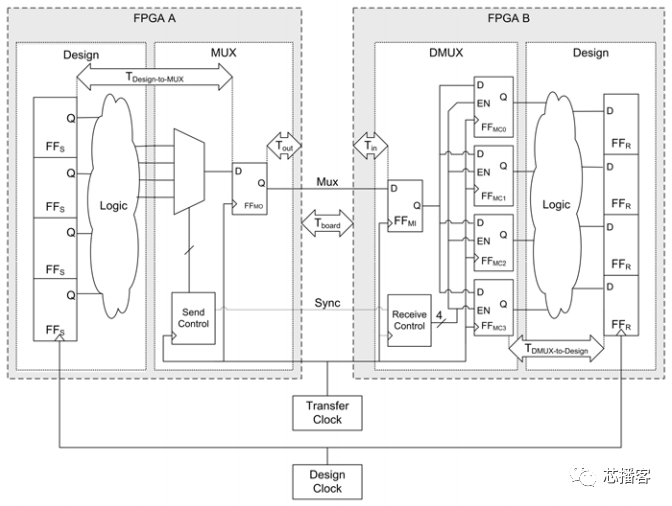

多片FPGA之间的互连,经常提到多路复用的概念,也经常提到TDM的概念,正确理解多路复用在多片FPGA原型验证系统中的机理,尤其是时序机制,对于我们正确看待和理解多片FPGA原型系统的性能有很好的促进作用。下图是一个使用多路复用器后接采样FF的多路复用解决方案的示例。

在FPGA-A中,我们有一些触发器的设计,我们称为FF(Flip_Flop),然后是一些组合逻辑设计,在FPGA中的Design这个模块,可以认为是移植成功的SoC的RTL设计,在这里抽象为一部分组合逻辑和时序逻辑FF的简单连接,实际上,我们的设计中也是组合逻辑和时序逻辑的结合,只是要比图示要复杂的多。

FPGA_A中要输出的IO的值被馈送到发送级所谓的发送级并不是SoC所拥有的RTL代码,而是为了正确传输这些IO所额外设计的文件,该级包含一个复用器,该复用器依次选择每个设计信号和一个输出FF,我们将其称为FFMO。FFMO可以被放置在FPGA A的IO FF中,以改善输出时序。

在两个FPGA之间,我们为多路复用信号使用单端连接(在图中显示为多路复用器)。为了保证信号完整性,我们必须确保在发送FFMO和接收FF(我们称之为FFMI)之间的一个传输时钟周期内接收多路复用样本并将其锁存到目的FF。

当多路复用的信号被逐个采样到FPGA-B中的FFMI时,而后它们被存储在一组捕获FF中,我们称之为FFMC。这些FF确保样本在设计时钟的下一个时钟边缘之前都是稳定的。我们的示例还显示了FPGA_B接收端的一些组合设计逻辑(被分割在FPGA-B中的SoC的逻辑)。

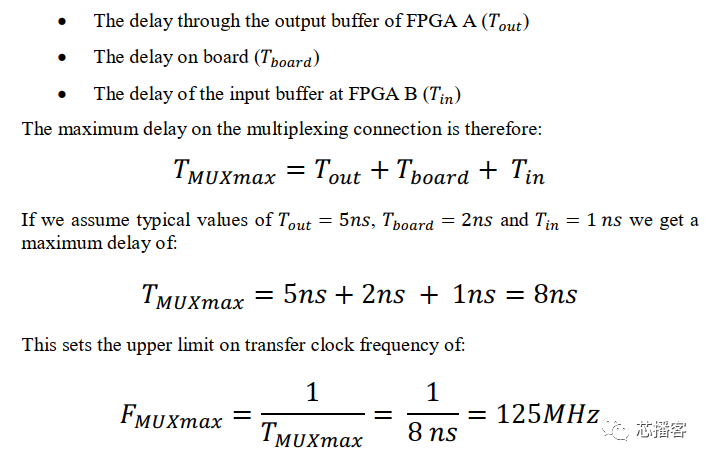

那么,如何计算最大传输频率以及传输时钟与设计时钟之间的比率呢?我们的约束是在FFMO和FFMI之间的传输时钟周期内传输数据值。路径上的延迟如下:

这是信号可以在FPGA之间传递的理论速率,但我们使用的是单端信令,并且FPGA之间可能存在一些时钟不确定性或抖动,我们也应该给容差留出一些空间。

因此,根据我们的经验,我们应该添加Ttolerances = 1到2ns的安全裕度,这取决于我们对电路板上时钟分布质量的信心。对于此示例,让我们假设

最大时钟频率100MHz(或10ns的周期)必须作为FPGA合成和放置和路由期间传输时钟的约束条件。

现在让我们更仔细地考虑多路复用器和dmux组件是如何工作的,以便计算传输时钟和设计时钟之间的比率。我们必须考虑两种可能的用例。

第一种情况是传输时钟和设计时钟是相互同步的,即,它们来自一个时钟源,并且它们是相位对准的。

第二种情况是,传输时钟和设计时钟是异步的,在这种情况下,我们不知道数据值的传输是从哪个传输时钟周期开始的,我们必须设置正确的约束以确保其正常工作。

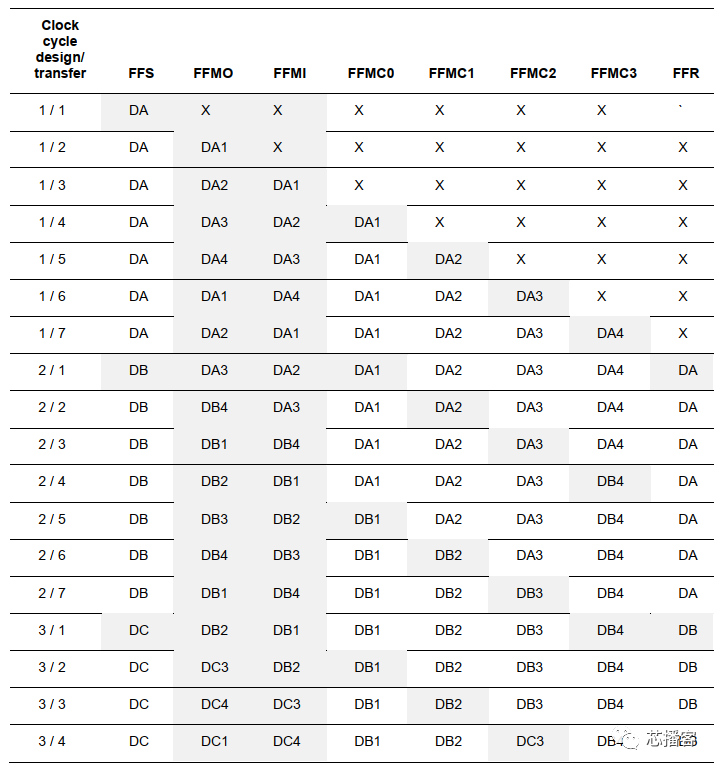

从同步情况开始,我们从框图中看到,需要一些传输时钟周期,才能将数据从发送设计FFS通过复用寄存器FFMO、FFMI、FFMC传送到接收设计寄存器FFR。

此外,即使这两个时钟是同步的,我们也必须重视发送和接收端的设计时钟和传输时钟之间的延迟。这些延迟在方框图中标记为发送侧的Tdesign−to−mux和接收侧的Tdmux−to−design。对于以下时钟比率的计算,我们假设这些延迟具有恒定值,并且我们必须将这些假设作为综合布局布线的约束条件。

对于我们这里的示例,我们将假设这些延迟最大为一个传输时钟周期,这是极端的,最大为10ns。下表显示了基于以上假设的设计信号如何通过复用传输。

考虑在设计寄存器FFS中有效的新数据DA。一个传输时钟周期后,第一位DA1被捕获到FFMO中。

这是使用我们的假设,即设计时钟和传输时钟之间的延迟是最大一个传输时钟周期,并且时钟是相位同步的。

表中带阴影的条目显示了捕获的数据位如何通过多路复用器和dmux传输,并被计时到接收FFR中。

我们在首都强调了链中每个FF都有新数据的地方。正如我们从选项卡的第一列中看到的,设计时钟和传输时钟之间的比率是7,这意味着设计时钟必须比传输时钟慢7倍才能保证正确的操作。

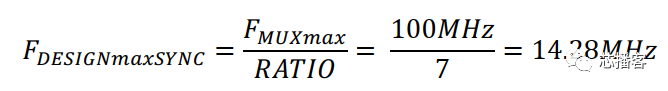

现在,计算我们的同步复用示例的最大设计时钟频率很简单:

因此,对于这一设计,即在100MHz下使用4:1复用器比率复用信号,我们可以在14.28MHz以上的最坏情况下运行我们的设计,而不是我们可能从4:1比率中猜测的25MHz。

我们现在已经看到了传输时钟和设计时钟是同步的情况,但让我们考虑异步复用方案中的差异。最大传输时钟频率相同,但我们不知道设计和传输时钟的有效边缘之间的偏差。

因此,我们必须在发送和接收端增加额外的同步时间,以确保满足设计和传输时钟之间的设置和保持时间。

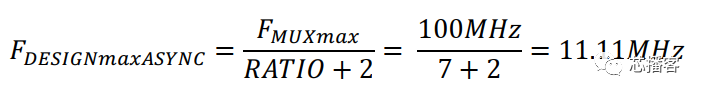

这在发送端和接收端都增加了额外的传输时钟周期。异步复用的最大设计频率计算如下:

我们可以看到,异步情况以较低的设计频率运行,但异步多路复用的优点是,我们不需要同步设计和传输时钟,而且我们可以更自由地从何处获取传输时钟。

为了总结这个例子,我们应该记住用复用来约束设计的重要事项是:

基于FPGA

IO技术、板上延迟和容差计算传输时钟的正确最大频率。

考虑同步或异步复用之间的差异,计算设计和传输时钟之间的正确比率。

为传输时钟和设计时钟提供正确的合成和FPGA位置和路线限制。

为传输时钟和设计时钟之间的延迟提供正确的合成时钟和FPGA位置和路径限制。

考虑了FPGA之间使用正常单端信令的不同类型的复用,我们可以做什么来获得更高的复用率,但仍然保持高系统速度?答案在于提高最大转移使用FPGA的内置串行IP和更强大的信令技术。

审核编辑:刘清

-

频分多路复用和时分多路复用的区别有哪些2024-05-07 6977

-

一文掌握多片FPGA的多路复用2023-06-06 2392

-

基于多片FPGA多路复用(TDM)科普2023-05-23 2854

-

如何在Mx1051的FlexCAN1中配置简单信号多路复用和扩展信号多路复用?2023-05-05 721

-

8:1 多路复用放大器形成大型多平面多路复用器结构2023-01-12 2926

-

[6.4.1]--多路复用器李开鸿 2022-11-13

-

时钟信号切换可以用多路复用开关吗2020-06-27 2650

-

多路复用ICSP引脚如何控制开关?2020-04-01 2543

-

什么是异步时分多路复用(ATDM)2010-04-03 2195

-

时分多路复用(TDM),时分多路复用(TDM)的原理是什么?2010-03-19 11396

-

复用器的多路复用2010-01-07 1435

-

多路复用技术2009-06-27 1314

-

非多路复用与多路复用总线转换桥的设计与实现2009-03-28 1253

-

多路复用与数字复接2008-10-22 911

全部0条评论

快来发表一下你的评论吧 !