射频芯片layout设计的40MHz晶振布局走线规范

RF/无线

描述

40MHz晶振布局走线规范

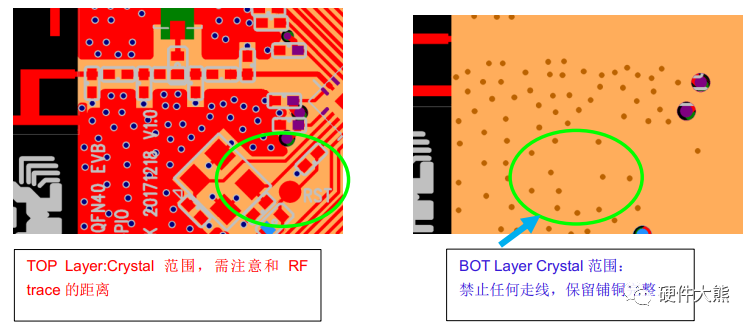

在没有结构限制情况下, Crystal 和 BT CHIP 要放在同一层面。

为了避免干扰 RF 信号, Crystal 尽量远离 RF Trace。

Crystal 的放置应尽可能靠近 BT CHIP,路径要短, Trace 宽度建议超过 6mil。

如果是 2 层板,禁止在 Crystal 的背层走线,让背层(BOT)的铺铜保留完整性。

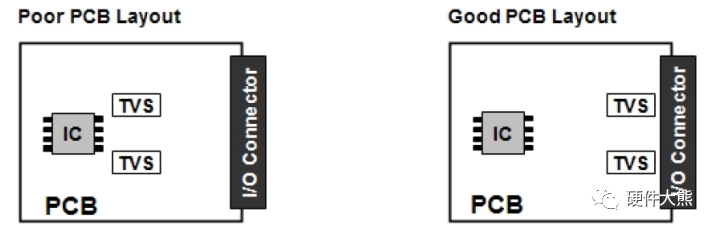

ESD Layout

TVS 摆放位置应尽可能靠近 ESD 源头(接头等处),与被保护 IC 的距离要远于 ESD 源。布线时需将 ESD 源直接接到 TVS,减少 TVS 管和回流地之间的寄生电感

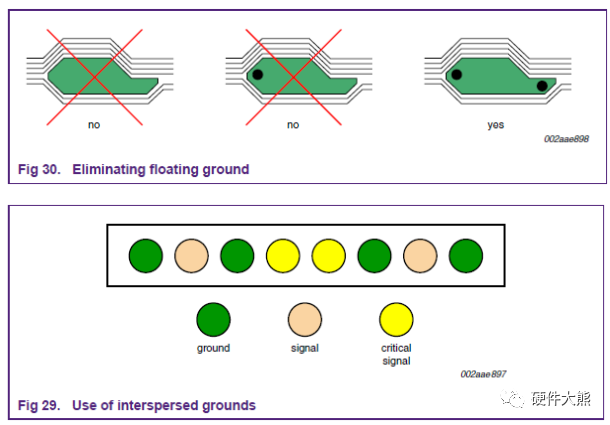

分割地平面时要注意缩短信号线的回流路径, 采用星状线的方式实现并联接地。

删除孤岛铜皮,用地将敏感信号包裹起来,防止其他信号的辐射干扰

尽量缩短线长以减少寄生电感。因直角走线会产生更大的电磁辐射,避免直角走线连接到器件或走线上。高速电路设计时,更需注意这点。

尽量增大过孔的钻孔直径和焊盘直径,减少过孔的寄生电感。

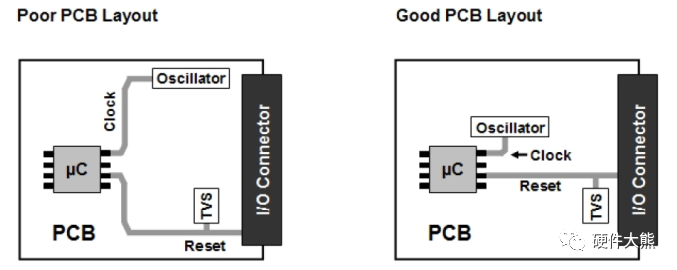

布线时,让敏感信号线远离 PCB 板边。为避免走线与天线间的串扰,走线需远离天线,天线需放在离

接头较远的位置。布局时,将所有的接头和板边接线放在 PCB 板边一侧, ESD 敏感器件放到 PCB 中心。

两层板注意事项

BT CHIP、 RF、 Crystal、 Buck 区域,尽量避免于这些区域走线。

两层板走线尽可能走在同一层面。

若走线要贯穿到背层,背面的走线尽可能短或者集中在一起,维持背面敷铜的完整。

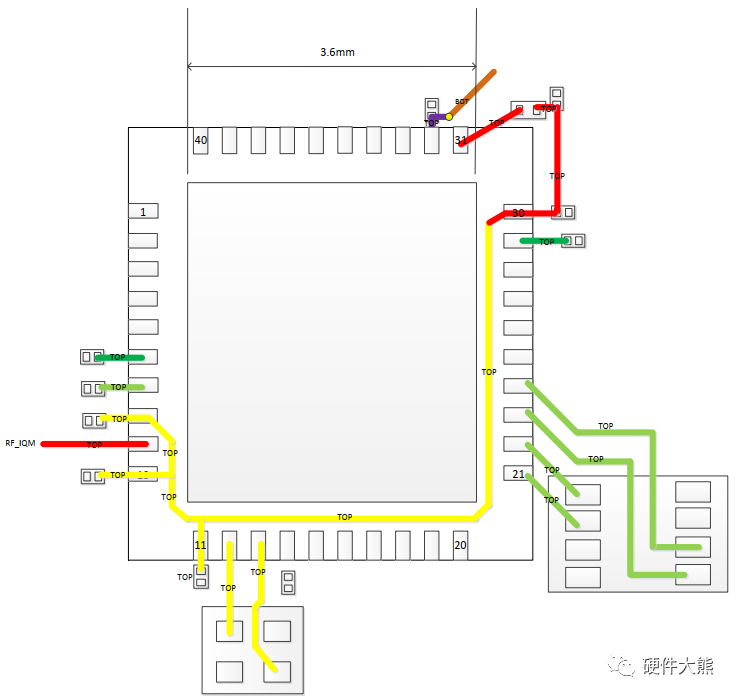

电源VDD12 走线可将 EPAD 尺寸改小到 3.6mm, trace 从 IC package 缝隙中穿过。

其他注意事项

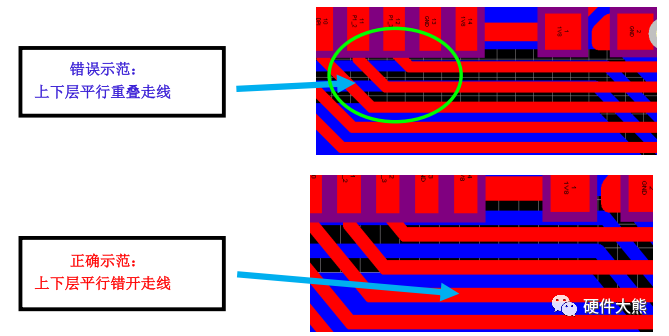

上下层走线时尽可能不要平行重叠的走线

External flash 必须尽量的靠近 IC 摆放

审核编辑:刘清

-

清lio

2024-12-06

0 回复 举报RF信号线没有做阻抗匹配 收起回复

清lio

2024-12-06

0 回复 举报RF信号线没有做阻抗匹配 收起回复

-

40MHz:藏在晶振里的数字密码2026-04-10 297

-

爱普生FA-20H 40MHz晶振成为智能穿戴设备时钟的最佳之选2024-08-12 1018

-

ESP32-D2DW 40MHZ晶振不能起振的原因?2024-07-01 1049

-

射频PCB走线规则简析2024-05-16 6643

-

一款射频芯片的layout设计指导案例2023-06-06 2199

-

ESP32-S3-WROOM-1(N8R8)是否需要连接外围40MHz晶振?2023-03-13 724

-

有源贴片晶振OSC3225 40MHZ技术数据手册2022-07-23 538

-

有源贴片晶振OSC3225 40MHZ 规格书2022-07-07 469

-

关于晶振频偏过大芯片工作正常,频率正常反而不工作的问题2019-11-22 8835

-

请问自带晶振的ad芯片与fpga通信的时钟设计该注意些什么?2019-05-08 1449

-

请问AD9361的板载晶振为什么不用30.72MHz、15.36MHz这样的晶振?2018-07-31 4380

-

我用atf1508as,100mhz晶振2013-04-04 2445

-

40MHz AM接收机的高放电路2009-03-13 2493

全部0条评论

快来发表一下你的评论吧 !