I2C模块的用法干货分享

接口/总线/驱动

描述

I2C总线是一种双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送信息。

主器件通过串行数据(SDA)线和串行时钟 (SCL)线连接到其他从器件,每个器件都有一个唯一的地址识别(无论是微控制器、LCD 驱动器、存储器或键盘接口),除了LCD 驱动器(只能作为接收器)其他器件都可以作为数据的发送器和接收器。

I2C模块主要包含

一个串行接口:一个数据引脚(SDA)和一个时钟引脚(SCL)

数据寄存器和FIF0:暂时保存SDA引脚与CPU之间传递的接收数据和发送数据

控制和状态寄存器。

外围总线接口:用于CPU访问I2C模块寄存器和FIF0s。

时钟同步器:用来使I2C输入时钟(由DSP时钟源产生)和SCL引脚的时钟同步,并且使数据发送器与不同的主机时钟速度同步

对输入到I2C模块的时钟进行分频的预定标器。

SDA和SCL引脚上的噪声滤波。

用来处理I2C模块和其它主器件的裁决问题的裁决器。

中断产生逻辑,用以向CPU发送中断信号。

FIF0中断产生逻辑:以便在I2C模块中接受数据或发送数据时能够同步访问FIF0。

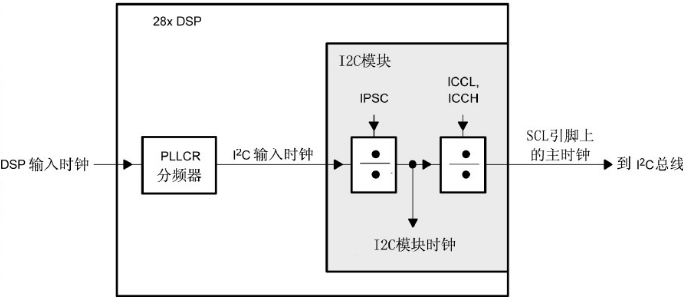

时钟产生源:

当外部时钟源发射信号时DSP接受到这个信号后产生一个频率可编程的I2C输入时钟。

I2C输入时钟为CPU时钟,在I2C内部被两倍以上分频后产生I2C模块时钟和主机时钟。

模块时钟决定I2C以何种频率工作。I2C模块的可编程分频器通过对输入时钟来产生模块的时钟。为了与所有I2C协议时钟频率匹配,模块时钟必须配置在7-12MHz之间。分频器必须在I2C模块被复位时进行配置。当IRS从0变成1时所分频的频率才能有效。IRS=1时改变IPSC的值不起作用。

I2C模块操作

1.数据状态:只有当SCL是低电平时,数据线SDA自身的高低电平状态才能改变。

2.输入和输出电平:主设备为每个数据传输产生一个时钟脉冲。因为连接到I2C总线的设备采用的技术标准不同,所以逻辑0(低电平)和逻辑1(高电平)是不固定的,与设备的VDD值有关。

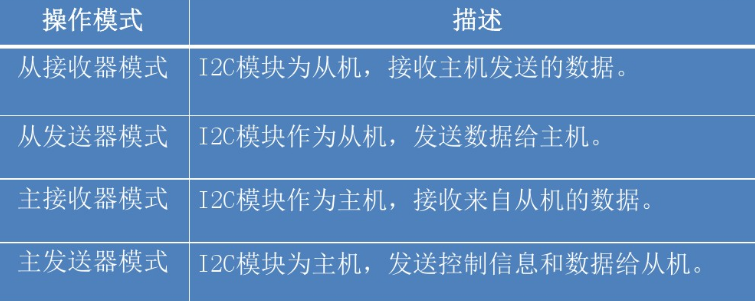

3.操作模式:如果主机要发送数据给从器件,则主机首先寻址从器件,然后主动发送数据至从器件,最后由主机终止数据传送;如果主机要接收从器件的数据,首先由主器件寻址从器件.然后主机接收从器件发送的数据,最后由主机终止接收过程。

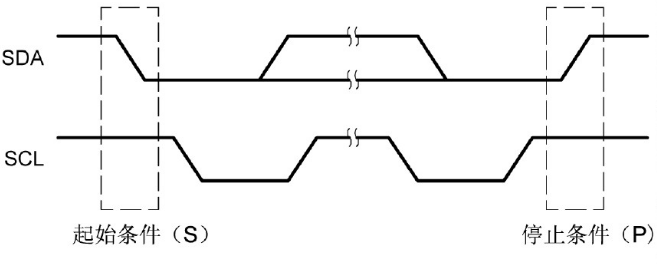

4.I2C模块的起始和停止条件:当I2C模块作为主机时,就由这个模块来控制起始和停止。

当SCL为高电平,SDA数据线产生由高到低的跳变时,表示起始条件产生。主机通过产生这样这样的条件来表明数据传送开始

当SCL为高电平,SDA数据线产生由低到高的跳变时,表示停止条件产生。主机通过产生该条件表明数据传送停止结束。

5.串行数据格式:I2C模块可以传输1-8位的数据。SDA数据线上每一位的维持时间相当于SCL的一个脉冲。传输数据时,都是高有效位字节开始传送。发送和接受数据的个数没有限制。

每个数据传输结束后,主机可以再次驱动一个起始信号。有了这个功能,主机就可以和多个从机通信,不需要通过驱动停止信号来放弃总线控制权。

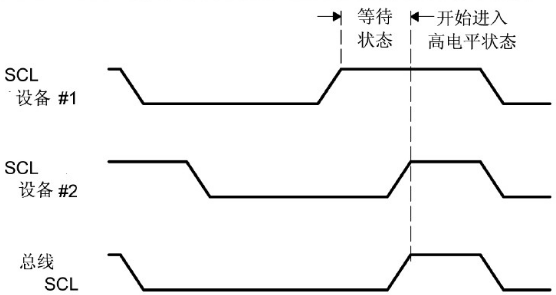

6.时钟同步。SCL的“线与”特性指的是在SCL上首先产生低电平的设备会控制其它的设备。这个由高到低的跳变,强制其它设备的时钟发生器开始其低电平周期。并且只要有设备的时钟信号为低则SCCL一直保持为低电平。必须等到SCL被释放后其它设备才能结束它们的低电平周期,开始其高电平周期。

SCL上产生的同步信号中,低电平周期的长度由最慢的设备决定,高电平周期的长度则是由最快的设备决定。

-

基于FPGA的I2C控制模块设计2025-12-26 6101

-

Micropython TPYBoard I2C的用法2018-05-25 5974

-

i2c总线ppt(I2C总线器件应用)2008-08-13 1363

-

I2C总线规范与I2C器件C51读写程序2009-08-22 1104

-

I2C总线接口模块设计2009-11-02 799

-

HT66F40使用SIM I2C Mode之用法与注意事项2010-03-27 936

-

I2C Guid I2C指南2010-04-23 812

-

什么是i2c总线2007-11-05 4145

-

i2c2016-05-17 1064

-

I2C模块arduinoio Simulink软件包2018-01-22 916

-

Arduino教程之I2C模块使用教程资料免费下载2019-01-22 1665

-

干货:I2C总线最全教程讲解2021-02-20 14722

-

I2C基本用法及问题汇总资料下载2021-04-23 1001

-

硬件I2C与模拟I2C2021-12-28 3378

-

使用C2000 I2C模块连接EEPROM2024-08-27 621

全部0条评论

快来发表一下你的评论吧 !