什么是SerDes?SerDes的应用场景又是什么呢?

描述

01

SerDes简介

首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?做过FPGA的小伙伴想必都知道串口,与并行传输技术相比,串行传输技术的引脚数量少、扩展能力强、采 用点对点的连接方式,而且能提供比并行传输更高带宽,而SerDes的主要作用就是把并行数据转化成为串行数据,或者将串行数据转化为并行数据的“器件。

SerDes的全称是SERializer(串行 器)/DESerializer(解串器),这种主流的高速的时分多路复用(TDM),点对点的串行通信技术可以充分利用通信的信道容量,提升通信速度,进而大量的降低通信成本。

目前,商用基于SerDes架构的通信协议最高可实现单通道56Gbps(好像已经可达112Gbps)的速率,在未来高带宽、低成本的应用领域会 越来越广泛。

实际上PCIE,JESD204B等复杂协议都是基于SerDes协议,常见的电SerDes就PCIE等协议来说,更接近物理层,所以SerDes通常又被称之为物理层(PHY)器件。正是因为SerDes的强电气属性,使得 Serdes具有以下优点:

1.减少布线冲突(非独立时钟嵌入在数据流中,解决了限制数据传输速率的Signal时钟的Jilter问 题);带宽高 ;

2.引脚数目少 ;

3.抗噪声、抗干扰能力强(差分传输);

4.降低开关噪声;

5.扩展能力强;

6.更低的功耗和封装成本;

根据SerDes的结构的不同可以将其分为四类:

并行时钟SerDes:将并行宽总线串行化为多个差分信号对,传送与数据并联的时钟。这些SerDes 比较便宜,在需要同时使用多个SerDes 的应用中,可以通过电缆或背板有效地扩展宽总线;

8B/10B编码SerDes(最常见的结构):将每个数据字节映射到10bit代码,然后将其串行化为单一 信号对。10位代码是这样定义的:为接收器钟恢复提供足够的转换,并且保证直流平衡(即发送相 等数量的‘1’和‘0’)。这些属性使8B/10B编码SerDes 能够在有损耗的互连和光纤传输中以较少的信 号失真高速运行;

嵌入式时钟SerDes:将数据总线和时钟串化为一个串行信号对。两个时钟位,一高一低,在每个 时钟循环中内嵌串行数据流,对每个串行化字的开始和结束成帧,并且在串行流中建立定期的上升 边沿。由于有效负载夹在嵌入式时钟位之间,因此数据有效负载字宽度并不限定于字节的倍数;

位交错SerDes:将多个输入串行流中的位汇聚为更快的串行信号对。

SerDes支持非常多的的主流工业标准,比如Serial RapidIO ,FiberChannel(FC),PCI-Express (PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。

02

SerDes结构

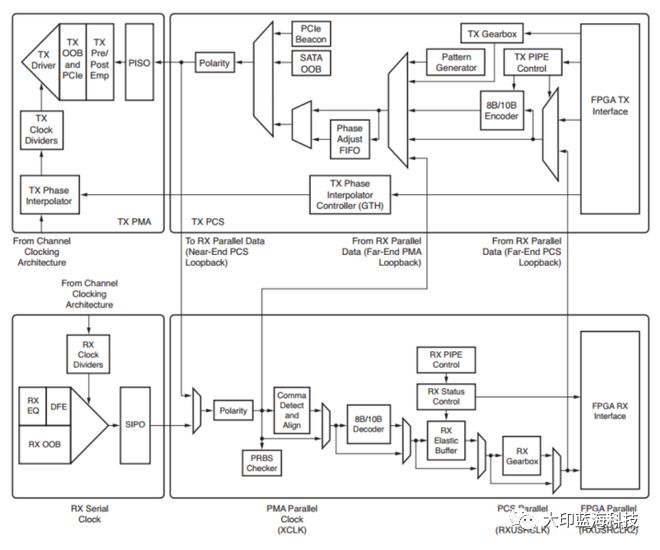

实上在SerDes收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠 正和通道绑定电路,为各种高速串行数据传输协议提供了物理层(PHY)基础。

而主流的8B/10B编 码SerDes则主要由物理介质相关子层( PMD)、物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层( Physical Coding Sublayer,PCS )所组成,且收发器的 TX发送端和RX接收端功能独立。

SerDes收发器内部的电路物理层结构图

各物理层的作用:

1.PCS层,负责数据流的编码/解码,是标准的可综合CMOS数字逻辑,可以通过逻辑综合实现 软硬综合实现。

2.PMA层,是数模混合CML/CMOS电路,负责负责串化/解串化,是理解SerDes区别于并行接 口的关键。

3.PMD层,负责串行信号通信。

涉及模块:

1.TXPLL:这个模块主要使用具有1ps以下的抖动的时钟为参考,输出数GHZ级的时钟。

2.RXCDR(时钟恢复):这个模块是一个复杂的控制回路,作用是来追踪传入数据的平均相位, 并不管Path上的任何SI或失真,通常是通过复杂的相位旋转器或CDR驱动的锁相环来完成的。

3.TXdriver:这个模块把序列化模块转化为差分信号。

4.RX均衡器:此模块用连续的时间均衡器以及DFE(裁决反馈均衡器)来均衡高速效应,通常 需要一个自动增益的电路来促进均衡效果,RX均衡器通常以状态机逻辑和软件的形式来实现 自动校准。

转化过程:

1.发送(TX)即并转串 简单的来说就是并行信号通过FiFO,传递给内部的8b/10b编码器、扰码器,防止数据连0/1, 之后传递给串行器进行转化,经过均衡器均衡后,由驱动发出。

2.接收(RX)即串转并 简单的来说就是输入的串行信号经过线性均衡器均衡后,去除了高速时钟的jilter后,CDR从数 据中恢复Caputure时钟,并通过解串器转为对齐的并行信号,由驱动发出。

03

光SerDes解串器

目前光互连中电串行/反串行器(SerDes)的高功耗和速度提升障碍是光互连发展的阻碍,人们逐 渐把目光投向光SerDes的高速收发器。

光SerDes解串器采用时间交错的多路复用技术来进行并行 串行光信号的直接转换,同时电SerDes的缺失极大地降低了数据传输通道中的功耗,以一个工作在 20个数据速率为2GHz的并行数字路径和1个40GHz串行光通道之间的光SerDes收发器为例,其功 耗仅为13.5pJ/b左右,要远远低于同类型电SerDes的静态功耗。

同时结合波分复用(WDM)、脉冲幅 度调制(PAM)、正交相移键控(QPSM)等多种光复用技术,可进一步提高带宽。

在数据中心、超级计算机和光纤接入网的数据通信中,对未来带宽的需求不断增长,这促使传 统的电子链路被光链路取代,用于片内和片外通信。

虽然光学技术在带宽、损耗、串扰、电磁兼容 等方面具有优势,但由于光信号不能直接由处理器处理,需要将光信号转换为电信号。

传统的光互 连通信解决方案是将并行电信号通过芯片内部的串行器/反串行器(SerDes)转换为高速串行电信号, 再通过芯片外部的光收发器转换为光信号。

由于SerDes电路的高功耗和链路比特率,光互连的发展 逐渐面临瓶颈。

收发器的大部分功率消耗在模拟电路,特别是SerDes上,而不是光学器件上。

以当前28Gb/s系统为例,收发器的光电转换(EO)和光电转换(OE)功耗仅为7.2pJ/b。但是整个 链路的功率预算增长到29.5pJ/b,其中22.3pJ/b(75.6%)是由SerDes电路贡献的,这与OE-EO转换 没有直接关系。

进一步的带宽扩展受到严重限制,因为需要均衡来恢复信号完整性,并在高速串行 链路的末端重新计时,即使是非常短的几英寸距离。同时提高比特率和保持低功耗是不可持续的。

因此,最好是提高并行度来提高链路比特率。但是并行化程度的提高是由芯片的引脚数决定的,而 引脚数是由制造工艺、芯片尺寸、芯片顶层设计等决定的。

简单地说,光SerDes就是利用时分复用技术将并行电信号加载到光载波上,获得单波长单通道 电平可能高于40Gb/s的串行光传输,同时完成光电和串并联转换。

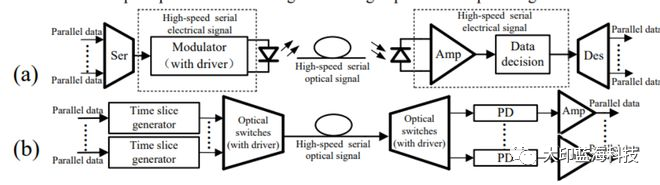

如图3所示,传统的电子SerDes 收发器需要两级转换,以高速串行电信号为介质,将低速并行电信号转换为高速串行光信号,而光 SerDes收发器实现了低速并行电信号与高速串行光信号的直接转换,即比传统的电SerDes多了一 级光电信号转化。

两种收发器的比较。(a)在传统收发器中,以高速串行电信号为介质,利用电子SerDes将并行 电信号转换为高速串行光信号。(b)在所提出的收发器中,利用光SerDes将并行电信号直接转换为 高速串行光信号。

04

SerDes主要包括以下几个部分:

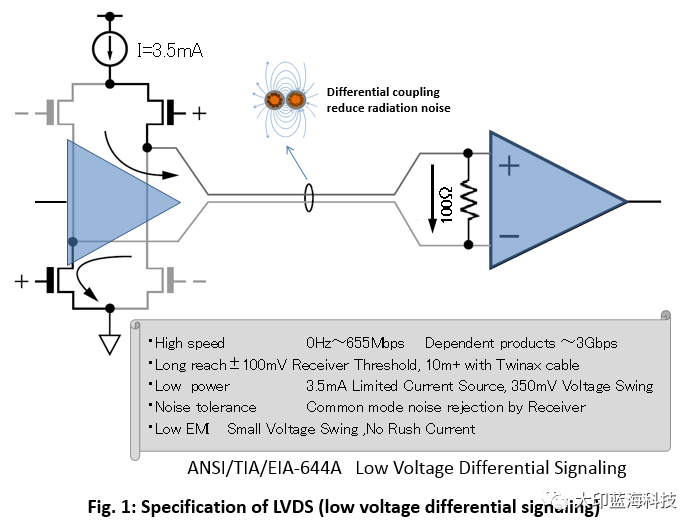

1、SerDes的前辈:LVDS SerDes,其中LVDS应该是大家比较熟悉的,这里不会展开,主要就是LVDS是1995年作为「ANSI/TIA/EIA-644」制定了标准规格的串行接口用物理层规格,为很多串行差分总线的发展奠定了基础。

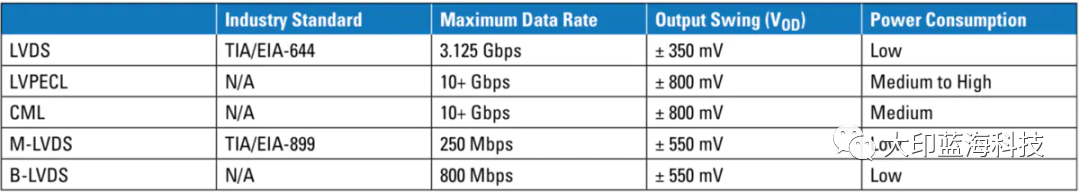

2、SerDes底层硬件包括早期的LVDS和现在CML:SerDes信号层采用的LVDS工作在155Mbps~1.25Gbps之间,而CML(电流模式信号)在600Mbps和10+ Gbps。

因此现在SerDes一般使用CML。但是LVDS和CML信号可以互通,但要有外接电阻做电平转换。

LVDS SerDes的基本原理理解串行总线高速、远距离、低杂音的特征。

针对LVDS、CML等差分技术会详细的介绍;上面已经详细介绍了LVDS,在阅读文档时,还时常看到CML、LVPECL,那么这些差分信号之间的差别是什么?

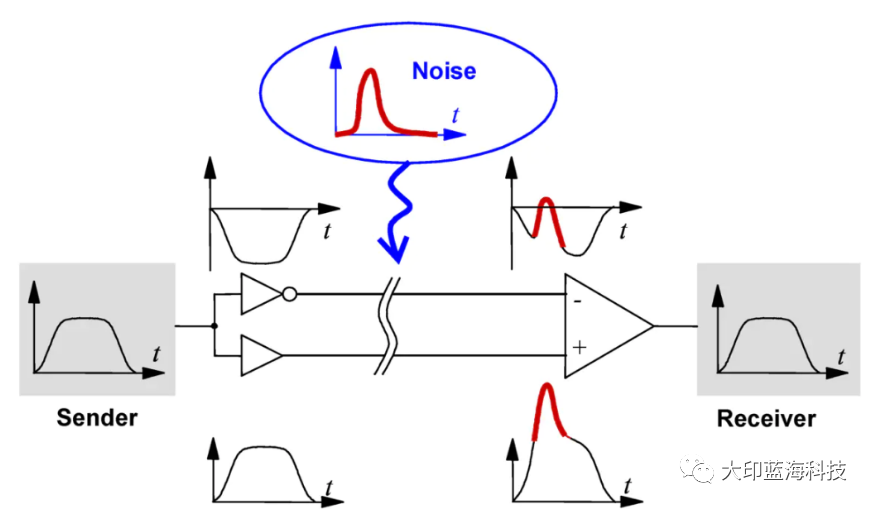

差分技术:LVDS、MLVDS、CML、LVPECL的区别与应用场景平衡型差分传输Differential Transmission 是一种信号传输的技术,区别于传统的一根信号线一根地线的非平衡型单端Single End Transmission 做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。在这两根线上的传输的信号就是差分信号。

信号接收端比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

差分信号示意图

差分信号与传统的一根信号线一根地线(即单端信号)走线的做法相比,其优缺点分别是。

优点:

1.抗干扰能力强。干扰噪声一般会等值、同时的被加载到两根信号线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

2.能有效抑制电磁干扰(EMI)。由于两根线靠得很近且信号幅值相等,这两根线与地线之间的耦合电磁场的幅值也相等,同时他们的信号极性相反,按右手螺旋定则,那他们的磁力线是互相抵消的。两根线耦合的越紧密,互相抵消的磁力线就越多。泄放到外界的电磁能量越少。

3.时序定位准确。差分信号的接收端是两根线上的信号幅值之差发生正负跳变的点,作为判断逻辑0/1跳变的点的。而普通单端信号以阈值电压作为信号逻辑0/1的跳变点,受阈值电压与信号幅值电压之比的影响较大,不适合低幅度的信号。

4.发送端电流源始终导通,消除开关噪声带来的尖峰(单端技术中所需要)和大电流晶体管不断导通-关断造成的电磁干扰EMI。

缺点:

若电路板的面积非常吃紧,单端信号可以只有一根信号线,地线走地平面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。这样的情况常常发生在芯片的管脚间距很小,以至于只能穿过一根走线的情况下。

05

几种典型差分信号

为了实现高速数据传输,有多种差分技术可供选择。这些差分技术都有差分信号几个共同的优点,但是在性能、功耗和应用场景上有很大的区别。下图列举了最常用的几种差分信号技术和它们的主要参数。

各种差分技术的工业标准

LVDS信号摆幅低,为350mv,对应功耗很低,速率达到3.125Gbps。总的来说,终接方法简单、功耗和噪声低等优点,使得LVDS成为几十Mbps至3Gbps、甚至更高的应用之首选。

我们可以毫不夸张地说--LVDS(Low voltage differential signaling)技术开拓了串行接口的历史。

在1990年代中期,LVDS SerDes(串行转换器/串行解串器)被使用于市场需求急速扩大的笔记本电脑上,销售数量急剧猛增。

LVDS为笔记本电脑在世界上的普及起到了一定的作用,为液晶显示器在市场上站稳脚跟做出了很大的贡献。

使用于笔记本电脑的LVDS SerDes在那之后,被集中用于电脑用芯片组和液晶时间控制器IC(TCON),以应对UXGA和WUXGA之类高分辨率液晶屏所需,被持续使用了15年以上。

笔记本应用上从2012年左右开始慢慢被eDP(embedded DisplayPort)替换。但可以说LVDS SerDes直到近期仍是支撑着笔记本电脑市场的存在。

但LVDS SerDes并不是连接液晶显示屏和逻辑板的“专用”接口技术。分析一下这一技术的内容就会一目了然--它是一种连接A点与B点的普通的串行接口技术。

因此,他可以在各种不同的接口用途上适用。那么在哪些用途上如何使用才能更好地发挥出LVDS SerDes的性能呢?下面我们就来详细说明。

06

发挥高速的数据传输的作用

要灵活使用LVDS SerDes,首先需要理解物理层面的LVDS技术。

LVDS是1995年作为「ANSI/TIA/EIA-644」制定了标准规格的串行接口用物理层规格(图1)。通过驱动3.5mA的稳定电流电源,可在100Ω終端时,以350mV这样非常低振幅的差动信号来高速传送数据。

其数据传输速度在规格内限定最大为655Mbit/秒。但这并不是极限值。通过各半导体厂商独有的加工,可以完成3Gbit/秒左右的高速传输速度。

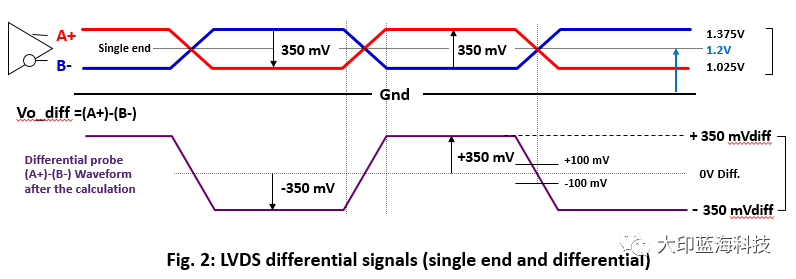

LVDS的差动信号波形的具体示例请见图2。

将2根差动信号--正电极信号(A+)和负电极信号(B−),以1.2V的共同电压(Voc)为中心,使2个信号间以350mV的电位差摆动。

然后,用探针测定示波器的差动,会得到图2这样的信号波形。

这就是两个信号的振幅差((A+)−(B−))。以差动探针测定,就能得到振幅差的计算结果。但是这样的信号波形并不是物理存在的。

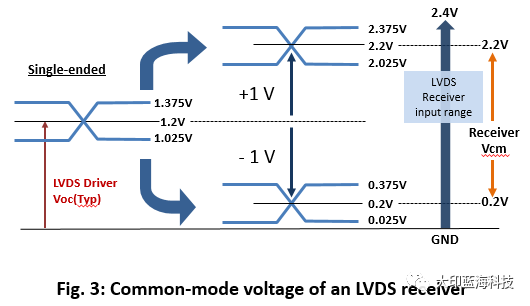

图3是LVDS接收器的共通电压范围。

如图所示:LVDS接收器其可收信的共通电压范围很广。送信(发送机)方以1.2V的共通电压输出后,收信(接收器)方的共通电压只要在0.2~2.2V的范围内就能接收信号。

此外,LVDS SerDes是以低振幅的差动信号来传送数据,因此可以抑制多余的辐射杂音(EMI:Electro-Magnetic Interference);防止EMI混入其他的回路中造成不良影响之类的事态发生。

这也是它多被使用在对杂音较敏感的电子设备上的理由之一。

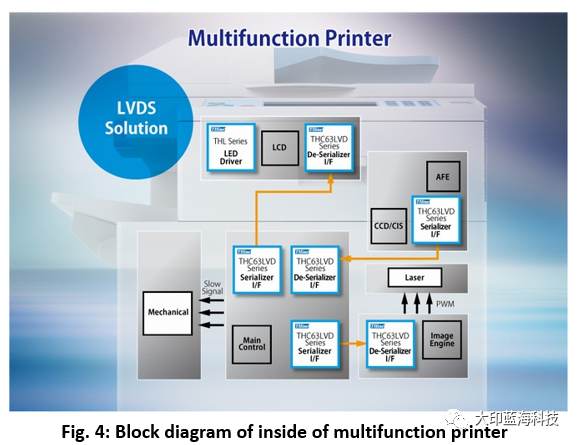

也就是说LVDS SerDes具备能高速和远距离地传输数据、对共通电压耐性高,且多余辐射少等优点。它最合适的用途就是用于需要这些优点的电子设备上。比如复合机(MFP)。

LVDS SerDes在MFP中除了可以用于液晶显示用接口以外;将扫描仪(图像传感器)取得的图像数据传送到实行图像处理的主板上时也可使用。装置内其实有一定的距离(图4)。

使用LVDS SerDes的话,扫描仪与主板相距较远也没问题。虽然与所使用的配线的扭曲度和电力损失程度有一点关系,但仅用细小的配线传输数米之类的完全不会成问题。

对于这类需要机箱内高速数据传输的电子设备,LVDS SerDes可以被很好地应用。

07

对配线扭曲和共通电压耐性强

现在,LVDS SerDes有多种产品在销售中。接下来将以THine Electronics的产品系列为例进行详细介绍。

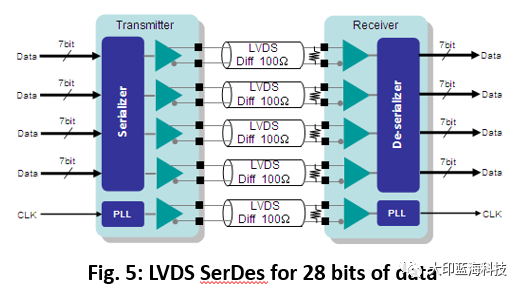

图5是LVDS SerDes的基本构成。

输入串行转换器的信号数据为7bit×4根=28bit。将这些数据转换成串行的LVDS信号,传输到串行解串器上。同时另行传送时钟信号。

串行解串器会通过传送到的时钟信号调整时间来接收信号,将7bit×4根的LVDS信号转换成TTL/CMOS数据并输出。

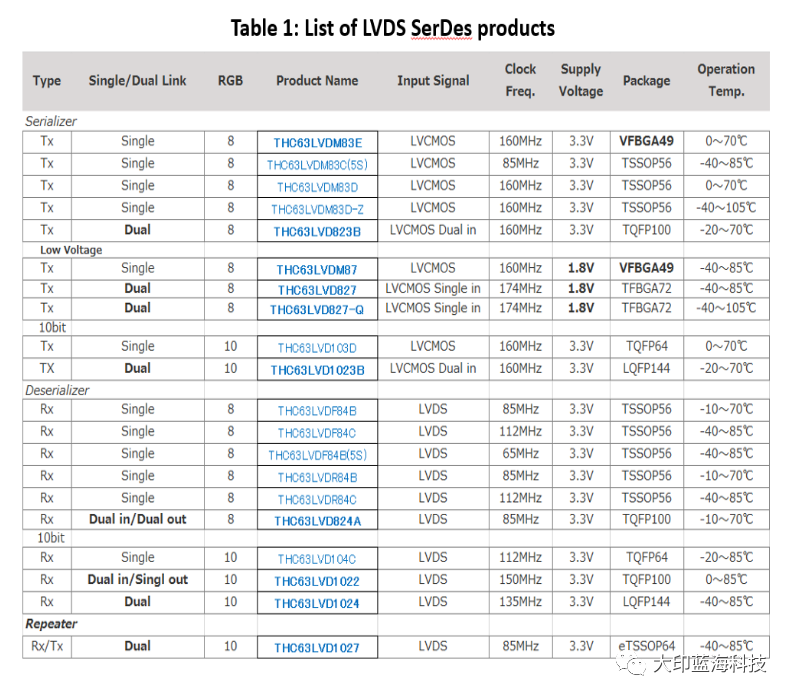

THine Electronics提供的LVDS SerDes的特征可列举为以下6点(表1)。

1、在工作电压为3.3V的普通产品以外,可在串行转换器上按照LVDS规格的同时提供1.8V的低工作电压的产品。一般情况下电源电压降低,LVDS规格中限定的1.2V的输出共通电压(Voc)就很难保持。在一些同行业的竞争对手生产的低电压产品中,Voc就常常会低于1.2V。但THine Electronics的「THC63LVDM87」和「THC63LVD827」可在达到1.8V的低工作电压环境时,输出共通电压(Voc)在到达收信侧的串行解串器时仍能维持最合适的1.2V。

2、产品涵盖可应对单连接和双连接的各个系列。比如RGB各10bit的图像信号传送用单连接的串行转换器「THC63LVD103D」和串行解串器「THC63LVD104C」,其双连接版则为串行转换器「THC63LVD1023B」和串行解串器「THC63LVD1024」。使用双连接产品可以简单地使数据传送带宽放大。比如单连接产品最多只能对应1080I;但使用双连接产品可以对应1080P。此外,我们还有RGB各8bit的双连接产品,具体产品有串行转换器「THC63LVD823B」和串行解串器「THC63LVD824A」等。这些产品可以应用于基板间及机箱内通路宽度较宽的数据通信用途上。

3、我们还有可以选择使用脉冲上升沿或脉冲下降沿来控制取得数据的时间的产品。在液晶屏等用途上会用脉冲下降沿;但一般的数据传输时所使用的串行接口则会使用脉冲上升沿。我们的产品中产品型号上如LVDR这样带「R」的产品是对应使用脉冲上升沿的;LVDF这样带「F」的产品则是对应使用脉冲下降沿。「LVDM」和「LVD」的产品则可以同时对应两种方式;可以通过pin设定来决定使用哪一种。

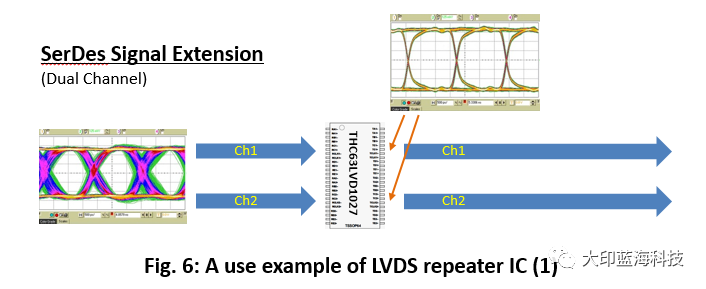

4、我们还有RepeaterIC产品。型号是「THC63LVD1027」。使用RepeaterIC,可以在接收LVDS SerDes输出的信号后,吸收通过配线时产生的扭曲及波动,调整成电压轴和时间轴都在理想状态下的LVDS信号后再一次传输(图6)。

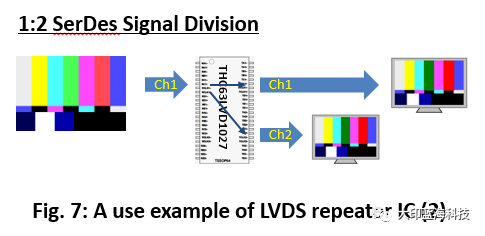

这样就可以使数据的传输距离(配线长度)大幅度加长。将其设置在传送路径的中部可使传送距离(配线长度)延伸2倍。此外,还能使至今仍很困难的1个频的图像信号输入分配到2频这样一种LVDS SerDes的信号分配成为可能(图7)。

5、可对应的时钟频率范围在8M~160MHz这一较大范围。比如「THC63LVD103D」等产品就能对应较大的时钟频率范围。频率范围大就能适用于各种并串通路;也能提高设计的灵活性。

6、我们还有将LVDS的输出控制在更低振幅的产品。如前所述:LVDS SerDes一般在3.5mA的电流电源与100Ω的終端阻力下使用。因此振幅也在350mV。使用LVDS低振幅型的RS(Reduce Swing),可使振幅降低到200mV。因此可以抑制EMI达到低耗电。

此外,我们还有适合搭载在摄像机模组等小型电子设备上的、实际面积为5mm×5mm及超小的49pin VFBGA封印产品;适用车载设备的则有工作温度范围在−40~+105℃这样广的范围下的产品;这些都是我们的特点。

综上所述,THine Electronics有着众多LVDS SerDes产品,可以对应各种不同用途。但是,仅靠LVDS SerDes还不能满足所有的串行接口需求。要对应要求有4K的倍速和鲜艳的色彩、8K这样的高分辨率信号以及高速的远距离传输的用途就比较困难。因此THine Electronics开发出了更高速的串行接口技术。

08

关于HDMI 采用的TMDS过渡调制差分信号

过渡调制差分信号,也被称为最小化传输差分信号(TMDS:Transition Minimized Differential signal),是指通过异或及异或非等逻辑算法将原始信号数据转换成10位,前8位数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡(DC-balanced,就是指在编码过程中保证信道中直流偏移为零,电平转化实现不同逻辑接口间的匹配),转换后的数据以差分传动方式传送。

过渡调制差分信号,也被称为最小化传输差分信号,是指通过异或及异或非等逻辑算法将原始信号数据转换成10位,前8位数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡(DC-balanced,就是指在编码过程中保证信道中直流偏移为零,电平转化实现不同逻辑接口间的匹配),转换后的数据以差分传动方式传送。这种算法使得被传输信号过渡过程的上冲和下冲减小,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的速度和可靠性

在上世纪九十年代晚期,Silicon Image公司开始采用面板连接、数字可视接口(DVI)和高清多媒体接口(HDMI)的形式向显示行业推广其所有权标准——最小化传输差分信号(TMDS:Transition Minimized Differential signal)。在该情况下,发射端混合了具有在铜导线上降低EMI特性的更高级编码算法,从而使得接收端具有健壮的时钟恢复性能。

8位/10位编码是一个二阶处理,它是将一个8位的输入信号转换成10位的编码。和LVDS相似的是,它采用了差分信号来降低EMI及提高精确的信号传输速率。还和LVDS相似的是,它是一个串行的传输设计。

应用: DVI技术已成功的应用于PC领域,HDMI技术也成功的推向了消费电子市场。但是,TMDS并没有因此成为广泛使用的面板接口标准。相反,没有专利费的LVDS已被普遍使用。此外,当前的DVI版本并不能更新,而且具有物理上、功能上及成本上的局限。

目前HDMI高清线普遍采用的就是TMDS算法,HDMI把视频信号分为R、G、B、H、V五种信号用TMDS技术编码。TMDS把这三个通道传输R、G、B三原色,HV编码在B信号通道里面传输,R、G的多余位置用来传输音频信号。

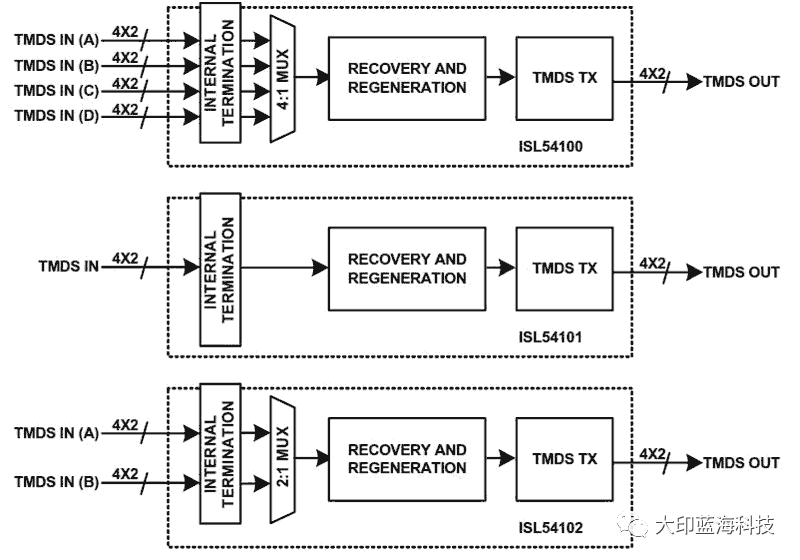

HDMI 4:1 Mux & Repeater - ISL54100 (with CDR Regeneration)

审核编辑:刘清

-

GMII、SGMII和SerDes的差异总结2020-10-09 34850

-

SERDES的作用 SerDes基础知识详解2024-01-04 9485

-

请问6678中的srio的serdes和以太网的serdes是共用还是各自有自己的serdes?2018-08-02 3430

-

主serdes和奴隶serdes,如果我使用主人,奴隶能使用吗2020-06-08 1405

-

什么是SerDes?2021-06-24 1627

-

SerDes是怎么工作的2021-07-28 2172

-

怎样去更好地使用SerDes2021-09-22 2095

-

怎样去设计SerDes2021-10-18 2159

-

参考时钟对SERDES性能的影响2017-02-10 6756

-

SERDES的优势 SERDES演变的看法2021-07-23 5596

-

SerDes收发器内部的电路物理层结构设计分析2023-04-26 3210

-

SerDes是怎么设计的?(一)2023-10-16 3524

-

为什么我们需要SERDES?SERDES的优点有哪些?2023-10-23 3820

-

什么是SerDes呢?为什么我们需要此项技术呢?有哪些设计要求和技巧?2023-11-07 4169

-

什么是SerDes?SerDes有哪些应用?2025-03-27 7585

全部0条评论

快来发表一下你的评论吧 !