DDR跑不到速率后续来了,相邻层串扰深度分析!

描述

高速先生成员:黄刚

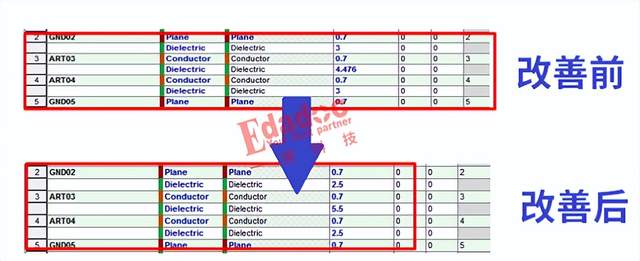

就在刚刚,雷豹把他对叠层的调整方式和改善后的仿真结果给师傅Chris看完后,Chris给雷豹点了个大大的赞,因为优化的方式其实不需要大改DDR的走线,只需要把相邻层的信号最大限度的拉开,同时为了保证叠层厚度不变,就需要把信号和参考的地平面相应的靠近。这个操作的好处是显而易见,信号与信号之间的距离变远的同时,信号与参考地平面的距离又变近了,串扰肯定就能够改善了啊!下面是雷豹想到的改善后的叠层方案。

信号与信号由之前的4.476mil拉大到了5.5mil,同时为了保持厚度不变,信号与地的距离从3mil减小到了2.5mil。这个时候会不会有粉丝问,为什么不再拉大一点呢,直接拉到6mil以上不更好了。呃,这个……只能回答你们,PCB设计是需要多种因素来权衡,拉到6mil的串扰肯定会更好,但是信号离地平面近了,线宽需要减小才能控到之前的阻抗,近到2mil压根就控不到阻抗了,因为线忒细了。

其实雷豹坦言,采取这个叠层调整的方案其实也主要是通过“凭感觉”来的,理论是知道的,就是信号之间远了,信号和地平面近了,电磁场在信号之间的交叉量就少了,因此串扰能够改善。但是改善了多少,能不能通过其他指标更清晰的量化出来呢,雷豹心里其实是打鼓的!

Chris看破不点破,决定亲自来接手这个案例后续的串扰分析。我们知道,去衡量任何信号质量的手段无非就两种,要么是在时域上判断,要么就是在频域上去分析。时域的话,雷豹已经在信号眼图上有对比过了,那么想继续分析这个串扰的改善的话,就有在频域上去做文章了。

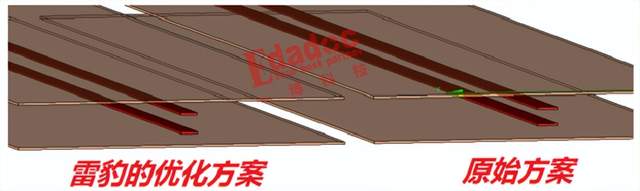

Chris对雷豹调整叠层前后的走线结构进行建模,利用cadence的3D clarity快速的建立了两种结构的模型,可以看到,雷豹的优化方案就是把信号间距拉远,信号与地间距拉近,同时减小一定的线宽来控制阻抗不变。

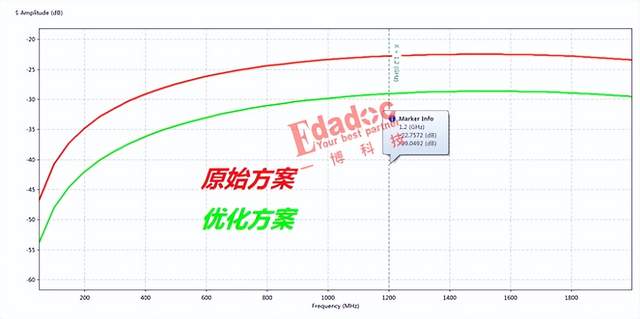

原始仿真模型版本中,我们把相邻层的走线长度定在1000mil,基本上和该案例的DDR走线的最大并行长度接近,使得这个仿真模型更贴近该案例的真实情况。

分别对两个模型进行仿真,仿真后得到两者的串扰参数的结果,Chris把它们摆在一起来看。

从对比结果可以看到,串扰在DDR运行的频率处从22db改善到29db,大家可不要小看这个7db的串扰改善,从db损耗反推回幅度的话,如果串扰源电压是1V的话,基本上22db是80mV的串扰幅度,29db只有35mV左右,改善还是非常的大的,有兴趣的粉丝后面可以自己算算哈!

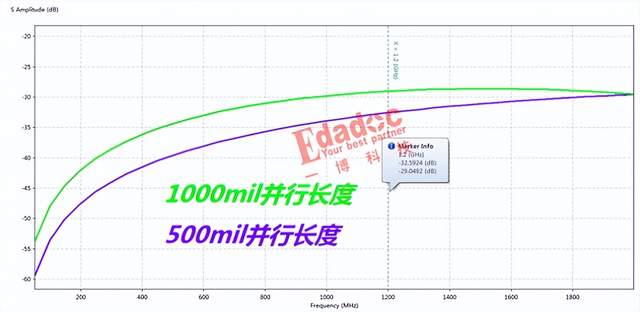

当然,在雷豹惊呼很厉害的时候,Chris突然问雷豹,那优化了叠层之后,还有没有什么办法通过走线的变化进一步优化串扰呢?此时雷豹看着Chris的仿真模型,同时脑中不停的翻滚曾经学过的串扰理论,duang的一声,有啦!目前仿真模型是信号线并行长度1000mil,如果能缩短到500mil呢,会不会使得串扰结果进一步变好呢?Chris满意的点了点头,进步很大的小伙子!只见Chris飞快的对模型上的信号走线缩短一半,只剩500mil的并行长度,然后再次进行仿真,结果令人满意,串扰量级又改善了3个多db!

的确,从串扰产生的理论出发去寻找改善串扰的方案,的确是比较好的解决问题的思路,于是雷豹在之前的叠层优化建议之外,还加上了一条,尽量减小相邻层并行的走线的长度,这下这个案例的改板设计就更保险了!正当雷豹开始暗爽的时候,突然Chris来了一句,那在这个case里,主控和DDR的布局位置都不变的时候,具体要怎么走线才能达到缩短并行长度的目标呢?雷豹刚开始楞了下,不过镇定下来思考片刻后,作为PCB设计出身然后转到我们高速先生团队的他还是想到了不少的办法实现了!

审核编辑:汤梓红

-

基于高速PCB串扰分析及其最小化2018-09-11 1198

-

几张图让你轻松理解DDR的串扰2019-09-05 2988

-

DDR跑不到速率,调整下PCB叠层就搞掂了?2023-06-02 812

-

DDR跑不到速率后续来了,相邻层串扰深度分析!2023-06-06 3053

-

pcb设计中的串扰—两传输线相邻太近2011-11-21 3667

-

高速差分过孔间的串扰 差分过孔间串扰的仿真分析2022-11-11 1664

全部0条评论

快来发表一下你的评论吧 !