如何用MOS设计分立式电平转换系统?

模拟技术

描述

★ SCD-1---分立式MOS电平转换 ★★★

引言:当传统设备与使用较小电平的新设备连接时,需要进行逻辑电平转换。对于像I2C这样的双向总线系统,这种电平转换器也必须是双向的,且不需要额外的方向控制信号。解决这个问题的最简单方法是用分立MOSFET在每条总线上搭建一个电平转换系统。

集成电路技术工艺限制了使用最大电源电压(工艺制程越高,电压越低),从而限制了数字I/O信号的逻辑电平。例如为了将这些低电压电路与现有的5V或者3.3V甚至1.8V设备连接,需要电平转换器。

- €1. 用于快速模式和标准模式I2C总线系统的双向电平转换器*

尽管分立式电平转换非常简单性,但这种解决方案不仅满足了无方向控制信号的双向电平切换的要求,而且将断电的母线部分与总线系统的其余部分隔离,保护“较低电压”侧免受来自“较高电压”侧的高电压尖峰。

双向电平转换器可用于标准模式(高达100kbit/s)或快速模式(高至400kbit/s)I2C总线系统。但它不适用于HS模式系统,HS模式和更高速率的场景需要使用专业的电平转换器。

- €2. 连接具有不同逻辑电平的设备*

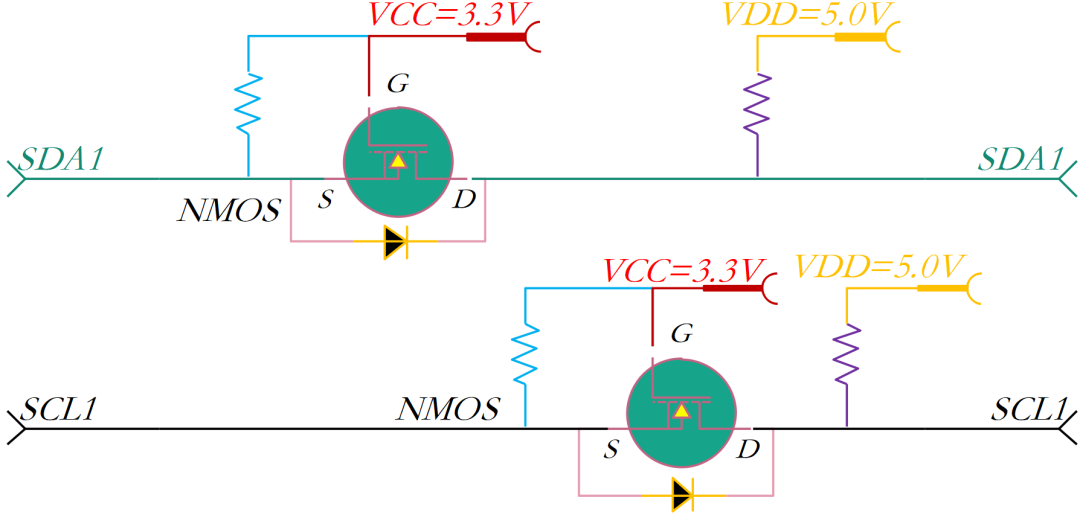

通过将上拉电阻器连接到电源电压线,不同的电压设备可以连接到同一总线。虽然这是最简单的解决方案,但较低电压的器件必须能耐受5V,这可能会使它们的制造成本更高。然而,通过使用双向电平转换器,可以互连I2C总线系统的两个部分,每个部分具有不同的电源电压和不同的逻辑电平。这种配置如图1-1所示。左侧“低压”部分有上拉电阻器和连接到3.3V电源电压的设备;右侧的“高压”部分有上拉电阻器和连接到5V电源电压的器件。每个部分的设备都具有具有电源电压相关逻辑输入电平和开路漏极输出配置的I/O。

每条总线的电平转换器是相同的,由一个分立的N沟道增强MOSFET组成;Q1用于串行数据线SDA,Q2用于串行时钟线SCL。栅极(G)连接到较低的电源电压VCC,源极(S)连接到“较低电压”部分的总线,漏极(D)连接到“较高电压”部分的总线。许多MOSFET的衬底与其源极内部连接,如果不是这样,则应进行外部连接。每个MOSFET在漏极和衬底之间都有一个集成二极管(n-p结)。

图1-1:连接I2C总线系统中两个不同电压段的双向电平转换器电路

当5V转3.3V时,5V发送5V高电平信号,MOS管截止,S极(3.3V)被电阻上拉为3.3V,当5V电路发送低电平时,MOS管导通,S极(3.3V)为低电平。

当3.3V转5V时,3.3V发送3.3V高电平信号,MOS管截止,D极(5V)被电阻上拉为5V,当3.3V电路发送低电平时,MOS管导通,D极(5V)为低电平。

- €3. 电平转换器的工作过程*

在电平转换器的操作过程中,应考虑以下三种状态:

第一种状态:没有任何设备正在拉下总线。“较低电压”部分的总线由其上拉电阻器Rp上拉至3.3V。MOSFET的栅极和源极均为3.3V,因此其VGS低于阈值电压,MOSFET不导通。这允许“较高电压”部分的总线被其上拉电阻器Rp上拉至5V。因此两个部分的总线均为高电平,但处于不同的电压值。

第二种状态:3.3V设备将总线下拉至低电平。MOSFET的源极也变为低,而栅极保持在3.3V。VGS上升到阈值以上,MOSFET开始导通。然后3.3V器件通过导电MOSFET将“较高电压”部分的总线下拉至低电平。因此两个部分的总线都变低至相同的电压电平。

第三种状态:5V设备将总线下拉至低电平。MOSFET“低电压”部分的漏极-衬底二极管被下拉,直到VGS超过阈值,MOSFET开始导通。然后,5V器件通过导电MOSFET将“低电压”部分的总线进一步拉低至低电平。因此两个部分的总线都变低至相同的电压值。

这三种状态表明,逻辑电平在总线系统的两个方向上传输,与驱动部分无关。状态一执行电平移位功能。状态二和状态三按照I2C总线规范的要求在两个部分的总线之间执行“有线and”的功能。

也可以施加除VCC为3.3V和VDD为5V以外的电源电压,例如VCC为2V,VDD为10V也是可行的。在正常操作中,D极上拉电平VDD必须等于或高于S极和G极上拉电平VCC(在接通/断开电源期间,允许VDD低于VCC)。

€4.分立式MOS电平转换器设计示例

*设计背景:*现有一个SOC的I2C电平是1.8V,需要连接到一个传感器,但是传感器的I2C接口电平是3.3V,请设计一个低成本的分立式双向MOS电平转换器。

*设计分析:*分立式电平转换器MOS选型需要考虑如下几点:

#1.成本考量,从低成本设计出发,建议使用NMOS

#2.导通阈值,一定要完全导通,以VGSTHmax为下限

#3.电平转换速率,估算选用的MOS可以支持到最大的开关速率。

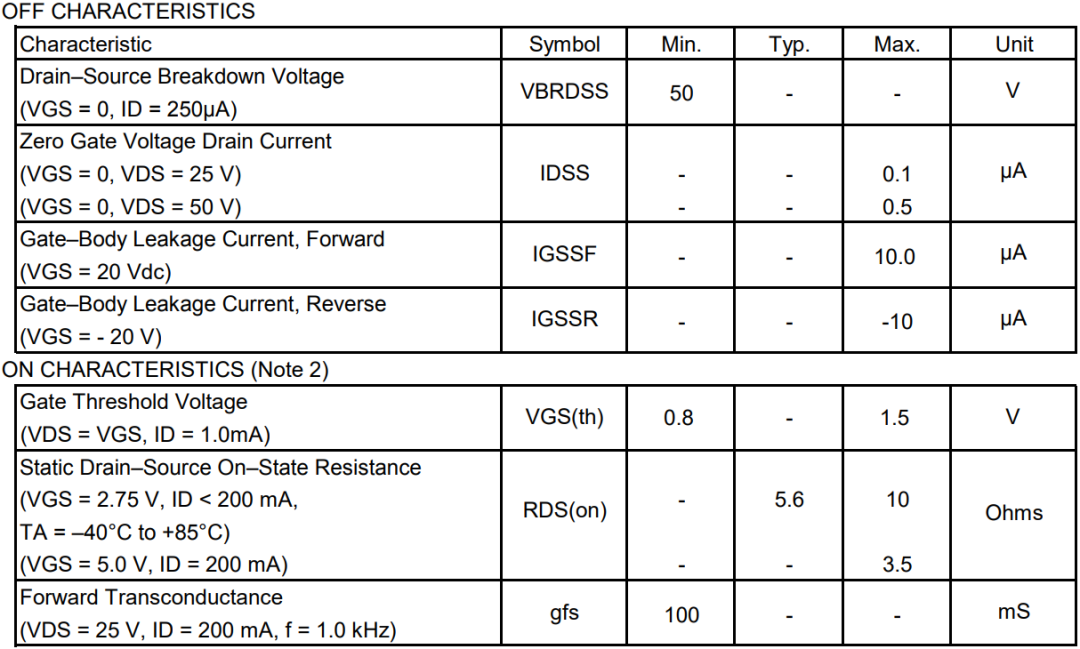

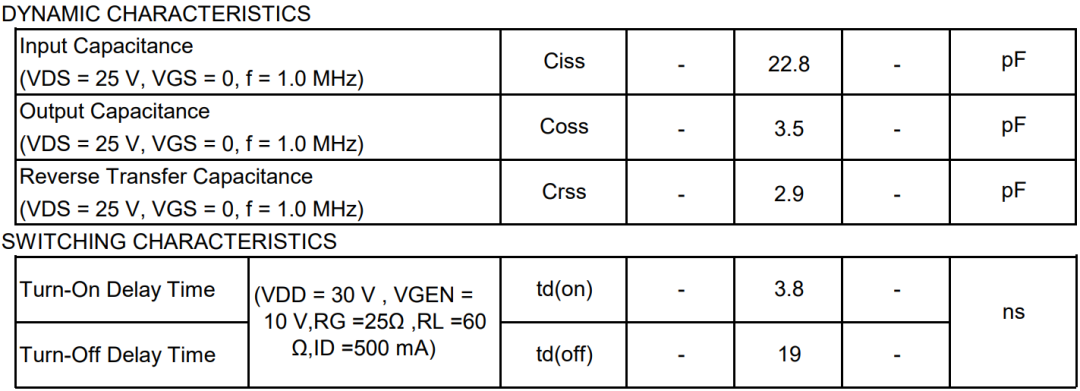

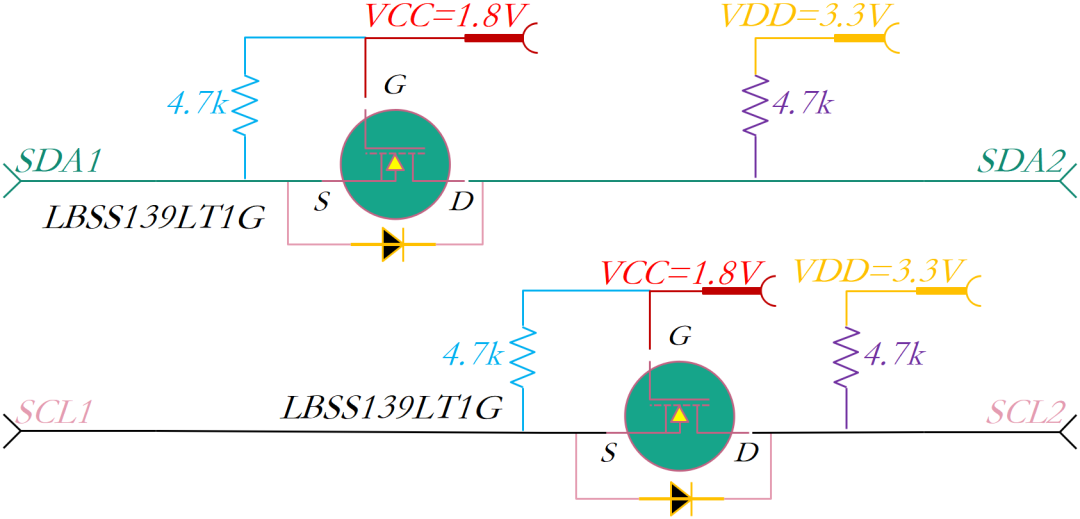

设计选型:从图1-1可以看出,1.8V在右,3.3V在左,那么NMOS的VGSTHmax一定要小于1.8V。四只上拉电阻遵从I2C的上拉电阻计算,我们选择LRC的LBSS139LT1G,图1-2和 图1-3 **为LBSS139LT1G的相关电气参数。

图1-2:LBSS139LT1G的静态参数

图1-3:LBSS139LT1G的动态参数

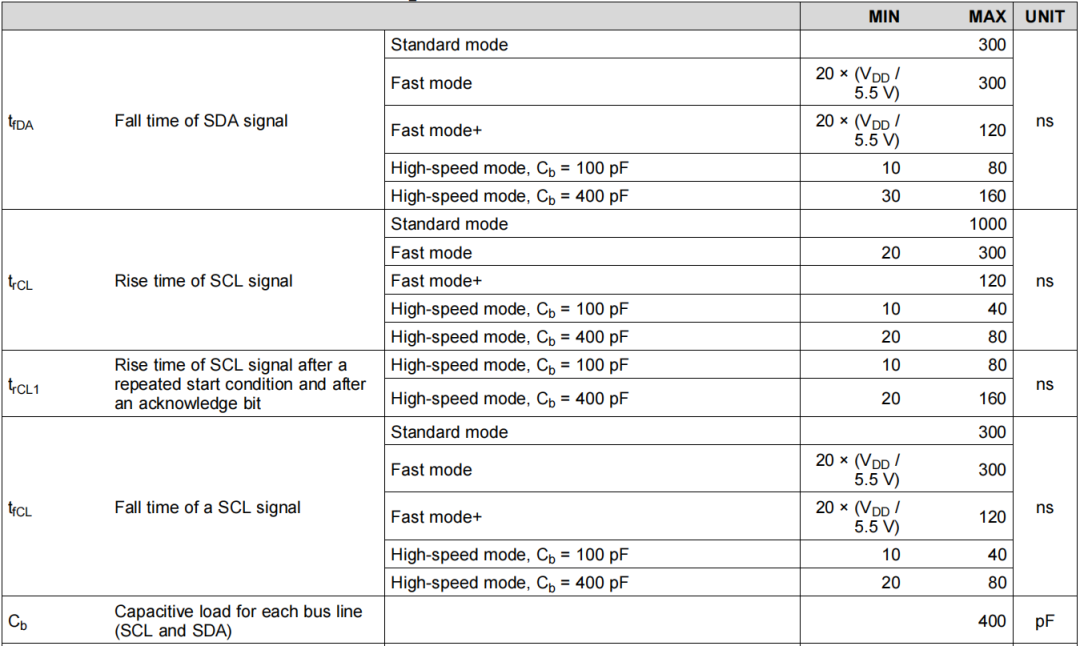

图1-4:标准I2C时序参数

*速率评估:*图1-3里面已经列出了Tdon和Tdoff,对比I2C的标准时序参数( 图1-4 )可知LBSS139LT1G能支持到的速率其实挺高的,但是考虑到线路额外增加的Cload,分立式MOS电平转换推荐使用在速率为标准模式(高达100kbit/s)或快速模式(高至400kbit/s)的I2C,不推荐使用在HS模式下,避免使用隐患。图1-5为设计的1.8v-3.3v双向I2C电平转换系统。

图1-5:1.8v-3.3v双向I2C电平转换

*** €5. 小结 ***

本节以I2C电平转换系统为导引,但实际上该简易电平转换系统不仅仅适用于I2C,也适用于低速率的SPI等等其它接口,甚至单个或多个IO电平转换。其简易的设计,可靠的性能,也是硬件设计中不可多得的降本增效方案。

-

PowerLab笔记:进行分立式设计的方法2018-09-20 1537

-

集成与分立式低电压电机驱动解决方案的主要差异2018-12-07 2741

-

支持多种汽车应用的微控制器分立式电源设计2018-12-28 1675

-

分立式逆变器的挑战2019-05-13 2107

-

请问如何利用ADIsimRF对零中频分立式发射机进行电平规划?2021-04-13 2282

-

如何进行分立式设计?2022-11-23 655

-

电源变换器集成式和分立式的作用特点2018-08-02 4443

-

基于IGBT的分立式三相逆变器的TIDA 00472设计2022-09-06 1048

-

PowerLab 笔记:如何进行分立式设计2022-11-07 928

-

分立式 LED 驱动器-AN107392023-02-09 582

-

建立FETching分立式放大器的提示2023-11-23 431

-

集成式与分立式开漏电平转换2024-08-28 437

-

取代分立式保护并优化PLC系统保护2024-08-29 601

-

如何使用分立式电流检测优化 PoE 系统2024-09-09 500

-

分立式整流器的整流原理2024-10-11 2341

全部0条评论

快来发表一下你的评论吧 !